| Скачать .docx |

Реферат: Разработка формирователя сигналов на однокристальном микропроцессоре

Министерство РФ по связи и информатизации

Поволжская государственная академия телекоммуникаций

и информатики

Кафедра “Вычислительная техника”

Сдана на проверку Допустить к защите

“___” _________2004г. “___” _________2004г.

“___” _________2004г.

КУРСОВАЯ РАБОТА

“Разработка формирователя сигналов на однокристальном микропроцессоре”.

Пояснительная записка

на 26 листах.

Студент группы 24 «О» Потапов В.А. № зачётной книжки 023465

Руководитель Куляс О.Л.

Самара. 2004г.

Рецензия

Содержание.

1. Задание на выполнение курсовой работы.

Необходимо разработать формирователь двух сигналов периодического цифрового четырехразрядного сигнала ![]() , имитирующего работу четырехразрядного двоичного счетчика с заданным модулем счета, и непериодического аналогового напряжения сложной формы

, имитирующего работу четырехразрядного двоичного счетчика с заданным модулем счета, и непериодического аналогового напряжения сложной формы ![]() , используя аппаратный и программно-аппаратный способ реализации.

, используя аппаратный и программно-аппаратный способ реализации.

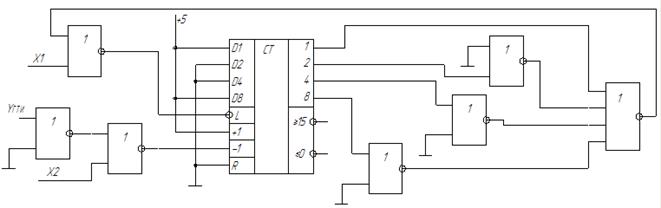

Обобщенная структурная схема формирователя реализованного аппаратным способом на «жесткой логике» представлена на рис.1.

Устройство состоит из генератора тактовых импульсов (ГТИ), счетчика импульсов (СТ), преобразователя кодов (ПК) и цифро-аналогового преобразователя (ЦАП).

Формирователь сигналов работает следующим образом: импульсы с выхода генератора с периодом следования ![]() поступают на 4-х разрядный счетчик, который с каждым импульсом изменяет свое состояние на единицу. На выходах счетчика формируются заданные последовательности четырехразрядных сигналов

поступают на 4-х разрядный счетчик, который с каждым импульсом изменяет свое состояние на единицу. На выходах счетчика формируются заданные последовательности четырехразрядных сигналов ![]() . Затем, с помощью преобразователя кодов, эти последовательности преобразуются в восьмиразрядные последовательности сигналов

. Затем, с помощью преобразователя кодов, эти последовательности преобразуются в восьмиразрядные последовательности сигналов ![]() , которые управляют работой ЦАП. С выхода ЦАП снимается пропорциональное входным восьмиразрядным последовательностям аналоговое напряжение заданной величины и формы

, которые управляют работой ЦАП. С выхода ЦАП снимается пропорциональное входным восьмиразрядным последовательностям аналоговое напряжение заданной величины и формы ![]() .

.

Дополнительные входы счетчика предназначены: ![]() – для установки начального состояния счетчика. При активном уровне

– для установки начального состояния счетчика. При активном уровне ![]() на выходах формирователя должны появиться сигналы, соответствующие

на выходах формирователя должны появиться сигналы, соответствующие ![]() и

и ![]() ;

;

![]() – для принудительной остановки работы. При активном уровне

– для принудительной остановки работы. При активном уровне ![]() формирователь должен приостановить работу до получения дальнейших инструкций.

формирователь должен приостановить работу до получения дальнейших инструкций.

2.1. Определение цифровых последовательностей на входах ЦАП.

Для того, чтобы ЦАП мог формировать аналоговые напряжения необходимой величины ![]() , на его цифровые входы необходимо подавать пропорциональные этим напряжениям двоичные коды

, на его цифровые входы необходимо подавать пропорциональные этим напряжениям двоичные коды ![]() . Для определения этих кодовых комбинаций найдём напряжение

. Для определения этих кодовых комбинаций найдём напряжение ![]() , соответствующее единице младшего значащего цифрового разряда на входе ЦАП, как:

, соответствующее единице младшего значащего цифрового разряда на входе ЦАП, как:

где ![]() и

и ![]() - минимальное и максимальное напряжения на выходе ЦАП, n

- разрядность используемого ЦАП.

- минимальное и максимальное напряжения на выходе ЦАП, n

- разрядность используемого ЦАП.

![]()

Значения цифрового кода ![]() вычисляются по формуле:

вычисляются по формуле:

где ![]() - целая часть числа а

.

- целая часть числа а

.

Второе слагаемое учитывает начальное смещение цифрового кода, так как последний является только положительным, а напряжение на выходе ЦАП может иметь различную полярность. Для заданных значений ![]() ,

, ![]() и

и ![]() его значение постоянно и равно 128.

его значение постоянно и равно 128.

Для определения цифровых последовательностей ![]() необходимо воспользоваться соотношением:

необходимо воспользоваться соотношением:

![]()

т.е. перевести значения цифрового кода ![]() в двоичную систему счисления.

в двоичную систему счисления.

Таким образом, таблица исходных данных будет иметь следующий вид:

| ABC

=512; логический базис или-не |

|||||

| i Порядковый номер кодовой комбинации |

M (i ) Значение кода счетчика DEC |

Q 4Q 3Q 2Q 1 Код счетчика, BIN |

U (i ) ,В напряжение на выходе ЦАП |

Y (i ) , знач. кода на входе ЦАП |

Y 8Y 7Y 6Y 5Y 4Y 3Y 2Y 1 код на входе ЦАП BIN |

| 0 |

8 |

1 0 0 1 |

0 |

109 |

0 1 1 0 1 1 0 1 |

| 1 |

7 |

1 0 0 0 |

-1 |

91 |

0 1 0 1 1 0 1 1 |

| 2 |

6 |

0 1 1 1 |

-2 |

73 |

0 1 0 0 1 0 0 1 |

| 3 |

7 |

0 1 1 0 |

-2,5 |

54 |

0 0 1 1 0 1 1 0 |

| 4 |

8 |

0 1 0 1 |

-3 |

64 |

0 1 0 0 0 0 0 0 |

| 5 |

9 |

0 1 0 0 |

-4 |

73 |

0 1 0 0 1 0 0 1 |

| 6 |

10 |

0 0 1 1 |

-4,5 |

82 |

0 1 0 1 0 0 1 0 |

| 7 |

11 |

0 0 1 0 |

-2 |

91 |

0 1 0 1 1 0 1 1 |

| 8 |

12 |

0 0 0 1 |

-2 |

100 |

0 1 1 0 0 1 0 0 |

| 9 |

13 |

0 0 0 0 |

-1 |

109 |

0 1 1 0 1 1 0 1 |

| 10 |

0 |

1 1 1 1 |

-0,5 |

118 |

0 1 1 1 0 1 1 0 |

Таблица 1. Исходные данные для проектирования

В соответствии с вариантом временная диаграмма напряжения на выходе ЦАП будет иметь следующий вид (рис.2):

![]()

2.2.Синтез преобразователя кода.

Согласно схеме, показанной на рис.1, восьмиразрядные кодовые комбинации Y (i ) формируются преобразователем кода из четырехразрядных кодовых комбинаций Q 4Q 3Q 2Q 1, получаемых на выходе счетчика. Таблица 1 связывает сигналы на входе преобразователя кода Q 4Q 3Q 2Q 1 с выходными сигналами Y 8Y 7Y 6Y 5Y 4Y 3Y 2Y 1 и является таблицей истинности КЦУ с четырьмя входами и восемью выходами.

В процессе синтеза преобразователя кода произведем:

1) минимизацию логических функций Y 1=f (Q 4,Q 3,Q 2,Q 1), Y 2=f (Q 4,Q 3,Q 2,Q 1), ... , Y 8=f (Q 4,Q 3,Q 2,Q 1) методом карт Карно, используя покрытие единиц или нулей карты. При этом учтём, что эти функции являются не полностью определенными.

2) преобразуем минимизированные логические выражения в базис ИЛИ-НЕ.

3) построим функциональную схемы преобразователя кодов, выбрав для реализации логических функции такие варианты, которые требуют минимального числа корпусов интегральных микросхем (ИМС) ТТЛ серий К155.

Выполним необходимые расчеты

![]()

![]()

![]()

| Q4 Q3 \ Q2 Q1 |

00 |

01 |

11 |

10 |

| 00 |

1 |

1 |

1 |

|

| 01 |

1 |

1 |

1 |

0 |

| 11 |

~ |

~ |

1 |

~ |

| 10 |

1 |

1 |

~ |

~ |

![]()

| Q4 Q3 \ Q2 Q1 |

00 |

01 |

11 |

10 |

|

|

1 |

1 |

0 |

0 |

| 01 |

0 |

0 |

0 |

1 |

| 11 |

~ |

~ |

1 |

~ |

| 10 |

0 |

1 |

~ |

~ |

![]()

| Q4 Q3 \ Q2 Q1 |

|

01 |

11 |

10 |

| 00 |

0 |

0 |

1 |

1 |

| 01 |

0 |

0 |

0 |

1 |

| 11 |

~ |

~ |

1 |

~ |

| 10 |

1 |

0 |

~ |

~ |

![]()

|

|

00 |

01 |

11 |

10 |

| 00 |

1 |

0 |

0 |

1 |

| 01 |

1 |

0 |

1 |

0 |

| 11 |

~ |

~ |

0 |

~ |

| 10 |

1 |

1 |

~ |

~ |

![]()

![]()

![]()

![]()

![]()

![]()

По полученным выражениям составим структурную схему преобразователя кода (Рис.3):

|

2.3. Синтез счётчика импульсов.

В качестве счётчика импульсов используем интегральную микросхему К555ИЕ7. Обозначение и функциональная схема синтезируемого счетчика показана на рис.4

|

|

|

|

Это четырехразрядный асинхронный реверсивный счётчик с возможностью предустановки. Модуль счета счетчика 16, т.е. при работе в режиме счета он последовательно переходит из одного состояния в другое начиная с состояния 010 =00002 и заканчивая состоянием 1510 == 11112 .

Выводы счетчика имеют следующее назначение:

Входы "D 1", "D 2", "D 4" и "D 8" предназначены для предварительной установки состояния счетчика. На эти выводы подается четырехразрядная кодовая комбинация, которую можно загрузить в счетчик.

Вход "L " – вход разрешения предустановки. При подаче логического "0" установленная на входах предустановки комбинация записывается в триггеры счетчика и появляется на выходах.

Входы "+1" и "-1" - суммирующий и вычитающий входы счетчика соответственно. Срабатывание счетчика происходит при положительном перепаде напряжения на одном из входов. При этом на неиспользуемый вход должен подаваться уровень логической "1".

Вход "R " - асинхронный вход сброса всех триггеров счетчика в состояние 0. Сброс осуществляется подачей логической "I".

Выходы "1", "2", "4", "8" - прямые выходы разрядов счетчика.

На выходах "≥15" и "≤0" – формируются сигналы логического "0" при достижении максимального и минимального состояний счетчика соответственно.

Напряжение питания счетчика +5 В, потребляемый ток 34 мА.

Максимальная тактовая частота 25 МГц, время установки кода счетчика около 40 нс.

Исходные данные для синтеза счетчика берем из таблицы 1. Для нашего варианта счетчик должен работать в режиме вычитания, иметь 11 состояний, начальное состояние счетчика М (0)=9, конечное состояние счетчика М (10)=15. Принцип синтеза счетчиков с произвольным модулем счета заключаются в исключении из работы "лишних" состояний. Для нашего варианта требуется исключить из работы 5 "лишних" состояний, что можно осуществить с помощью принудительной установки счетчика в начальное состояние М (0)=9 вместо состояния М (10+1)=14. Такую принудительную установку можно выполнить, если на входы предустановки подать код начального состояния счетчика, а в момент перехода счетчика в состояние М (10+1) сформировать сигнал разрешения предустановки. Сигнал разрешения предустановки формируется схемой предустановки, которая по сути является дешифратором числа 14.

Для синтеза схемы предустановки составим таблицу истинности ее работы, исходя из следующих предположений: логический 0, необходимый для разрешения предустановки, должен появляться на ее выходе только в момент времени, когда счетчик находится в состоянии М(10+1)=14. Это значит, что для любых других состояний счетчика на выходе схемы предустановки должна формироваться логическая 1. Таким образом, таблица истинности будет иметь вид таблицы 2.

| Входные сигналы |

Y ПУ |

|||

| Q 4 |

Q 3 |

Q 2 |

Q 1 |

|

| 1 |

1 |

1 |

0 |

0 |

| остальные комбинации |

1 |

|||

Таблица 2. Таблица истинности схемы предустановки

Записав по этой таблице логическое выражение в СКНФ, получим:

![]()

![]()

Временные диаграммы работы счетчика в этом режиме показаны на рис.5.

|

Согласно заданию, счетчик имеет два дополнительных входа: X 1- вход установки начального состояния и Х 2 - вход остановки счета. Это значит, что при подаче на входы X 1 и Х 2 активных логических уровней должна происходить установка начального состояния счетчика и остановка счета соответственно. Причем эти входы должны обладать наивысшим приоритетом по сравнению с другими. Поскольку установка начального состояния происходит с помощью механизма предустановки, то по сигналу X 1 должен формироваться сигнал разрешения предустановки, который следует подать на вход "L " счетчика. Его формирование происходит в схеме установки начального состояния. Остановку счета можно произвести, если прекратить подачу импульсов на счетный вход счетчика по сигналу Х 2. Это осуществляется в схеме остановки счета.

Произведем синтез схем установки начального состояния и остановки счета. При синтезе учитываем, что для нашего варианта активными уровнями сигналов X 1 и Х 2 являются уровни логической "1".

Составим схему установки начального состояния счетчика, для этого составим таблицу истинности установки начального состояния счетчика.

| X 1 |

Y ПУ |

YL |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

| 1 |

1 |

0 |

Запишем СДНФ:

![]()

перейдя в базис ИЛИ-НЕ, получим:

![]()

Составим схему остановки счёта, для этого составим таблицу истинности остановки счёта.

| X 2 |

Y ГТИ |

Y -1 |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

| 1 |

1 |

0 |

Запишем СДНФ:

![]()

перейдя в базис ИЛИ-НЕ, получим:

![]()

Составим принципиальную схему счетчика импульсов, объединив элементы счетчика. Так как схема предустановки заканчивается инвертором, а в схеме установки начального состояния Y ПУ инвертируется, то целесообразно убрать эти два инвертора. Покажем принципиальную схему счетчика импульсов на рис.6.

![]()

2.4. Выбор и расчет генератора тактовых импульсов.

В качестве ГТИ используем простой импульсный автогенератор на логических элементах ТТЛ серии. Принципиальная схема ГТИ изображена на рис.7:

![]()

Параметры R

1 и C

1 рассчитываются по формуле T

с

=2R

1C

1 . Пусть величина R

1=1кОм , тогда  Ф.

Ф.

В качестве ЦАП в проектируемом устройстве будем использовать интегральную микросхему К572ПА1. Это 10-разрядный перемножающий ЦАП, выполненный по КМОП технологии и отличающийся малой потребляемой мощностью в 0,1 Вт. Его основные динамические характеристики: время установления выходного напряжения t У =5мкс и дифференциальная нелинейность преобразования менее 0,8% от полной шкалы. Условное графическое обозначение ЦАП и схема его включения показана на рис.8.

![]()

Назначение выводов ИМС:

Х 1...Х 10 - цифровые входы , причем X 1 - вход младшего разряда.

U oп - вход для подключения источника опорного напряжения.

Y 1, Y 2 - аналоговые выходы ЦАП, которые являются токовыми.

R oc - вывод внутреннего резистора обратной связи.

U cc - вывод для подачи напряжения питания +5...17В.

OU - вывод для подключения общего провода.

Конструктивно ЦАП выполнен в 16 выводном корпусе типа DIP . В состав микросхемы входит резистивная прецизионная матрица R -2R , токовые ключи на МОП транзисторах и входные усилители-инверторы, которые обеспечивают управление ключами от стандартных уровней цифрового сигнала. Микросхема работает с прямым параллельным двоичным кодом, который подается на цифровые входы Х 10...Х 1 и реализует функцию перемножения опорного напряжения на цифровой код Х 10...Х 1 в четырех квадрантах. Благодаря тому, что коммутирующие ключи выполнены на МОП транзисторах, ЦАП допускает выбор опорного напряжения в широком диапазоне: -17...+17 В.

Поскольку выходы ЦАП токовые, то для преобразования тока в напряжение к выходам Y 1 и Y 2 подключаются операционные усилители DA 2, DA 3.

Операционный усилитель DA 2 обеспечивает суммирование токов, поступающих с коммутирующих ключей, находящихся в состоянии "1", a DA 3 - с ключей, находящихся в состоянии "0". В качестве операционных усилителей используем микросхему КР544УД2Г с незначительным смещением нуля и достаточно высоким быстродействием.

Благодаря использованию двух операционных усилителей эта схема формирует на выходе биполярное напряжение в пределах от -U oп до U oп. Связь между напряжением на выходе преобразователя, опорным напряжением U oп и цифровым кодом на входах Х 10...Х 1 определяется выражением:

Здесь n – количество разрядов ЦАП. В разрабатываемом устройстве, ЦАП К572ПА1 используется в восьмиразрядном включении, поэтому на два младших разряда XI и Х2 подаются постоянные логические уровни "0".

Для согласования входных уровней с выходами ТТЛ логики можно снизить напряжение питания U cc до величины 5 В.

Произведём выбор величины опорного напряжения, от которого зависит величина напряжений на выходе ЦАП. Для нашего варианта, для того, чтобы получить U min=-7 В и U max=7 В, значение U оп=-7 В. Выбранное опорное напряжение подается на вывод U оп DA 1 (см. рис.8).

Рассчитаем напряжение на выходе ЦАП для пяти значений цифрового кода и сведем результат в таблицу 3.

| Код на цифровых входах ЦАП |

Напряжение на выходе схемы, В |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

| 0 0 0 0 0 |

1 0 1 1 1 |

1 1 0 0 1 |

0 1 0 1 1 |

1 0 1 1 0 |

1 1 0 0 1 |

0 1 0 1 1 |

1 0 1 1 0 |

0 0 0 0 0 |

0 0 0 0 0 |

-1,039 -4,047 -3,008 -2,023 -0,547 |

Таблица 3. Зависимость напряжений на выходе ЦАП от цифрового кода на входе при восьмиразрядном включении

2.6. Составление полной принципиальной схемы формирователя.

Полная принципиальная схема составляется путем объединения всех разработанных выше узлов формирователя сигналов в единую схему, которая приведена в приложении 1.

2.7. Расчет задержки распространения сигналов и потребляемой мощности.

Подсчитаем время задержки распространения t З , выбрав в преобразователе кода наиболее длинную логическую цепочку.

Время задержки для ИМС К155 не более 25 нс

Время установки кода счетчика около 40 нс

Время установления выходного напряжения 5мкс

В разработанной в принципиальной схеме формирователя сигналов число ИМС типа К155, семь.

t З =25·10-9 ·7+40·10-9 +5·10-6 =5,215·10-6 с

Т.о. время задержки составляет не более 5,215мкс

Потребляемая мощность рассчитывается отдельно для каждого из источников питания: P +5 , P +15 , P -15 .

Найдем мощность для источника питания +5B.

Средняя мощность ИМС К155 20мВт

Мощность ИМС К555ИЕ7 равна: P К555ИЕ7 =I · U =5B·34·10-3 A=0,17Вт

Мощность ИМС К572ПА1 равна: P К572ПА1 =0,1Вт

P +5 =7·20мВт+0,17Вт+0,1Вт=0,41Вт

Найдем мощность для источника питания +15B и -15В.

P +15 = P -15 = P О У1 = P О У2 = P О У =260мВт

3.1. Разработка алгоритма формирования заданных сигналов и определение дополнительных исходных данных для проектирования.

Обобщенный алгоритм работы МП системы для варианта ABC =512 показан на рис.9.

![]()

Одним из простых способов программного формирования кодов счетчика M (i ) и кодов ЦАП Y (i ) является создание массива этих кодов в выбранной области ОЗУ или ПЗУ (блок 1). Поскольку создаваемые коды имеют разрядность в один байт, то они размещаются по четным адресам. После того, как эти коды будут сформированы в памяти, следует произвести инициализацию (установку режимов работы) портов ввода-вывода (блок 2). Дальнейшая задача сводится к выборке из ОЗУ нужных кодов и передаче их в соответствующие порты ввода-вывода (блоки 4...7). При этом нужно обеспечить выдачу сигналов Y (i ) с необходимыми временными интервалами Тс . Время Тс задает длительность одной ступеньки аналогового напряжения на выходе ЦАП. Это значит, что интервал времени между двумя соседними выводами кода ЦАП в порт должен быть равен Тс . При тактовой частоте fclk =5 МГц подсчитаем количество тактов, приходящееся на время Тс :

Такое большое количество тактов требует введения в алгоритм блока временной задержки (блок 3), который должен формировать нужный временной интервал Тс .

Кроме этого нужно предусмотреть анализ сигналов X 1 и Х 2, активный уровень которых должен приводить к появлению на выходе кода начального состояния М(0) или к остановке счета соответственно.

Составим таблицу исходных данных для дальнейшего проектирования.

Определим начальный адрес размещения массива кодов сигналов в ОЗУ ![]() , определяется соотношением

, определяется соотношением ![]() с округлением до большего четного числа

с округлением до большего четного числа ![]()

Определим значение диапазона адресов устройств ввода-вывода ![]() определяется по формуле

определяется по формуле ![]() с округлением до большего числа кратного восьми

с округлением до большего числа кратного восьми ![]()

после округления получим:

![]()

| ABC

=512; |

||||

| i Номер кодовой комбинации |

Адреса ячеек ОЗУ |

Содержимое ячеек ОЗУ |

Примечание |

|

| HEX |

BIN |

HEX |

||

| 0 |

00280 |

00001001 |

09 |

M(0) |

| 0 |

00282 |

01101101 |

6D |

Y(0) |

| 1 |

00284 |

00001000 |

08 |

M(1) |

| 1 |

00286 |

01011011 |

5B |

Y(1) |

| 2 |

00288 |

00000111 |

07 |

M(2) |

| 2 |

0028A |

01001001 |

49 |

Y(2) |

| 3 |

0028C |

00000110 |

06 |

M(3) |

| 3 |

0028E |

00110110 |

36 |

Y(3) |

| 4 |

00290 |

00000101 |

05 |

M(4) |

| 4 |

00292 |

01000000 |

40 |

Y(4) |

| 5 |

00294 |

00000100 |

04 |

M(5) |

| 5 |

00296 |

01001001 |

49 |

Y(5) |

| 6 |

00298 |

00000011 |

03 |

M(6) |

| 6 |

0029A |

01010010 |

52 |

Y(6) |

| 7 |

0029C |

00000010 |

02 |

M(7) |

| 7 |

0029E |

01011011 |

5B |

Y(7) |

| 8 |

002A0 |

00000001 |

01 |

M(8) |

| 8 |

002A2 |

01100100 |

64 |

Y(8) |

| 9 |

002A4 |

00000000 |

00 |

M(9) |

| 9 |

002A6 |

01101101 |

6D |

Y(9) |

| 10 |

002A8 |

00001111 |

15 |

M(10) |

| 10 |

002AA |

01110110 |

76 |

Y(10) |

Таблица 4. Исходные данные для проектирования

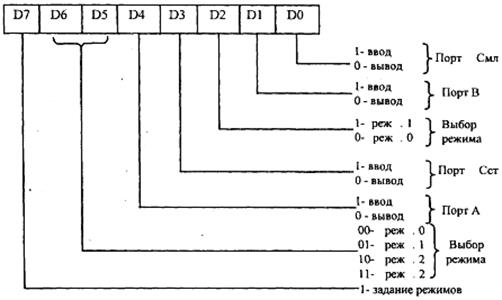

3.2. Определение управляющего слова.

|

Назначение разрядов управляющего слова показано на рис.10. С помощью этого рисунка определим управляющее слово, которое будет использоваться для инициализации ППИ. Для формирования заданных сигналов целесообразно использовать основной режим ввода-вывода – режим “0”.

![]()

Для нашего варианта, коды счетчика M (i ) = Q 4Q 3Q 2Q 1 выводятся в порт С , коды, управляющие работой ЦАП, Y (i ) = Y 8Y 7Y 6Y 5Y 4Y 3Y 2Y 1 выводятся в порт B , а порт A используется для ввода сигналов внешнего управления X 1 и Х 2. Следовательно, в соответствии с рис.10, разряды управляющего слова, используемого для установки режимов портов, будут такими:

| 1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

После перевода в шестнадцатеричный код получим управляющее слово 90H.

3.3. Определение адресов портов и синтез дешифратора адреса ППИ.

ППИ подключен к системной шине с использованием адресного пространства ввода-вывода и занимает в нем четыре четных адреса начиная с адреса ![]() . Для определения значений адресов портов ввода-вывода составим таблицу 5 в которой покажем состояние сигналов на системной шине адреса А

7...А

0 и адресуемый при этом порт. При составлении таблицы считаем, что разряд адреса А

0 не используется и всегда равен 0, разряды адреса А

2 и А

1 используются для выбора портов и регистра управляющего слова внутри ППИ.

. Для определения значений адресов портов ввода-вывода составим таблицу 5 в которой покажем состояние сигналов на системной шине адреса А

7...А

0 и адресуемый при этом порт. При составлении таблицы считаем, что разряд адреса А

0 не используется и всегда равен 0, разряды адреса А

2 и А

1 используются для выбора портов и регистра управляющего слова внутри ППИ.

| Состояние шины адреса |

Адресуемый порт |

Адрес порта HEX |

|||||||

| A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

||

| 0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

Порт A |

40 |

| 0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

Порт B |

42 |

| 0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

Порт C |

44 |

| 0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

РУС |

46 |

Таблица 5. Распределение адресов портов ввода-вывода

Как видно из составленной таблицы, порты ввода-вывода и регистр управляющего слова, которые входят в состав ППИ занимают 4 адреса в диапазоне 40Н...46Н. Поскольку в МП системе могут присутствовать УВВ с другими адресами, то для безошибочной работы нужных портов необходимо формировать сигналы их выбора. Эту функцию выполняет дешифратор адреса ППИ (ДШ ППИ), который формирует сигнал CS с уровнем логического 0, активизирующий БИС ППИ, только при установке на шине адресов, отведенных для данного устройства. Составим таблицу 6 истинности для дешифратора адреса ППИ.

| Входные сигналы |

CS Выходной сигнал |

||||||

| A 7 |

A 6 |

A 5 |

A 4 |

A 3 |

A 2 |

A 1 |

|

| 0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

| 0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

| 0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

| 0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

| все остальные комбинации |

1 |

||||||

Таблица 6. Таблица работы дешифратора адреса ППИ

Запишем логическое выражение для выходного сигнала, с учетом того, что входные сигналы A 2,A 1 являются фиктивными.

![]()

и перейдя в базис ИЛИ-НЕ, получим

![]()

Дешифратор адреса ППИ будет иметь вид как на рисунке 11.

3.4. Составление полной функциональной схемы формирователя на основе МП.

Все разработанные выше аппаратные части и выбранные устройства формирователя объединим в единую функциональную схему МП системы. На ней покажем в виде элементов принципиальной схемы ЦП К1810ВМ86, ППИ К580ВВ55, синтезированный ДШ ППИ и ЦАП. Остальные узлы схемы покажем в виде функциональных элементов. Данная схема изображена в приложении 2.

3.5. Разработка детального алгоритма работы микропроцессорной системы.

При разработке детального алгоритма (рис.12.) используется обобщенный алгоритм, показанный на рис.9. и исходные данные. При этом считаем, что массив кодов в ОЗУ (таблица 4) уже сформирован, следовательно, блок 1 обобщенного алгоритма в детальный алгоритм включать не будем.

Поскольку МП использует сегментацию памяти, адреса ячеек определяем в виде: PA =Seg : EA ,

где PA – двадцатибитовый полный (физический) адрес ячейки;

Seg – шестнадцатибитовый адрес сегмента (база, сегмент);

EA – шестнадцатибитовый адрес ячейки внутри сегмента (смещение).

Таким образом, для адресов (таблица 4), получим таблицу 7:

| Таблица 7. Адреса ячеек ОЗУ |

| PA |

Seg |

EA |

| 00280 |

0028 |

0000 |

| 00282 |

0028 |

0002 |

| 00284 |

0028 |

0004 |

| 00286 |

0028 |

0006 |

| 00288 |

0028 |

0008 |

| 0028A |

0028 |

000A |

| 0028C |

0028 |

000C |

| 0028E |

0028 |

000E |

| 00290 |

0028 |

0010 |

| 00292 |

0028 |

0012 |

| 00294 |

0028 |

0014 |

| 00296 |

0028 |

0016 |

| 00298 |

0028 |

0018 |

| 0029A |

0028 |

001A |

| 0029C |

0028 |

001C |

| 0029E |

0028 |

001E |

| 002A0 |

0028 |

0020 |

| 002A2 |

0028 |

0022 |

| 002A4 |

0028 |

0024 |

| 002A6 |

0028 |

0026 |

| 002A8 |

0028 |

0028 |

![]()

3.6. Разработка алгоритма подпрограммы задержки.

Для разработки алгоритма ПП задержки найдем число тактов задержки N З :

N З = N C -N Ф ,

где N Ф – число тактов между двумя соседними выводами кода ЦАП в порт без учета подпрограммы.

N З =10000-118=9882

ПП задержки реализуется путем включения в алгоритм подпрограммы холостых (пустых) команд NOP . Каждая команда NOP выполняется за 3 такта частота CLK . Последовательно можно включать любое количество холостых команд, но для экономии памяти и компактности целесообразно выполнять эти команды в цикле. Регистр МП СН используется как счетчик циклов и в него загружается число R , равное числу повторений цикла задержки. Поскольку СН восьмиразрядный регистр, то загружаемое в него число не должно быть больше 255(10) .

Найдем число повторений цикла задержки из соотношения:

![]() ,

,

где n – количество последовательно включенных команд NOP в блоке 24.

Для того чтобы R было не больше 255, выберем n =10, тогда R = 247(10) =F7h

![]()

3.7. Разработка программы работы микропроцессорной системы.

Текст программы представлен ниже:

| ; программа работы формирователя сигналов варианта 512 |

|

| ; упр. слово для настройки УВВ 90H |

|

| ; адрес текущего сегмента 0028H , адрес начального смещения 0000H |

|

| MOV AL, 90H |

;загрузить в AL управляющее слово |

| OUT AL, 46H |

;вывести управляющее слово в порт 46H |

| MOV AX, 0028H |

;адрес текущего сегмента данных |

| MOV DS, AX |

;загрузить в сегментный регистр DS |

| Label1: MOV CL, 0BH |

;загрузить в CL число циклов формирования |

| MOV BX,0000H |

;загрузить начальное смещение в регистр BX |

| Label2: CALL SUBR |

;вызвать подпрограмму задержки SUBR |

| MOV AL,[BX] |

;выбрать код M(i) из памяти |

| OUT AL,44H |

;вывести код M(i) в порт 44H |

| ADD BX,0002H |

;увеличить смещение на 2 |

| MOV AL,[BX] |

;выбрать код Y(i) из памяти |

| OUT AL,42H |

;вывести код Y(i) в порт 42H |

| ADD BX,0002H |

;увеличить смещение на 2 |

| Label3: IN AL,40H |

;ввести X2,X1 из порта 40H |

| RCR AL,1 |

;сдвинуть циклически на один разряд вправо |

| JC Label3 |

;перейти к метке Label3, если FC=1 (X2=1) |

| RCRAL,1 |

;сдвинуть циклически на один разряд вправо |

| JNC Label4 |

;перейти к метке Label4, если FC=0 (X2=0) |

| JMP Label1 |

;перейти к метке Label1 |

| Label4: DEC CL |

;уменьшить содержимое счетчика CL на 1 |

| JZ Label1 |

;перейти на метку Label1, если ZF=1 ((CL)=0) |

| JMP Label2 |

;перейти на метку Label2 |

| ; подпрограмма временной задержки |

|

| SUBR: MOV CH, F7H |

;загрузить в CН число циклов задержки R =F7H |

| Label5: NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| NOP |

;холостая команда |

| DEC CH |

;уменьшить содержимое счетчика CН на 1 |

| JNZ Label5 |

;перейти на метку Label5, если CН не пуст (ZF=0) |

| RET |

;возврат из подпрограммы |

Список литературы

1. Методические указания к курсовой работе по дисциплине «ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА». – Самара 2000.

2. Цифровая и вычислительная техника: Учебник для вузов/ Э.В. Евреинов, Ю.Т. Бутыльский, И.А. Мамзелев и др.; под ред. Э.В. Евреинова. – М.: Радио и связь, 1991.

3. Шило В.Л. Популярные цифровые микросхемы: справочник. – М.: Металлургия, 1987.

00

00 00

00 Q4 Q3 \ Q2 Q1

Q4 Q3 \ Q2 Q1