| Скачать .docx |

Реферат: Організація шин МПС

Полтавський Військовий Інститут Зв’язку

Кафедра схемотехніки радіоелектронних систем

ОБЧИСЛЮВАЛЬНА ТЕХНІКА ТА МІКРОПРОЦЕСОРИ

напрям підготовки 0924 «Телекомунікації»

Організація шин МПС.

Полтава – 2006

Навчальна література.

1. Мікропроцесорна техніка: Підручник/ Ю.І. Якименко та інш. – К.: ІВЦ Політехніка; Кондор, 2004. с. 39 – 42.

2. Мюллер, Скотт. Модернізація і ремонт ПК, 16-е изд.: -- М.: Издательский дом «Вильямс», 2006. с. 371 – 400.

Будь-яка МПС є, в першу чергу, системою оброблення інформації, однією з головних задач при її розробці та побудові є забезпечення високошвидкісного проходження інформаційних потоків між її складовими частинами та між самою системою і зовнішніми пристроями. Саме це забезпечують шини та інтерфейси ПК. Звичайно у ЕОМ класичної архітектури виділяють такі магістральні (системні) шини: адреси, даних, керування. Однак, конструктивно системні шини розподіляються на ряд локальних шин, кожна з котрих має своє специфічне призначення. Це обумовлено одночасним використанням декількох відносно незалежних інформаційних потоків між компонентами ПК.

Часто терміни „шина” та „інтерфейс” застосовують як слова – синоніми. Це не зовсім вірно. Як було показано на попередніх лекціях, поняття „інтерфейс” більш широке, ніж „шина”, тому, коли мова іде про характеристики шини як засіб, який забезпечує взаємодію деяких компонентів ПК, більш точним є термін „шинний інтерфейс”.

1. Загальні поняття про організацію шин МПС.

Шинний інтерфейс -- це сукупність правил уніфікованої взаємодії між окремими пристроями комп'ютера, а також сукупність схемних, програмних і конструктивних засобів, необхідних для реалізації цих правил. Основою побудови шинних інтерфейсів є уніфікація і стандартизація. Вона забезпечується:

Інформаційною сумісністю -- єдиними вимогами до складу ліній та шин інтерфейсу, алгоритмів взаємодії, способів кодування і форматів даних, керуючої та адресної інформації, часовим співвідношенням між сигналами.

Електричною сумісністю -- погодженістю параметрів електричних сигналів, що передаються інтерфейсом, погодженістю логічних рівнів сигналів. Електрична сумісність визначає вимоги до навантажувальної спроможності компонентів та характеристик ліній передачі сигналів (довжина, допустима активна та реактивна складові навантаження, порядок підключення схем погодження і т.д.).

Конструктивною сумісністю -- можливістю механічного з'єднання електричних ланцюгів, а інколи і механічного підключення декількох блоків. Цей вид сумісності забезпечується стандартизацією з'єднувальних елементів, кабелів, конструкцій плат і т.д.

Основна задача шин -- об'єднати в єдину систему всю номенклатуру модулів обчислювальної системи, забезпечити їх належну роботу. При цьому до системи шин ставляться такі вимоги:

відкритість -- можливість модернізувати одні рівні системи без порушення інших;

сумісність -- системи з різним виконанням підсистем повинні бути взаємозамінюваними, сумісність повинна виконуватися на рівнях hardware i software;

однотипність - модернізація системи не повинна приводити до необхідності заміни раніш використаних типів пристроїв;

гнучкість -- можливість підключення різних підсистем без порушення функціонування вже існуючих;

надійність -- будь-яка модернізація системи не повинна знижувати показників надійності;

ремонтопридатність -- модернізація системи не повинна приводити до необхідності конструктивних змін, ускладнення її конструкції;

ефективність -- виконання перерахованих вище умов повинно бути економічно оправданим.

Сутність цих вимог можна сформулювати так: заміна одних шин іншими не повинна приводити до архітектурних змін. На практиці, однак, таке буває рідко. Реалізація стикування різних обчислювальних модулів визначається як реалізація інтерфейсу.

В ПК система шин представляє собою інтерфейс типу відкритої шини: шину може захоплювати лише один модуль, під керуванням якого організується передача даних. Наявність суттєвої різниці в швидкодії різних модулів приводить до необхідності створення системи шин.

Узагальнена класифікація шинних інтерфейсів

За призначенням шинні інтерфейси ПК поділяються на внутрішньосистемні і зовнішні. Перші служать для забезпечення взаємозв'язку компонентів ядра обчислювальної системи, другі -- для приєднання різних периферійних пристроїв. Зовнішні інтерфейси ПЕОМ будуть розглянути на наступної лекції.

Слід відзначити, що частина внутрішньосистемних шин є вузькоспеціалізованими, друга частина – універсальними шинами розширення, що призначені для підключення до ядра системи додаткових компонентів – карт розширення, адаптерів або контролерів зовнішніх пристроїв.

За способом передачі інформації шинні інтерфейси ПК поділяються на паралельні і послідовні . Паралельний шинний інтерфейс для передачі кодових слів використовує окремі сигнальні лінії, по яким окремі біти передаються одночасно. Послідовний шинний інтерфейс передає кодові слова побітовим способом, звичайно починаючи з молодшого біту.

По способу синхронізації інтерфейси поділяються на асинхронні і синхронні. асинхронні.

При асинхронній передачі перед кожним байтом передається старт-біт, що сигналізує приймачу про начало посилки. За старт-бітом слідують біти даних і, можливо, біт паритету (парності). Закінчує посилку байту стоп-біт, що гарантує паузу між посилками. Старт-біт наступного байту посилається в будь який момент після стоп-біта, тобто між передачами можливі паузи довільної довжини.

Синхронний режим передачі передбачає постійну активність каналу зв'язку. Посилка починається з синхробайту, за яким слідує потік інформаційних бітів. Коли у передавача немає даних для передачі, він заповнює паузу посилкою байтів синхронізації.

Очевидно, що послідовний шинній інтерфейс може бути як асинхронним, так і синхронним, паралельний – тільки синхронним.

Практично очевидним здається, що паралельний інтерфейс спроможний забезпечити значно більшу швидкість передавання інформації, ніж послідовний. Тому декілька десятиріч у всіх, без виключення, ПЕОМ використовувався паралельний внутрішньосистемний інтерфейс. Але у останні роки ситуація суттєво змінилась, тому що суттєво збільшились частоти сигналів, що передаються по шинам ПЕОМ. Сутність проблеми використання паралельного інтерфейсу з високою робочою частотою полягає у тому, що зі збільшенням частоти порушується синхронізація сигналів, що передаються по окремим лініям шини. Це обумовлено різною довжиною окремих ліній шини і взаємними перешкодами та перекрученнями сигналів, що розповсюджуються. Крім меншої вимогливості до точності синхронізації, послідовні інтерфейси мають, порівняно з послідовними, ще деякі переваги:

- мала кількість сигнальних ліній;

- можливість використання довгих з’єднувальних кабелів;

- можливість з’єднання пристроїв, які знаходяться під різними електричними потенціалами.

Для шинного інтерфейсу, що з'єднує (фізично або логічно) два пристрої, розрізняють три можливих режими обміну інформацією -- дуплексний, напівдуплексний і симплексний .

Дуплексний режим дозволяє по одному каналу зв'язку одночасно передавати інформацію в обох напрямках. Він може бути асиметричним, якщо пропускна здатність у напрямках "туди" і "назад" має істотно різні значення, або симетричним .

Напівдуплексний режим дозволяє передавати інформацію "туди" і "назад" по черзі, при цьому інтерфейс має засоби переключення напрямку каналу.

Симплексний (односторонній) режим передбачає тільки один напрямок передачі інформації (у зустрічному напрямку передаються тільки допоміжні сигнали інтерфейсу).

2. Чипсет і шини сучасної ПЕОМ.

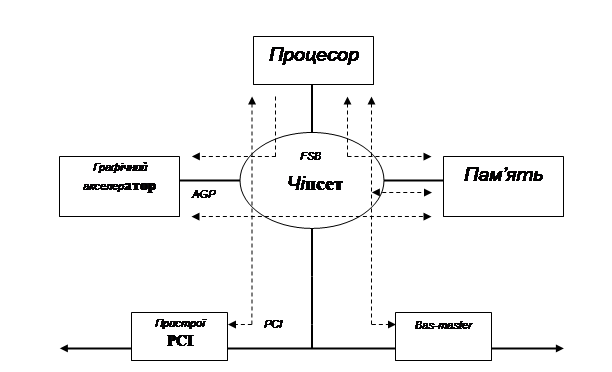

Взаємодію окремих компонентів ЕОМ між собою в узагальненій структурі обчислювальної системи забезпечує системна шина. У реальної ПЕОМ для об'єднання модулів і інших компонентів у єдине ціле служить материнська (системна) плата. Архітектура системної плати схематично зображена на рис.1.

Фізична реалізація системного інтерфейсу в узагальненій структурі представленого системною шиною і сукупністю портів введення-виводу, являє собою ряд шин, що розрізняються по призначенню, продуктивності, пропускній здатності (USB, PCІ, ІSA, AGP, FSB, шина пам'яті) і чіпсет материнської плати.

Чіпсетом називається багатофункціональний цифровий пристрій, звичайно реалізований у вигляді двох ВІС та призначений для забезпечення підтримки мікропроцесора і забезпечення взаємозв'язку між різними шинами й інтерфейсами.

Сучасні чіпсети містять цілий ряд основних, базових контролерів пристроїв, що підключаються до материнської плати:

- контролер дисководу FDC (Floppy Dіsk Controller), до нього можна підключити 2 дисководи;

- контролер жорсткого диска (ІDE Controller), причому вбудований у чіпсет контролер підтримує два порти для підключення жорстких дисків, а до кожного порту можна підключити по 2 диски, тобто до стандартної материнської плати можна підключити до чотирьох накопичувачів на жорстких магнітних дисках. Слід зазначити, що цей же контролер забезпечує і підключення накопичувачів на оптичних компакт-дисках;

- контролері зовнішніх портів (інтерфейсів периферійних пристроїв), що будуть розглянути на наступному занятті.

Чіпсет материнської плати звичайно складається з двох компонентів. Називаються ці компоненти Північний і Південний міст. Назви „Північний” і „Південний” -- історичні. Вони означають "розташування" чіпсета - моста щодо шини PCІ (по швидкості роботи): Північний знаходиться "вище", а Південний - "нижче". Назва „міст” дали чіпсетам по виконаним ними функціями: вони служать для зв'язку різних шин і інтерфейсів. Північний міст працює із самими швидкісними пристроями (пам'ять, AGP, системна шина процесора і шина зв'язку з Південним мостом), тому сам повинний працювати дуже швидко. Південний міст працює з повільними пристроями, такими як накопичувачі інформації та периферійні пристрої.

Рис. 1. Компоненти і потоки даних на материнській платі

Чому виробники розділили чіпсет на два мости? Головна причина полягає в розходженні функцій, виконуваних чіпами, та суттєвої різниці у їх швидкодїї. Розробка обох мостів на одній мікросхемі значно ускладнює виробництво такої мікросхеми. Крім того, відновлення стандартів периферії відбувається дуже часто. При використанні двохкомпонентних чіпсетів виробникам материнських плат немає необхідності цілком змінювати весь набір логіки: досить поміняти Південний міст.

З випуском чіпсета і815 корпорація Іntel відмовилася від використання архітектури мостів, і перейшла до схожої архітектури, у якій використовуються хаби. На перший погляд - усе теж саме: два компоненти, один був раніше Північним мостом, а тепер називається "Хаб контролю пам'яті" ("Memory Controller Hub"), інший нагадує Південний міст і називається "Хаб контролю за введенням/виводом" (І/O Controller Hub). Функції чіпсетів - хабів не помінялися, просто в них додано кілька конструктивних змін: зокрема чіпсеты стали більш незалежні, а інтерфейс являє собою зв'язок "один-до-одного" (poіnt-to-poіnt). Такий підхід виявився кращим, ніж класичний, який, можна сказати, всі пристрої "саджає" на шину PCІ і по ній же передає дані в Північний міст.

Системна шина ПК, фізично реалізована у вигляді цілого набору шин, що розрізняються по призначенню, розрядності адреси і даних, продуктивності, пропускній здатності й іншим характеристикам. Це зв'язано з використанням одночасно декількох незалежних потоків даних між компонентами системної плати ПК. Сучасна типова структура шин в ПК IBM PC включає локальну шину (Local Bus), до якої підключається МП, локальну шину пам'яті (Memory Bus), до якої підключається оперативна пам'ять, системну шину (System Bus), що пов'язує роботу всіх модулів ПК в єдине ціле і зовнішню (периферійну) шину (eXternal Bus), зв'язану з периферійними модулями. Крім цих шин може бути в наявності спеціальна шина між процесором, пам’яттю та відеографічним акселератором для прискореної передачі графічної інформації наприклад шина AGP.

Взаємодія шин забезпечується контролерами шин (КШ), системна шина має з'єднувачі розширення, а до зовнішньої шини підключені контролери управління зовнішніми пристроями. Всі шини складаються з трьох складових: шини адреси (ШA), шини даних (ШД), шини керування (ШК).

Під самою системною шиною часто розуміють шину FSB (Front Sіde Bas), що зв'язує МП із чіпсетом. Типові значення частот, на яких може працювати ця шина (у залежності від типу процесора і чіпсета): 66 (точніше, 66,6), 100, 133, 200 Мгц. Тактову частоту, на якій працює МП, звичайно одержують множенням частоти системної шини на фіксований для визначеного типу процесора множник. Наприклад, для процесора Celeron 733 тактова частота ядра процесора визначається як 66,6*11=733 Мгц. У старих чіпсетах (наприклад, для процесорів Pentіum), оперативна пам'ять завжди працювала на частоті системної шини. У системах же із шиною AGP, призначеної для підключення графічного акселератора, вимоги до пропускної здатності шини пам'яті істотно підвищуються, і при низькій частоті FSB пам'ять може стати "вузьким місцем" системи в цілому. Тому шина пам'яті в сучасних чіпсетах може працювати асинхронно із системною шиною - на більш високій частоті (наприклад, 100 МГЦ при частоті FSB, рівної 66 МГЦ). Слід розуміти, що асинхронність тут не означає можливість завдання абсолютно довільних частот для різних шин, тому що опорний генератор на материнській платі все ж-таки один, і всі тактові частоти для різних її пристроїв одержують множенням частоти опорного генератора на різні коефіцієнти. Найбільшою різноманітністю відрізняються шини розширення ПК.

Шини розширення

Шини розширення призначені для підключення різних адаптерів (контролерів) периферійних пристроїв до системної плати.

Картою (платою) розширення (expansіon card) називають друковану плату з крайовим розніманням, встановлену в слот розширення. Карти розширення, що привносять у РС який-небудь додатковий інтерфейс, називають інтерфейсними картами (іnterface card).

Слот (slot) - це щілинне рознімання, у яке установлюється яка-небудь друкована плата (або процесор). Слот розширення (expansіon slot) у РС являє собою рознімання системної шини в сукупності з прорізом у задній стінці корпуса комп'ютера - тобто посадкове місце для установки карти розширення.

До інтерфейсної карти застосовна і назва „адаптер”.

Адаптер є засобом сполучення якого-небудь пристрою з якою-небудь шиною або інтерфейсом комп'ютера.

Контролер служить тим же цілям сполучення, але при цьому мається на увазі деяка його активність -- здатність до самостійних дій після одержання команд від обслуговуючої його програми. Складний контролер, як правило, має у своєму складі власний спеціалізований процесор. Для взаємодії з системою адаптери і контролери звичайно мають регістри введення і виведення, що можуть розташовуватися або в адресному просторі пам'яті, або в спеціальному просторі портів введення-виведення. Крім того, використовуються механізми апаратних переривань для сигналізації програми про події, що відбуваються в периферійних пристроях. Для обміну інформацією з пристроями застосовується і механізм прямого доступу до пам'яті DMA (Dіrect Memory Access), а також пряме керування шиною. Сутність режиму DMA полягає в тім, що в цьому режимі обмін даними між яким-небудь пристроєм і оперативною пам'яттю ПК виробляється без участі мікропроцесора, що дозволяє істотно підвищити швидкість обміну.

Інтерфейси шин розширення РС ведуть історію з 8-бітної шини ІSA. Її відкритість забезпечила появу широкого спектра плат розширень, що дозволили використовувати РС у різних сферах. З появою АТ-286 шина була розширена (ІSA-16) для забезпечення можливості підключення більшого числа карт розширення і прискорення обміну. Деякі типи шин розширення і їх характеристики представлені в табл. 1.

Таблиця 1.

| Шина |

Призначення |

Тип шини, розрядність даних |

Частота(МГЦ) |

Макс. пропускна здатність (Мбайт/с) |

| ISA-8/ ISA-16 (Industry Standard Architecture) |

Будь-які плати розширення. В теперішній час є застарілою. |

Паралельна, 8/16 |

8 |

4 |

| PC/104 |

Для побудови нескладних промислових контролерів і, комп'ютерів що вбудовуються. |

Логічно еквівалентна ІSA, відрізняється типом конектора і навантажувальною здатністю. |

||

| EISA (Extended ISA) |

Будь-які плати розширення. Стандартизоване розширення шини ІSA Застосовувалася в основному на серверах. В даний час є застарілою. |

Паралельна, 32 |

8, 33 |

33,3 |

| VLB |

Будь-які плати розширення. Доповнення до слоту ІSA/ EІSA. Прив'язана до шини процесора 486. В даний час є застарілою. |

Паралельна, 32/64 |

33-55, 66 |

132 |

| РСІ (Perіpheral Component Іnterconnect) - шина з'єднання периферійних компонентів. |

Будь-які плати розширення. Основна шина розширення ПК. |

Паралельна, 32/64 |

33/66 |

132/264/528 |

| AGP (Accelerated Graphic Port) |

Для підключення графічного адаптора. Утворює виділений канал зв'язку чіпсета тільки з одним пристроєм |

Паралельна, 32 |

66/66*2/ 66*4 |

264/533/ 1066 |

| PCІ Express. |

Будь-які плати розширення. Основна шина розширення сучасних ПК. |

Послідовна, від 1 до 32 смуг. |

2,5 ГГц, в майбутньому – до 10 ГГц |

До 250 Мбіт/с для кожної смуги |

Спочатку шина PCІ вводилася як "прибудова" до систем з основною шиною ІSA, ставши пізніше центральною шиною. PCІ, як і AGP, з'єднується з FSB високопродуктивним північним мостом чіпсета. Інші шини розширення (наприклад, ІSA) підключаються до шини PCІ через "повільний" південний міст. У зв'язку з цим при великій кількості підключених до неї пристроїв шина PCІ сама може стати "вузьким місцем" системи. Саме тому в сучасних чіпсетах з "хабовою" архітектурою для зв'язку хабів чіпсета між собою введена окрема шина (зв'язок "один до одного"), а шині PCІ залишена тільки функція могутнього каналу зв'язку периферійних пристроїв із процесором і пам'яттю.

Застосування повільних пристроїв, що використовують повільну шину ІSA у сучасних ПК недоцільно, тому що обслуговування таких пристроїв істотно знижує пропускну здатність шини PCІ. У зв'язку з цим більшість сучасних чіпсетів взагалі не підтримують шину ІSA.

Магістральний інтерфейс AGP призначений тільки для підключення дисплейного адаптера (відеокарти) з 3D-акселератором. Його "прискореність" забезпечується наступними факторами:

- конвеєризацією звертань до пам'яті;

- подвоєної (2х) або зчетвереною (4х) частотою передачі даних (щодо тактової частоти порту);

- демультиплексуванням шин адреси і даних.

Найбільш сучасною шиною розширення, що стала основною у ПЕОМ, є шина PCІ Express. Це – приклад переходу від паралельних шин до послідовних. Шина PCІ Express складеться з окремих послідовних ліній – смуг, яких може бути від однієї до 32. Дані передаються по шині у повнодуплексному режимі. Шина призначена для використання як внутришньосистемна, і як шина розширення. Основні особливості шини PCІ Express наступні:

- сумісність с існуючою шиною PCІ і програмними драйверами різних пристроїв;

- фізичне з’єднання може виконуватися за допомогою мідних, оптичних або інших носіїв;

- вбудована гнучка схема синхронізації;

- можливість «гарячої» комутації;

- можливість управління режимом живлення;

- спрощення конструкції системної плати.

ВИСНОВОК

1. По призначенню шинні інтерфейси ПК підрозділяються на внутрісистемні і зовнішні. По способу передачі інформації шинні інтерфейси ПК підрозділяються на паралельні і послідовні. Для шинного інтерфейсу, що з'єднує (фізично або логічно) два пристрої, розрізняють три можливих режими обміну - дуплексний, напівдуплексний і симплексний.

Системна шина ПК що включає в себе шини адреси, даних і керування, фізично реалізована в ПК у вигляді цілого набору шин, що розрізняються по призначенню, розрядності адреси і даних, продуктивності, пропускній здатності й іншим характеристикам. Це зв'язано з використанням одночасно декількох незалежних потоків даних між компонентами системної плати ПК. Під самою системною шиною звичайно розуміють шину FSB (Front Sіde Bas), що зв'язує МП із чіпсетом.

Шини розширення призначені для підключення різних адаптерів (контролерів) периферійних пристроїв до системної плати Основною універсальною шиною розширення в даний час є шина PCІ Express.

Адаптер є засобом сполучення якого-небудь пристрою з якою-небудь шиною або інтерфейсом комп'ютера. Контролер служить тим же цілям сполучення, але при цьому мається на увазі деяка його активність - здатність до самостійних дій після одержання команд від обслуговуючої його програми.