| Скачать .docx |

Реферат: Проектирование цифрового автомата

Министерство образования Российской Федерации

Российский химико-технологический университет им. Д.И. Менделеева

Новомосковский институт

Проектирование цифрового автомата

Методические указания к курсовой работе

Под редакцией В.И. Воробьева

Новомосковск 2004

УДК 681.322

ББК 32.973

П 791

Рецензенты:

кандидат технических наук, доцент кафедры АПП

В.З. Магергут (НИ РХТУ им. Д.И. Менделеева)

кандидат технических наук, доцент кафедры Электротехника

Е.Б. Колесников (НИ РХТУ им. Д.И. Менделеева)

Составитель: В.С. Прохоров

П791 Проектирование цифрового автомата: Методические указания к курсовой работе / Под редакцией В.И. Воробьева; РХТУ им. Д.И. Менделеева, Новомосковский ин-т; Сост.: В.С. Прохоров. Новомосковск, 2001. - 24 с.

Предлагаются индивидуальные задания, даются методические указания и пример выполнения курсовой работы по курсу "Схемотехника" для студентов специальности “Автоматизированные системы обработки информации и управления”.

Ил.8. Табл.11. Библиогр.: 3 назв.

УДК 681.322

ББК 32.973

© Новомосковский институт

РХТУ им. Д.И. Менделеева, 2001

Содержание

Введение. 4

1. Последовательность выполнения задания и рекомендации по проектированию цифрового автомата. 5

2. Задание к курсовому проектированию.. 21

Библиографический список. 25

Введение

Курсовая работа является итоговой работой студентов по изучению курса "Схемотехника". Конечной целью изучения курса является освоение студентами самостоятельного проектирования несложных дискретных устройств (цифрового автомата), для того, чтобы в дальнейшем успешно эксплуатировать более сложные, серийно выпускаемые микроконтроллеры, а также ремонтировать и модернизовать персональные компьютеры.

Для облегчения курсового проектирования в этом методическом пособии рассматривается сначала порядок выполнения задания, а затем дается достаточно подробный пример с необходимыми пояснениями. Разумеется, перед курсовым проектированием необходимо изучить соответствующие разделы лекционного курса и выполнить индивидуальные расчетные задания.

1. Последовательность выполнения задания и рекомендации по проектированию цифрового автомата

Для курсовой работы предлагается спроектировать цифровой автомат, структурная схема которого показана на рис.1.

Задание рекомендуется выполнять в следующем порядке:

1. Уточнить порядок функционирования предложенного для проектирования цифрового автомата (ЦА) в соответствии с заданием на курсовое проектирование, которое приводится ниже. Построить структурную схему ЦА с указанием схемы запуска, цепей формирования тактовых сигналов (Ф), сигналов сброса (W), входных сигналов (X) и т.д.

2. Определить период функционирования ЦА в соответствии с заданием на курсовое проектирование.

3. Определить необходимое количество триггеров для реализации регистра (RG).

4. Задать функцию переходов ЦА в виде графа и таблицы состояний ЦА.

5. Составить таблицу функций переходов и таблицу функций выходов.

6. С учетом рекомендуемого в задании на курсовое проектирование типа триггера и таблицы его состояний, приведенной в справочной литературе составить полную таблицу функционирования ЦА.

7. Провести минимизацию логических функций, описывающих работу комбинационных схем КС1, КС2, регистра RG.

8. Провести необходимые тождественные преобразования логических функций в соответствии с заданным в задании на курсовое проектирование логическим базисом для синтеза ЦА.

9. Выбрать тип ПЗУ, описать принцип его работы и составить таблицу программирования.

10. Построить функциональную схему ЦА.

11. С учетом функциональной схемы ЦА синтезировать его принципиальную электрическую схему на выбранных цифровых микросхемах. Описать работу примененных микросхем и ЦА.

12. С помощью интегрированного пакета – редактора схемотехники и SPCE симулятора "MULTISIM" провести анализ работы разработанной электронной схемы. Выявить возможные ошибки в схеме ЦА, сделать необходимые исправления Обширная библиотека компонентов интегрированного пакета "MULTISIM" включает генераторы сигналов, осциллографы, тестеры и т.д., огромное количество полупроводниковых приборов и микросхем разных фирм. Имеется возможность экспорта схемы в программы PCB – трассировки.

13. Составить перечень элементов (спецификацию) принципиальной электрической схемы.

14. Для создания принципиальной электрической схемы ЦА с помощью интегрированного пакета P-CAD использовать графический редактор P-CADSchematic.

15. Создать макет печатной платы ЦА. Для размещения компонентов и трассировки печатных плат использовать графический редактор P-CADPCB.

16. Результаты работы оформить в виде расчетно-пояснительной записки и графического материала на двух листах.

Результаты анализа принципиальной электрической схемы ЦА с помощью интегрированного пакета "MULTISIM" сохранить и использовать при защите курсовой работы для доказательства работоспособности разработанной схемы ЦА.

Обобщенная структурная схема (рис.1) цифрового автомата (ЦА) содержит запоминающее устройство ЗУ (RG - регистр, выполненный на триггерах), два комбинационных устройства: для формирования сигналов управления триггерами (КС1) и для формирования требуемых выходных сигналов (КС2).

ЦА работает циклами, заканчивая их всякий раз возвращением в исходное состояние.

Рис.1. Структурная схема цифрового автомата

По сигналу, например, с дешифратора команд ДШ схема запуска формирует входной сигнал x, который принимает только два значения: x1=0 (пауза в работе ЦА) и x2=1 (запуск и работа ЦА).

В ходе выполнения цикла ЦА в заданные моменты времени t1, t2, t3,... проходит через определенную последовательность внутренних состояний a(t) =al (l=0, 1,..., S), сменяющих друг друга при поступлении очередного тактового импульса Ф. При этом каждый цикл функционирования КА начинается в момент t поступления на его вход сигнала запуска x(t) =1.

Часть этих состояний (тактов), пребывание в которых сопровождается выдачей импульса на какой-либо выход y1, y2,..., можно назвать активными, а остальные, обеспечивающие заданные паузы между выдачами импульсов, – пассивными.

Пусть требуется синтезировать цифровой автомат (ЦА) с одним входом и пятью выходами. При этом на выходах y1, y2, y3, y4, y5 после запуска ЦА периодически, на каждом такте, появляются коды символов, образующих фамилию и инициалы студента. Каждый символ кодируется пятью битами: два старших разряда – номер строки, три младших разряда – номер столбца, согласно табл.1.

Период функционирования ЦА может быть определен согласно табл.1.

Таблица 1

Период функционирования цифрового автомата

![]()

| Символы | – | П | О | Ж | И | Л | О | В | А | – | О | – | И | – |

| 8-ричный код | 00 | 20 | 17 | 07 | 11 | 14 | 17 | 03 | 01 | 00 | 17 | 00 | 11 | 00 |

Каждый период (цикл) функционирования ЦА начинается в момент поступления на его вход сигнала запуска x(t) = 1. При поступлении на его вход очередного тактового импульса Ф, максимальное число которых равна периоду функционирования автомата R=14, ЦА проходит ряд сменяющих друг друга состояний a(t) = al (l = 0, 1, 2, …, S). Число рабочих состояний равно S, а общее число состояний ЦА, включая исходное a0, равно s+1 и связано с максимальным числом рабочих тактов R соотношением S ³ R.

Выполнение этого условия обеспечивает возможность выдачи выходных импульсов на любом такте цикла. Минимально необходимое количество триггеров для синтеза регистра (памяти) определяют из соотношения n ³ log2 (S + 1).

Для проектируемого ЦА минимальное количество триггеров n = 4, так как 24 > 14. Для определения активных состояний следует задать определенный порядок их чередования в рабочем цикле ЦА, т.е. функцию переходов.

В соответствии с заданием последовательность состояний регистра должна состоять из вычетов по модулю М, образовывать арифметическую прогрессию с разностью, равной простому наименьшему числу, не являющемуся делителем числа М, где М – период генерируемой последовательности.

В рассмотренном случае М = 14. Наименьшее простое число, не являющееся делителем 14, это 3. Поэтому состояния регистра будут изменяться в такой последовательности:

0, 3, 6, 9, 12, 1, 4, 7, 10, 13, 2, 5, 8, 11…

Каждое состояние регистра отождествляется с записанным в триггеры n-разрядным двоичным числом в соответствии с установленным выше правилом и может быть представлено табл.2.

Таблица 2

Таблица состояний цифрового автомата

Состояние регистра |

Сигналы QB(t) на прямых выходах триггеров T4, T3, T2, T1 | |||

| Q4(t) | Q3(t) | Q2(t) | Q1(t) | |

| a0 | 0 | 0 | 0 | 0 |

| a3 | 0 | 0 | 1 | 1 |

| a6 | 0 | 1 | 1 | 0 |

| a9 | 1 | 0 | 0 | 1 |

| a12 | 1 | 1 | 0 | 0 |

| a1 | 0 | 0 | 0 | 1 |

| a4 | 0 | 1 | 0 | 0 |

| a7 | 0 | 1 | 1 | 1 |

| a10 | 1 | 0 | 1 | 0 |

| a13 | 1 | 1 | 0 | 1 |

| a2 | 0 | 0 | 1 | 0 |

| a5 | 0 | 1 | 0 | 1 |

| a8 | 1 | 0 | 0 | 0 |

| a11 | 1 | 0 | 1 | 1 |

| a0 | 0 | 0 | 0 | 0 |

Алгоритм функционирования ЦА можно задать с помощью графа, в котором номер состояния удобно обозначить числом, характеризующим состояние регистра, а также указать номер выхода в каждом состоянии, на котором формируется сигнал 1 (рис.2).

Рис. 2. Алгоритм функционирования цифрового автомата, заданный с помощью графа.

Для синтеза КС1 и КС2 следует таблично задать функцию переходов (табл.3) и функцию выходов (табл.4).

Таблица 3

Таблица функций переходов

| Предшествующее состояние автомата a(t) | Последующее состояние автомата a(t+1) |

||

| при x(t) =1 | при x(t) =0 | ||

| a0 | 0000 | a3 | a0 |

| a3 | 0011 | a6 | a0 |

| a6 | 0110 | a9 | a0 |

| a9 | 1001 | a12 | a0 |

| a12 | 1100 | a1 | a0 |

| a1 | 0001 | a4 | a0 |

| a4 | 0100 | a7 | a0 |

| a7 | 0111 | a10 | a0 |

| a10 | 1010 | a13 | a0 |

| a13 | 1101 | a2 | a0 |

| a2 | 0010 | a5 | a0 |

| a5 | 0101 | a8 | a0 |

| a8 | 1000 | a11 | a0 |

| a11 | 1011 | a0 | a0 |

| a0 | 0000 | a0 | a0 |

| a0 | 0000 | a0 | a0 |

Таблица 4

Таблица функции выходов

Состояние автомата a(t) |

Значения выходных сигналов y(t) |

||||||

| y1 | y2 | y3 | y4 | y5 | W | ||

| a0 | 0000 | 0 | 0 | 0 | 0 | 0 | 0 |

| a3 | 0011 | 1 | 0 | 0 | 0 | 0 | 0 |

| a6 | 0110 | 0 | 1 | 1 | 1 | 1 | 0 |

| a9 | 1001 | 0 | 0 | 1 | 1 | 1 | 0 |

| a12 | 1100 | 0 | 1 | 0 | 0 | 1 | 0 |

| a1 | 0001 | 0 | 1 | 1 | 0 | 0 | 0 |

| a4 | 0100 | 0 | 1 | 1 | 1 | 1 | 0 |

| a7 | 0111 | 0 | 0 | 0 | 1 | 1 | 0 |

| a10 | 1010 | 0 | 0 | 0 | 0 | 1 | 0 |

| a13 | 1101 | 0 | 0 | 0 | 0 | 0 | 0 |

| a2 | 0010 | 0 | 1 | 1 | 1 | 1 | 0 |

| a5 | 0101 | 0 | 0 | 0 | 0 | 0 | 0 |

| a8 | 1000 | 0 | 1 | 0 | 0 | 0 | 0 |

| a11 | 1011 | 0 | 0 | 0 | 0 | 0 | 1 |

| a0 | 0000 | 0 | 0 | 0 | 0 | 0 | 0 |

Пусть в соответствии с заданием для синтеза регистра следует использовать RS-триггер. Можно применить ИМС 564ТР2. В одном корпусе микросхемы содержится четыре одинаковых независимых триггера (см. рис.3).

Рис.3. Микросхема 564ТР2 – четыре RS-триггера:

а – логическая структура одного триггера;

б – уловное изображение микросхемы на принципиальной электрической схеме

Эти триггеры выполнены на логических элементах ИЛИ-НЕ и являются асинхронными RS-триггерами с прямым управлением, т.е. переключаются сигналами логической единицы. В табл.5 описываются состояния, характеризующие работу триггера.

Таблица 5

Состояния RS-триггера с прямым управлением

| Такт tn | Такт tn+1 | |||

| Qn | Rn | Sn | Qn+1 | |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | Н/О | Н/0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | Н/О | Н/О |

Каждый триггер имеет два входа S и R и один выход Q (выходы ![]() к внешним выводам микросхемы не подключены). Характерной особенностью этой ИМС является наличие разрешающего входа V – общего для всех четырех триггеров. Когда на этом входе единичный сигнал – информация на выходах триггера присутствует, при логическом нуле – нет. Вход, по которому RS-триггер устанавливается в состояние 1, обозначается буквой S, а в состояние 0 – буквой R. Если на один из входов подать единичный сигнал, сохраняя нулевой на другом, триггер примет состояние, которое однозначно определяется входной информацией. При входных сигналах S=1, R=0 триггер принимает единичное состояние Q=1,

к внешним выводам микросхемы не подключены). Характерной особенностью этой ИМС является наличие разрешающего входа V – общего для всех четырех триггеров. Когда на этом входе единичный сигнал – информация на выходах триггера присутствует, при логическом нуле – нет. Вход, по которому RS-триггер устанавливается в состояние 1, обозначается буквой S, а в состояние 0 – буквой R. Если на один из входов подать единичный сигнал, сохраняя нулевой на другом, триггер примет состояние, которое однозначно определяется входной информацией. При входных сигналах S=1, R=0 триггер принимает единичное состояние Q=1, ![]() =0, а при S=0, R=1 – нулевое: Q=0,

=0, а при S=0, R=1 – нулевое: Q=0, ![]() =1.

=1.

При появлении управляющего сигнала на одном из входов происходит либо опрокидывание триггера, либо подтверждение существующего состояния, если оно совпадает с требуемым. Если одновременно подать переключающие сигналы на оба входа (S=R=1), на обоих выходах появятся логические нули (Q=![]() =0) и устройство утратит свойство триггера. Комбинацию S=R=1 называют неопределенной (Н/О). Переход от неопределенной комбинации к нейтральной (S=R=0) называют запрещенной комбинацией, так как состояние выходов при этом восстанавливается, но с равновероятностью оно может стать как единичным, так и нулевым. Это ведет к непредсказуемому поведению триггера.

=0) и устройство утратит свойство триггера. Комбинацию S=R=1 называют неопределенной (Н/О). Переход от неопределенной комбинации к нейтральной (S=R=0) называют запрещенной комбинацией, так как состояние выходов при этом восстанавливается, но с равновероятностью оно может стать как единичным, так и нулевым. Это ведет к непредсказуемому поведению триггера.

Для синтеза ЦА необходимо применить синхронный (тактируемый) RS-триггер. Однако в известных сериях микросхем синхронные RS-триггеры как самостоятельные изделия отсутствуют.

Применение синхронного триггера позволяет увеличить помехоустойчивость схемы, т.е. исключить ложные срабатывания триггера из-за возможного возникновения состязания сигналов (гонок) или от помех. Опрокидывание синхронного триггера происходит только при участии тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входные сигналы, равно как и помехи различного происхождения, триггер не реагирует.

Синхронный (тактируемый) RS-триггер получают из асинхронного RS-триггера путем подключения к его выводам схемы управления, состоящей из логических элементов И-НЕ (рис.4).

Рис.4. Логическая структурная схема синхронного RS-триггера со статическим управлением.

Полученный синхронный RS-триггер будет управляться следующим образом: переброс триггера осуществляется сигналами Sn=0, Rn=0 при С=0, т.е. нулевыми логическими уровнями. Он оказывается синхронным RS-триггером с инверсным управлением. Для реализации такого триггера совместно с микросхемой 564ТР2 следует применить две микросхемы 564ЛА7, каждая их которых содержит по четыре логических элемента 2 И-НЕ. На функциональной схеме синхронный RS-триггер с инверсным управлением обозначают согласно рис.5.

Рис.5. Синхронный RS-триггер с инверсным управлением

Для реализации синхронного RS-триггера с прямым управлением следовало бы совместно с микросхемой 564ТР2 применить микросхемы, содержащие двухвходовые элементы И. Однако в сериях микросхем К176, К561, К564 таких элементов нет, а применение подходящих других элементов из этих серий существенно усложнит принципиальную электрическую схему ЦА. Для синтеза ЦА целесообразно использовать синхронный RS-триггер с инверсным управлением, который может быть реализован из микросхем 564ТР2 и 564ЛА7.

Поэтому выполняют регистр на синхронных RS-триггерах с инверсным управлением, которые работают так, что:

1) Если такой триггер должен перейти из нуля в единицу, то к приходу тактового импульса на тактовый вход нужно обеспечить S=0, R=1.

2) Если триггер должен опрокинуться из единицы в нуль, следует к приходу тактового импульса установить S=1, R=0.

3) Если же требуется сохранить состояние триггера "единица", то необходимо к приходу тактового импульса установить S=X, R=1, т.е. сигнал на входе S может быть либо 0, либо 1 и не влияет на поведение триггера.

4) Если триггер должен остаться в состоянии "ноль", то нужно к приходу тактового импульса установить S=1, R=X, т.е. сигнал на входе R не влияет на поведение триггера.

Закон функционирования синхронного RS-триггера с инверсным управлением можно также представить в виде табл.6.

Таблица 6

Закон функционирования синхронного RS-триггера с инверсным управлением

| Такт tn | Такт tn+1 | ||

| Qn | Rn | Sn | Qn+1 |

| 0 | 0 | 0 | Н/О |

Продолжение табл.6 |

|||

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | Н/О |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Если учесть, что Qn+1 зависит только от Sn и Rn, то из табл.6 можно исключить столбец Qn и получить минимизированную табл.7.

Таблица 7

Состояния синхронного RS-триггера с инверсным управлением (минимизированная форма) при C=0

| Sn | Rn | Qn+1 |

| 0 | 0 | Н/О |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | Qn |

Используя таблицу состояний ЦА (табл.2), таблицу функции переходов (табл.3), таблицу функции выходов (табл.4) и таблицу состояний синхронного RS-триггера с инверсным управлением (табл.7), составляют полную таблицу функционирования ЦА (табл.8). Переход от одного состояния ЦА к другому осуществляется под воздействием тактовых импульсов Ф, поступающих одновременно на тактовые входы всех четырех триггеров.

К приходу очередного тактового импульса на управляющих входах (R, S) триггеров должны существовать сигналы, обеспечивающие срабатывание только тех триггеров, которые должны изменить свое состояние при переходе к следующей кодовой комбинации. Таким образом, для каждой кодовой группы, характеризующей состояние регистра, необходимо найти сигналы на управляющих выходах триггеров, обеспечивающих переход к следующей кодовой группе.

В табл.8 указывают значения сигналов, которые должны быть поданы на управляющие входы триггеров для того, чтобы обеспечить переход от данного состояния регистра к последующему.

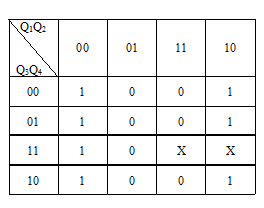

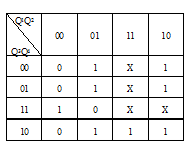

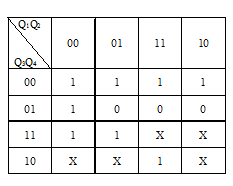

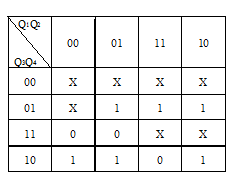

Данные из табл.8 переносят на карты Карно (Рис.6) с тем, чтобы провести минимизацию логических функций, определяющих каждый из управляющих сигналов триггеров, а затем составить логическую цепь, реализующую полученные функции, т.е. синтезировать функциональную, а затем и принципиальную электрические схемы комбинационного устройства КС1 и регистра RG (память на триггерах).

а) S1 = Q1

б) R1 = ![]() 1

1

в) S2 = Q2 + Q1![]() 4 + Q1

4 + Q1![]() 3 +

3 + ![]() 1Q3Q4

1Q3Q4

г) R3 = ![]() 3 +

3 + ![]() 1

1![]() 2

2![]() 4

4

д) S3 = ![]() 1

1![]() 2 + Q3 + Q1Q2Q4

2 + Q3 + Q1Q2Q4

е) R3 = ![]() 3 +

3 + ![]() 1

1![]() 2

2![]() 4

4

ж) S4 = ![]() 3 + Q4 +

3 + Q4 + ![]() 1

1![]() 2

2

з) R4 = ![]() 3 +

3 + ![]() 4

4

Рис.6. Карты Карно для минимизации логических функций, описывающих работу КС 1.

В этих картах по две клетки (комбинации 1111 и 1110) оказались не заполненными: эти клетки соответствуют неиспользованным кодовым комбинациям. Совокупность четырех триггеров, образующих регистр, может находиться в одном из шестнадцати состояний: 24=16, из которых для формирования кодов импульсов на выходе ЦА используется только четырнадцать. Эти клетки можно заполнить символами "Х". Это означает, что минимизируемая функция может при данном наборе аргументов Q1…Q4 принимать любое значение: 0 или 1.

Особенностью минимизации логических функций, значение которых при определенных наборах аргументов не играет роли (клетки заполняются символами "Х") является то, что при проведении на картах контуров, охватывающих единицы, можно включать в эти контуры также и клетки, в которых функция не определена.

Синтез комбинационной схемы КС1 можно осуществить в логическом базисе И, ИЛИ, НЕ по логическим функциям для сигналов на управляющих входах триггеров. Эти логические функции получены в минимизированной дизъюнктивной нормальной форме (МДНФ):

Схема

S1 = Q1 S2 = Q2 + Q1 S3 = S4 = |

R1 = R2 = R3 = R4 = |

Пусть в соответствии с заданием синтез схемы следует провести в логическом базисе ИЛИ-НЕ.

Для этого следует с помощью законов дуальности (теоремы де-Моргана) исключить из логических выражений функцию И:

![]()

![]()

![]()

![]()

По полученным после преобразований логическим функциям строят КС1 в логическом базисе ИЛИ-НЕ.

Комбинационную схему КС2 строят на постоянном запоминающем устройстве (ПЗУ). Для этого можно применить ПЗУ с произвольным доступом к памяти, когда место искомой информации однозначно определяется адресом, а информация извлекается и заносится в кодоимпульсной форме. В качестве ПЗУ целесообразно применить перепрограммируемое (репрограммируемое) полупроводниковое запоминающее устройство. Закон программирования ПЗУ может быть задан табл.9, которую составляют на основе табл.8.

Таблица 9

Таблица программирования ПЗУ

| Адрес строки | Содержимое строки ПЗУ | ||||||||

| А3 | А2 | А1 | А0 | y1 | y2 | y3 | y4 | y5 | W |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 |

Как видно из табл.9, при выборе типа интегральной схемы ПЗУ следует учитывать, что она должна обладать памятью не менее 14 бит и иметь не менее 6 выходных шин, а также быть совместимой с интегральными схемами, на которых построены КС1 и регистр, например, ПЗУ типа КР556РТ5 [3].

Сначала строят функциональную схему, а потом, с учетом применения интегральных схем – принципиальную схему ЦА.

2. Задание к курсовому проектированию

Синтезировать цифровой автомат (ЦА), у которого на выходе "у" периодически появляются коды символов, образующих фамилию и инициалы студента (рис.7).

| Символы | – | П | Е | Т | Р | О | В | – | П | – | П | – | П | Е | Т |

| 8-ричный код | 00 | 20 | 06 | 23 | 21 | 17 | 03 | 00 | 20 | 00 | 20 | 00 | 20 | 06 | 23 |

Рис.7. Символы и их 8-ричные коды

Каждый символ кодируется пятью битами согласно табл.10: два старших разряда – номер строки, три младших разряда – номер столбца.

Таблица 10

Способы кодирования символов

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | |

| 0 | – | А | Б | В | Г | Д | ЕЁ | Ж |

| 1 | З | И | Й | К | Л | М | Н | О |

| 2 | П | Р | С | Т | У | Ф | Х | Ц |

| 3 | Ч | Ш | Щ | Ы | ЬЪ | Э | Ю | Я |

Длина периода должна быть в пределах 9-16 символов. Если период меньше 9 символов, то можно написать имя полностью. Если период больше 16 символов, можно убрать пробел(ы) или один-два инициала.

Обобщенная структурная схема ЦА показана на рис.8.

Рис.8. Обобщенная структурная схема цифрового автомата:

КС1, КС2 – комбинационные схемы; RG – регистр

Одна из схем (по согласованию с преподавателем) КС1 или КС2 должна быть выполнена на постоянном запоминающем устройстве (ПЗУ). Другая схема выполняется в логическом базисе, который определяется из табл.11 по последней цифре шифра (номера зачетной книжки). Регистр выполняется на триггере, тип которого определяется из табл.11 по предпоследней цифре шифра.

Последовательность состояний регистра должна состоять из вычетов по модулю М, образовывать арифметическую прогрессию с разностью, равной наименьшему простому числу, не являющемуся делителем числа М, где М – период генерируемой последовательности. Для примера, приведенного на рис.7, М = 12. Наименьшее простое число, не являющееся делителем 12, это 5. Поэтому состояния регистра будут изменяться в такой последовательности:

0, 5, 10, 3, 8, 1, 6, 11, 4, 9, 2, 7, 0, 5, …

Логический базис, в котором следует разрабатывать принципиальную электрическую схему ЦА выбирают из табл.11по последней цифре шифра, где также по предпоследней цифре шифра выбирают тип триггера.

Таблица 11

Логический базис и тип триггера

Последняя цифра шифра |

Логический базис | Предпоследняя цифра шифра | Тип триггера |

0 1 2 3 4 |

И-НЕ | 0 1 2 3 |

RS |

4 5 6 |

JK | ||

5 6 7 8 9 |

ИЛИ-НЕ | 7 8 9 |

RS |

Выполненное задание представляется в виде расчетно-пояснительной записки, оформленной в соответствии с общими требованиями и правилами, и графического материала:

– лист 1: Структурная схема ЦА. Алгоритм функционирования ЦА, заданный с помощью графа. Полная таблица функционирования ЦА. Таблица программирования ПЗУ.

– лист 2: Принципиальная электрическая схема ЦА, выполненная в соответствии с ГОСТ 2.743 – 97 "Обозначения условные графические в схемах. Элементы цифровой техники". Чертежи печатной платы ЦА, созданной с помощью интегрированного пакета PCAD.

Результаты анализа принципиальной электрической схемы ЦА с помощью интегрированного пакета "MULTISIM" сохраняются в электронном виде и используются при защите курсовой работы.

Для выполнения курсовой работы потребуется интегрированный пакет программ "MULTISIM" и один из самых популярных пакетов программ для схемотехников и радиоинженеров "P-CAD"

Эти пакеты программ установлены на ПК в вычислительном зале кафедры АСУИУ.

Библиографический список

1. Савельев А.Я. Арифметические и логические основы цифровых автоматов. – М.: Высшая школа, 1980. -165 с.

2. Баранов С.И. Синтез микропрограммных автоматов. – Л.: Энергия, 1979. -152 с.

3. Аналоговые и цифровые интегральные микросхемы; Справочное пособие / С.В. Якубовекий, Н.А. Барканов, Л.И. Ниссельсон и др.; Под ред. С.В. Якубовекого. – 2-е изд., перераб. и доп. – М.: Радио и связь, 1985. – 432 с., ил.

4. Стешенко В.Б. P-CAD. Технология проектирования печатных плат. - СПб.: БХВ-Петербург, 2003. -720 с.: ил.