| Скачать .docx |

Курсовая работа: Проектирование аппаратуры передачи данных

Министерство науки и образования Украины

Пояснительная записка

к курсовому проекту

по дисциплине

"Компьютерные сети"

на тему

"Проектирование аппаратуры передачи данных"

2006

Данный документ представляет собой пояснительную записку к курсовому проекту по дисциплине «Компьютерные сети» на тему «Разработка сетевого звена передачи данных».

Целью курсового проектирования является углубление теоретических знаний в области систем передачи данных и компьютерных сетей, приобретение практических навыков разработки, анализа и конструирования электрических схем устройств систем передачи данных.

Устройство передачи данных является завершенной конструктивной единицей, состоящей из передающей и приёмной части. Основная функция передающей части получение данных от компьютера и преобразований их для передачи по каналу связи. Приемная часть получает данные из канала связи и преобразует их к исходному виду.

К данному документу прилагаются функциональные схемы передающей и приёмной частей звена передачи данных, а также программное обеспечение для них.

Введение

1 Постановка задачи

2 Обобщенная структурная схема АПД

3 Разработка УПС

3.1 Расчет параметров прямого канала

3.2 Расчет параметров обратного канала

3.3 Разработка передающей части УПС

3.4 Разработка приемной части УПС

4 Разработка УЗО

4.1 Выбор способа защиты от ошибок

4.2 Разработка формата сообщения

5 Алгоритм функционирования передающей части АПД

6 Алгоритм функционирования приемной части АПД

7 Разработка функциональной схемы

7.1 Передающая часть АПД

7.2 Приемная часть АПД

Заключение

Список используемой литературы

Приложение А – Временные диаграммы передающей части АПД

Приложение Б – Временные диаграммы приемной части АПД

Приложение В – Блок-схема функционирования передающей части АПД

Приложение Г – Блок-схема функционирования приемной части АПД

Приложение Д – Текст программы передающей части АПД

Приложение Е – Текст программы приемной части АПД

Введение

Развитие вычислительной техники в наши дни позволяет абонентам вычислительных сетей передавать данные со своего рабочего места в любую точку мира. И таким образом большинство задач обработки данных становятся задачами телеобработки данных. В процессе телеобработки осуществляется обмен, как между различными абонентами информационной системы, так и между абонентами и центральной ЭВМ. Важное место в системе обмена информацией между удаленными абонентами АИС и АСУ занимают технические средства, осуществляющие передачу данных между оконечным оборудованием данных (ООД), в качестве которого выступает ЭВМ, устройства ввода-вывода информации, цифровые измерительные приборы. Аппаратура передачи информации включают в себя аппаратуру передачи данных (АПД) с устройствами сопряжения между ООД и каналами передачи данных.

Объектом курсового проектирования является аппаратура передачи данных, позволяющая передать 20 кБит данных за период 1,2 минуты, при этом для соединения АПД с ООД применён стык С3 на передающей стороне и С2 на приёмной. В качестве линии связи выступает физическая линия со следующими параметрами: эффективное значение напряжения помехи – 2,2 мВ, неравномерность ГВП канала – 3,0 мс, ошибки при передаче объединяются в пакеты длиной не более 8-ми элементов, причём вероятность появления таких пакетов равна 8×10-5. Тип кабеля связи, переходное затухание и длина линии не нормируются. Необходимо реализовать безмаркерный способ фазирования по циклам с вероятностью ложного запуска не более 0,8×10-5.

Задачей данного курсового проекта является разработка передающей и приемной части в соответствии с заданными параметрами. Требуется рассчитать основные параметры необходимых блоков исходя из варианта. На основе полученных данных необходимо разработать функциональную схему устройства преобразования сигналов (УПС) и устройство защиты от ошибок (УЗО) и написать алгоритм его функционирования. Проектирование должно осуществляться на основе данных, указанных в задании на работу.

В процессе проектирования необходимо провести сравнительную характеристику возможных вариантов систем передачи дискретной информации, удовлетворяющих заданным требованиям варианта. Основными данными по проекту являются объем передаваемой информации, равный 20 кБит, время передачи данного массива данных 1,2 минуты. Данные будут передаваться по телефонному каналу связи, следовательно, зная скорость передачи, можно выбрать параметры АПД из стандартных протоколов. Необходимо учесть, что телефонный канал не позволяет организовать передачу данных со скоростью более 9600 бит. Также необходимо учесть, что при передаче информации по телефонному каналу применяется обязательная модуляция, для переноса спектра сигналов в полосу частот выбранного канала связи. В данном случае была выбрана частотная модуляция.

Для обеспечения помехоустойчивости необходимо спроектировать устройство защиты от ошибок (УЗО).

Необходимо разработать алгоритм функционирования передающей и приемной частей УПС, а также их функциональные схемы.

Для синхронизации работы отдельных частей УПС требуется построить временные диаграммы функционирования модулей.

2 Обобщенная структурная схема АПД

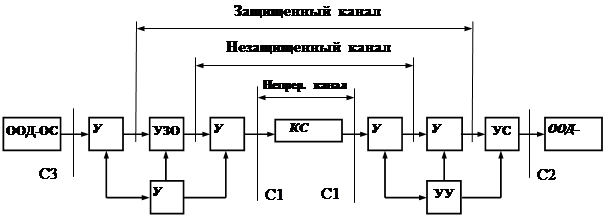

Обобщенная структурная схема системы передачи данных (СПД) представлена на рисунке 2.1.

Рисунок 2.1 – Обобщенная структурная схема СПД

Она состоит из оконечного оборудования, выполняющего функции отправителя (ООД—ОС) и получателя (ООД—ПС) сообщений, устройства защиты от ошибок (УЗО), устройства преобразования сигналов (УПС) и канала связи. В УЗО происходит кодирование-декодирование данных. УПС осуществляет преобразование сигналов данных в форму, удобную для передачи по каналу связи, а устройства сопряжения (УС) обеспечивают обмен информационными и управляющими сигналами между АПД и ООД. Координация взаимодействия составных частей СПД обеспечивается специальными импульсами, вырабатываемыми устройством управления (УУ). Совокупность непрерывного канала с включенными на его входе и выходе УПС называют незащищенным (НК) или каналом передачи данных (ПД), а объединение НК с УЗО – защищенным от ошибок (ЗК) каналом ПД. Для обмена информацией между абонентами используются две однонаправленные СПД, которые конструктивно могут быть выполнены в виде одной дуплексной СПД.

Основными характеристиками, определяющими качество и эффективность передачи данных, являются надежность, скорость и верность передачи, а также удельная скорость. Немаловажным показателем является сложность аппаратурной реализации, определяющая ее стоимость. При выборе вариантов проектируемой аппаратуры необходимо остановиться на том, который при равенстве одного или нескольких показателей обеспечивает более высокие остальные. Однако в зависимости от назначения технических средств часто приходится ухудшать одни показатели (например, стоимость или скорость) с целью обеспечения более высоких других показателей.

Задачей проектирования является разработка АПД, удовлетворяющей заданным требованиям:

алгоритм работы должен быть достаточно гибок;

схема должна обладать высоким быстродействием;

должна соблюдаться функциональная независимость отдельных узлов СПД;

стоимость аппаратурной реализации должна быть минимальной [2].

Для обмена информацией между абонентами используются две однонаправленные СПД, которые конструктивно могут быть выполнены в виде одной дуплексной СПД.

Основными характеристиками, определяющими качество и эффективность передачи данных, являются надёжность, скорость и верность передачи, а также удельная скорость.

При выборе вариантов проектируемой аппаратуры необходимо остановится на том, который при равенстве одного или нескольких показателей обеспечивает более высокие остальные. Однако в зависимости от назначения технических средств часто приходится ухудшать одни показатели с целью обеспечения более высоких других показателей.

3.1 Расчет параметров прямого канала

Определим необходимую скорость передачи данных по каналу связи при условии, что объем служебной информации за сеанс не превысит 8%:

V = (1,08×In)/Тcc = (1,08×20×1024) / 72 = 307 (бит/с) (3.1.1)

где In – объем информации, подлежащий передаче потребителю, за сеанс;

Tcc – время сеанса связи (время передачи);

Выбираем из ряда скоростей скорость 600 бит/с.

Согласно рекомендации МККТТ V.22 и V.22 бис при разработке УПС для полудуплексной передачи со скоростью 600 бит/с по коммутируемым телефонным сетям общего пользования предусмотрено частотное разделение канала тональной частоты путем деления на два подканала при использовании частотной модуляции. Так физическая реализация частотных модуляторов и демодулятор несложная, а при данной скорости передачи частотная модуляция обеспечивает достаточно высокую помехоустойчивость, то модуляцию данных для передачи в канал будем осуществлять именно этим способом. Обратный канал можно использовать для исправления ошибок при применении системы с решающей обратной связью.

Определяем эффективную скорость передачи

Vэф = Iп / Tсс = 20×1024 / 72 = 284 (бит/с) (3.1.2)

Средняя частота прямого канала составляет Fср=1500 Гц (УПС -1,2 ТЧ/ТФ-ПД) [7]. Девиация частоты Dw = +200 Гц и Dw=-200 Гц.

Частота передачи двоичной единицы для прямого канала f1= 1300 Гц, а частота передачи двоичного нуля f0= 1700 Гц (справочные данные).

Допустимое отклонение характеристических частот номинального значения для прямого канала ±10 Гц.

Определим длительность единичных элементов t0 :

V=(log 2 mс)/t0, (3.1.3)

где mс – количество позиций сигнала.

При ЧМ применяется двухпозиционный сигнал, следовательно mс = 2, тогда

V=1/t0 =600 бод (3.1.4)

Для двухпозиционных сигналов скорость модуляции и скорость передачи совпадают.

Длительность единичного элемента для прямого канала:

t0=1/V=1/600=1,67 (мс) (3.1.5)

Требуемая ширина пропускания Dfпф фильтров передачи определяется по формуле:

Dfпф =1,42×В = 1,42×600 = 852 Гц (3.1.6)

С учетом допуска на временную и температурную нестабильность параметров фильтра берем Dfпф = 940 Гц (то есть на 10% больше рассчитанного).

Определяем отношение несущей частоты к модулирующей для передачи по прямому каналу:

Для «1»: f1/fмод = 1300 / 600 =2,17 (3.1.7)

Для «0»: f0/fмод = 1700 / 600 =2,83 (3.1.8)

Так как отношения меньше 3, то при модуляции возникает «отраженный спектр» и данные будут искажаться еще в приемнике. Поэтому для борьбы с «отраженным спектром» будем осуществлять модуляцию на повышенной несущей частоте с последующим переносом спектра сигнала в полосу пропускания канала.

Несущая частота f1м должна быть в 5-10 раз больше частоты модулирующего сигнала.

f1м >=5×B>=5×600 = 3000(Гц) (3.1.9)

Полосовой фильтр ПФ1 будет пропускать сигналы в диапазоне частот 3000 - Dfпф / 2; 3000 + Dfпф / 2. Получаем, что диапазон (2530 – 3470) Гц.

Среднее значение частоты передачи в прямом канале связи:

Fcp=(f1+f0)/2=(1300+1700)/2=1500 Гц (3.1.10)

Тогда чтобы перенести сигнал в эту область генератор преобразователя должен иметь частоту fм2=fм1-fср=3000-1500 = 1500 Гц.

После модуляции получаем верхнюю и нижнюю боковую полосу, но будем передавать только нижнюю боковую полосу частот.

Fн = 2530 Гц и Fв = 3470 Гц

Тогда полоса пропускания ПФ2 будет такая

(2530 – 1500; 3470 – 1500) = (1030 – 1970) Гц

Для обеспечения высокой помехоустойчивости и скорости передачи информации при транспортировке больших массивов сообщений следует строить синхронные УПС.

Вероятность ошибочного приема единичных элементов Роп вычисляется по следующей формуле

Роп = 0.5×(tпр×vпр)/3600×t0×В = 0,5×5×10-3×8/3600×600×1/600 = 5,66*10-6 (3.1.11)

где tпр – средняя длительность перерывов в долях от t0;

vпр – интенсивность перерывов.

Максимально допустимая вероятность ошибок на выходе УПС от воздействия флуктуационных помех:

Роф <Р0-Роп (3.1.12)

Роф<10-3 - 5,66×10-6 = 0,99×10-3

Определение метода регистрации единичных элементов.

Средняя длительность перерывов tпр = 5 (мс) больше длительности единичных элементов (1,67 мс) и, следовательно пропадание единичного элемента возможно при любом методе регистрации. В кабельных каналах связи наиболее устойчивым является метод регистрации стробированием. Поэтому будем использовать эту регистрацию.

Максимально допустимая средне квадратичная величина краевых искажений вычисляется по формуле

dкв = (mэф - dпр)/z (3.1.13)

где mэф = 45 – 48 % - исправляющая способность

Искажение единичных элементов может происходить при сдвиге несущей частоты в каналообразующей аппаратуре. При этом с ЧМ сдвиг частоты приводит к постоянным преобладающим искажениям, величина которых dпр может быть оценена выражением

d пр = (df×B/(Df×DFk))×100% (3.1.14)

где df – сдвиг частоты в канале связи (не превышает 5 Гц для телефонных каналов);

Df – девиация частоты (она равна 200 Гц);

DFk – рассчитанная эффективная полоса пропускания канала (940 Гц).

d пр = (5×600/(200×940)) ×100 % = 1,596 %

где z – аргумент функции Крампа, который мы можем найти, используя заданную допустимую вероятность ошибки регистрации

Ф(z) = 1 – P0 = 0,999 (3.1.15)

и из таблицы выбираем z = 3,30, тогда получаем

dкв = (45 – 1,596) / 3,30 = 13,153 %.

Воспользовавшись найденными величинами, найдем отношение сигнал/помеха. Величина dкв для систем с различными видами модуляции может быть найдена по формуле

d кв =(В/(2*q*DFк))*100% (3.1.16)

Из этой формулы выражаем q:

q = (B×100 %)/(d кв ×2×DFк) = (600×100)/(13,153×2×940) = 2.43 (3.1.17)

Рассчитаем эффективное значение помехи на входе первого фильтра приемника. Uп эф = 0,0022 В – по заданию.

Uc эф ≥q×Uп эф , следовательно

Uc эф = Uп эф×q = 2,43×0,0022 = 0,0054 (В) (3.1.18)

Соответственно минимально допустимый уровень сигнала на выходе канала будет

Рс вых = 20×lg(Uc эф/Uисх) = 20×lg(0,0054/0,775) = -43 дБ (Uисх = 0,775 В) (3.1.19)

С учетом затухания канала минимальный уровень сигнала на выходе передающей части (входе канала) должен быть

Рс вх > Рс вых +аост =–43+20=–23дБ (3.1.20)

Для определения необходимости коррекции характеристики ГВП канала рассчитаем максимально допустимую величину ее неравномерности. Так как характеристика ГВП для канала ТЧ имеет обычно четко - симметричный характер, то

tгр доп=1/В=1/600=0,001667 = 1,667×10-3 (с) (3.1.21)

По техническому заданию неравномерность ГВП составляет 3*10-3 (с).

Расчет устройства синхронизации.

Определим допустимую погрешность синхронизации по формуле:

едоп = 0,5 – mэф – dпр = 0,5 – 0,45 – 0,01596 = 0,034 (3.1.22)

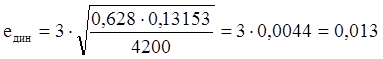

Динамическая составляющая погрешности определяется по формуле:

(3.1.23)

(3.1.23)

где mд – коэффициент деления делителя частоты;

S – коэффициент деления реверсивного счетчика;

Тс – время синхронизации.

Найдем неизвестные нам величины mд и S

Тс = S × mд /В (3.1.24)

следовательно S × mд = Тс × B = 7 × 600 = 4200, тогда

Определим допустимую статическую погрешность синхронизации при заданных параметрах краевых искажений:

ест = едоп – един = 0,034 – 0,013 = 0,021 (3.1.25)

Допустимая величина коэффициента нестабильности задающих генераторов kf модулятора и демодулятора равна

kf = едоп /(2×В×tпс) = 0,034 / (2×600×1,6) = 1,77×10-5 (3.1.26)

где tпс – время поддержки синхронизма.

Найдем коэффициент деления реверсивного счетчика и делителя частоты S и mд соответственно. Для этого решим систему:

![]()

(3.1.27)

(3.1.27)

ест = 1/mд + 4 × kf × S

Решив систему и округлив полученные значения, получим следующие результаты: S = 70, mд = 64. Следовательно, частота задающего генератора равна

f0 = mд×fв = 64×600 = 38400 Гц (3.1.28)

3.2 Расчет параметров обратного канала

Вместе с прямым каналом передачи возможно применение обратного канала связи с ЧМ и скоростью 75 бод.

Частота передачи двоичной единицы для обратного канала f1= 390 Гц, а частота передачи двоичного нуля f0= 450 Гц (справочные данные).

Допустимое отклонение характеристических частот номинального значения для обратного канала ±4 Гц (справочные данные).

Длительность единичного элемента для обратного канала:

t0 = 1/V = 1/75 = 13 (мс) (3.2.1)

где V – скорость передачи обратного канала.

Отношение несущей частоты к модулирующей для передачи по обратному каналу

для «1»: f1 / fмод = 390 / 75 = 5,2 (3.2.2)

для «0»: f0 / fмод = 450 / 75 = 6 (3.2.3)

Так как отношения больше 3, то «отраженный спектр» при передаче отсутствует. Несущая частота, вырабатываемая генератором:

Fcp = (f1 окс + f0 окс) / 2 = (390 + 450) / 2 = 420 Гц (3.2.4)

Требуемая ширина пропускания Dfпф окс фильтров передачи определяется по формуле:

Dfпф окс = 1,42×В = 1,42×75 = 107 Гц (3.2.5)

С учетом допуска на временную и температурную нестабильность параметров фильтра берем Dfпф окс = 120 Гц (то есть на 10 % больше обычного).

Тогда полоса пропускания фильтра будет

Dfпф окс = (420 – 120/2; 420 + 120/2)=(360-420) Гц (3.2.6)

Вероятность ошибочного приема единичных элементов Роп вычисляется по следующей формуле

Роп = 0,5× (tпр×vпр)/3600×t0×В = 0,5×5×10-3×8/3600×75 = 5,6×10-6 (3.2.7)

где tпр – средняя длительность перерывов в долях от t0

vпр – интенсивность перерывов.

Максимально допустимая вероятность ошибок приема при В = 75 бод (P0 = 10-4).

Максимально допустимая вероятность ошибок на выходе УПС при воздействии флуктуационных помех

Роф < Р0 – Роп (3.2.8)

Роф < 10-4 – 5,5×10-6 = 0,95×10-5

3.3 Разработка передающей части УПС

Структурная схема передающей части УПС изображена на рисунке 3.3.1

|

Рисунок 3.3.1 – Структурная схема передающей части УПС

Полосы пропускания полосовых фильтров ПФ1 и ПФ2, частоты генераторов Г1 и Г2 рассчитаны в пункте 3.1. Выберем модуляторы М1 и М2 и рассчитаем их параметры.

В настоящее время в УПС применяются в основном модуляторы ЧМ-сигналов, которые называют цифровыми. Они построены на основе цифровых элементов. Использование опорного генератора, стабилизированного кварцем, и элементов цифровой техники позволяет строить схемы модуляторов, обладающих высокой временной и температурной стабильностью и малой зависимостью параметров генерируемых сигналов от колебаний напряжения источника питания.

Модуляторы, построенные по принципу цифровых, имеют ряд недостатков: сравнительно широкий спектр прямоугольных ЧМ-сигналов, что вынуждает применять сложные ФНЧ высокого порядка; разрыв фазы ЧМ-колебаний, вызываемый изменением информационного сигнала в случайные моменты времени по отношению к окончанию периода колебания на выходе управляемого делителя. Схемы синхронизации являются громоздкими и вызывают дополнительные краевые искажения модулированных сигналов. Более перспективными являются ЧМ-модуляторы со ступенчатой аппроксимацией синусоидального сигнала. В схеме такого модулятора имеется функциональный цифроаналоговый преобразователь (ФЦАП), вход которого соединен с выходом управляемого делителя частоты (УДЧ), а его выход – с ФНЧ. Структурная схема ЧМ-модулятора со ступенчатой аппроксимацией синусоидального сигнала и временные диаграммы его работы представлены на рисунке 3.3.2, а, б. Синусоидальный сигнал формируется kст ступеньками напряжения. Как видно из временной диаграммы, переключение частоты происходит плавно, а краевые искажения сигналов на выходе такого модулятора в kст меньше, чем в модуляторах без ФЦАП. Так как для аппроксимации синусоиды используется четное число ступенек kст , то в спектре такого сигнала будут только нечетные гармоники, ближайшей после первой гармоники будет (kст -1)-я гармоника, следующей – (kст +1)-я и т.д.

а)

|

Рисунок 3.3.2 – ЧМ–модулятор со ступенчатой аппроксимацией сигнала: а – структурная схема; б – временные диаграммы

Коэффициент искажения синусоиды за счет аппроксимации Ки определяется на основании спектрального анализа:

Kи = 2π/( kст -![]() ) (3.3.1)

) (3.3.1)

Так как коэффициент искажения синусоидального сигнала должен быть не более 12%, определим необходимое число ступенек аппроксимирующего сигнала

kст ≥ 2π/(Ки ![]() ) = 2π/(0,12

) = 2π/(0,12 ![]() ) = 15,1 (3.3.2)

) = 15,1 (3.3.2)

Округлим kст до ближайшего большего целого четного числа: kст = 16.

Количество ступенек сигнала для прямого и обратного каналов совпадают. Высота i–й ступеньки аппроксимированной синусоиды в относительных единицах определяется по формуле:

Ui = sin [ 360 (i+0,5) / kст ], i = 0,1,2,…, ( kст - 1 ) (3.3.3)

Рассчитав данные значения, построим ступенчатую аппроксимацию синусоидального сигнала, изображенную на рисунке 3.3.3.

Рисунок 3.3.3 – Ступенчатая аппроксимация синусоидального сигнала

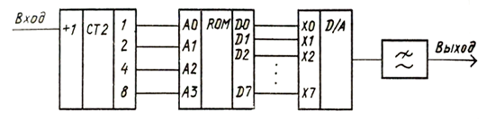

При использовании ИМС более высокой степени интеграции, а также в микропроцессорных УПС для формирования синусоидальных сигналов целесообразно использовать построенное запоминающее устройство (ПЗУ) и цифроаналоговый преобразователь (ЦАП). Обычно каждый из этих функциональных узлов выполняется в виде отдельной ИМС. Схема преобразования цифровой последовательности в синусоидальный сигнал приведена на рис 3.3.4. Адресная шина ПЗУ подключается к выходам двоичного счетчика СТ2, вход которого соединен с выходом УДЧ модулятора, либо к адресной шине микропроцессора УПС. В ячейки ПЗУ в цифровом виде заносятся значения напряжений синусоиды, соответствующие своим фазовым углам ∆φ (см. рис. 3.3.3) Количество слов, хранимых в ПЗУ, равно kст . Емкость ПЗУ можно уменьшить до kст/4, при этом существенно усложнится схема формирования адресов. Разрядность слова ПЗУ np зависит от точности воспроизведения ступенчатого напряжения. На практике достаточно принять np=8 с учетом знакового разряда, что обеспечивает погрешность формирования напряжения менее 1%.

Рисунок 3.3.4 – Цифровой формирователь синусоидальных сигналов на основе ПЗУ

В микропроцессорных УПС адресации ПЗУ осуществляется программным способом. Время нахождения адреса ta на соответствующей шине микропроцессора определяется программой и зависит от частоты формируемой синусоиды fi вых выходного сигнала

ta = 1/( fi вых kст) (3.3.4)

3.4 Разработка приемной части УПС

Структурная схема приемной части УПС изображена на рисунке 3.4.1

Рисунок 3.4.1 – Структурная схема приемной части УПС

Демодуляторы ЧМ-сигналов современных систем передачи данных строятся преимущественно на цифровых элементах. Входной сигнал в схеме демодулятора преобразуется в прямоугольную последовательность импульсов, постоянная составляющая которой зависит от частоты демодулируемого колебания. Помехоустойчивость таких демодуляторов несколько ниже, чем у частотных дискриминаторов с колебательными контурами. Высокая стабильность параметров схемы, отсутствие необходимости регулировок в процессе эксплуатации обусловили широкое применение их на практике.

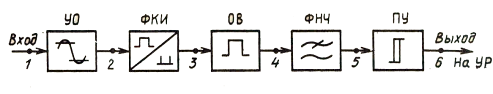

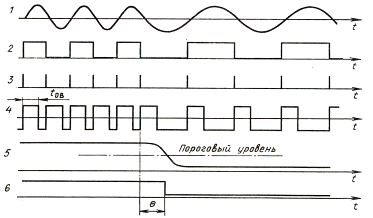

Функциональная схема одного из вариантов ЧМ – демодулятора приведена на рисунке 3.4.2. В её состав входит усилитель-ограничитель (УО) с нулевым порогом ограничения, формирователь коротких импульсов в моменты переходов входного сигнала через нуль (ФКИ), одновибратор (ОВ), фильтр низких частот (ФНЧ) и пороговое устройство (ПУ). Временная диаграмма, иллюстрирующая работу ЧМ- демодулятора, показана на рис. 3.4.3. Импульс фиксированной длительности формируется ОВ в момент пресечения входным сигналом нулевого уровня. Длительность импульса должна быть меньше длительности периода верхней частоты демодулируемого сигнала. Из прямоугольной последовательности импульсов ОВ ФНЧ выделяет постоянную составляющую, которая преобразуется ПУ в посылки постоянного тока.

|

Рисунок 3.4.3 – Временные диаграммы ЧМ–демодулятора

Для формирования коротких импульсов целесообразно использовать схему цифрового дифференциального выпрямителя (см. рис 3.4.4). В качестве ОВ можно применить схему ждущего мультивибратора, выполненного на логических элементах или на основе счетчика импульсов с предварительной установкой. Принцип действия ОВ на основе счетчика заключается в том, что импульсом нулевого пересечения в счетчик заносится число, в результате чего на его выходе появится положительный потенциал, длительность которого определяется выбором заносимого в счетчик числа, емкостью счетчика и частотой следования тактовых импульсов. Схема ОВ на основе счетчика будет более громоздкой, но стабильность параметров импульса значительно выше.

Рисунок 3.4.4 - Схема цифрового дифференциального выпрямителя

Параметры ОВ выбираются таким образом, чтобы при поступлении на вход демодулятора сигнала с частотой

fср = (fнч + fвч)/2 (3.4.1)

напряжение на его выходе имело симметричную форму (меандр), здесь fнч и fвч – нижняя и верхняя частоты демодулируемого сигнал. Длительность импульса ОВ равна

tов = 1/ (2 fср) (3.4.2)

Как видно из временной диаграммы, абсолютная величина краевых искажений сигналов Θ на выходе демодулятора составляет примерно 1.5tов. Задавая допустимую относительную величину краевых искажений δдоп, можно определить требования к средней частоте ЧМ – сигнала. Так как

δдоп ≤ 1.5tов / τ0 = 1.5В/(2 fср) (3.4.3)

то

fср ≥ 0.75В/ δдоп (3.4.4)

Для уменьшения вносимых демодулятором искажений нужно увеличить среднюю частоту ЧМ – сигнала, поэтому такой демодулятор следует включать совместно с преобразователем частоты. В процессе расчета параметров ЧМ – демодулятора необходимо рассчитать частоту преобразователя fпч, длительность импульса одновибратора и параметры ФНЧ.

Рассчитаем параметры ЧМ – демодулятора для прямого канала, если fнч = 1030 Гц, fвч = 1970 Гц, скорость модуляции В=600 бод. Допустимая величина краевых искажений δдоп = 5%

Из (3.4.4) найдём требуемую среднюю частоту ЧМ – сигнала, поступающего на вход демодулятора:

fср ≥ 0.75*600/ 0.05 = 9000Гц

Частота модуляции промежуточного преобразователя частоты определяется из соотношения

fпч = fдоп ± (fнч + fвч)/2 = 15±1.5 кГц (3.4.5)

Плюс берется в случае выделения в преобразователе нижней боковой составляющей, а минус – верхней. Принимаем fпч = 10.5 кГц. Длительность импульса одновибратора находим из (4.6) с учетом того, что fср = fср, тогда

tов = 1/ (2 *9000) = 5.6*10-5 с.

Параметры ЧМ – демодулятора для обратного канала, если fнч = 360 Гц, fвч = 420 Гц, скорость модуляции В=75 бод. Допустимая величина краевых искажений δдоп = 5%

Из (3.4.4) найдём требуемую среднюю частоту ЧМ – сигнала, поступающего на вход демодулятора:

fср ≥ 0.75*75/ 0.05 = 1125Гц.

Частота модуляции промежуточного преобразователя частоты определяется из соотношения

fпч = fдоп ± (fнч + fвч)/2 = 1125±390 кГц.

Плюс берется в случае выделения в преобразователе нижней боковой составляющей, а минус – верхней. Принимаем fпч = 1515 кГц. Длительность импульса одновибратора находим из (4.6) с учетом того, что fср = fср, тогда

tов = 1/ (2 *1125) = 4.4*10-4 с.

Для правильной фиксации единичных элементов при наличии краевых искажений или дроблений будем использовать регистрирующее устройство (УР) на основе принципа стробирования.

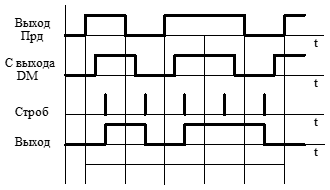

Метод стробирования заключается в том, что значение единичного элемента проверяется в момент времени, наименее подверженный искажениям, то есть в середине посылки, путем подачи стробирующего импульса (строба) на ключевые элементы. В качестве стробов используется последовательность коротких импульсов с периодом следования τ0, вырабатываемая специальной схемой синхронизации. При использовании в качестве регистратора синхронного D - триггера схема регистрации имеет вид, изображенный на рисунке 3.4.5. Временная диаграмма функционирования устройства регистрации со стробированием показана на рисунке 3.4.6.

Рисунок 3.4.5 – Схема регистрации единичных элементов стробированием

Рисунок 3.4.6 – Временные диаграммы регистрации стробированием

4 Разработка Устройства защиты от ошибок

4.1 Выбор способа защиты от ошибок

Основным способом повышения верности передачи дискретных сообщений является введение в передаваемую последовательность избыточности с целью обнаружения и исправления ошибок в принятой информации. Все устройства защиты от ошибок (УЗО) делятся на две группы: симплексные (без обратной связи) и дуплексные (с обратной связью).

В симплексных УЗО повышение верности передачи может быть достигнуто тремя способами: путем многократного повторения символов; одновременной передачей одной и той же информации по нескольким каналам; применением кодов исправляющих ошибки.

К дуплексной группе УЗО относятся устройства, в которых повышение верности передаваемой информации достигается за счет введения обратной связи. Они в свою очередь делятся на системы с решающей (РОС), информационной (ИОС) и комбинированной (КОС) обратной связью. Сущность повышения верности в этих системах состоит в том, что при обнаружении искажений в передаваемом сообщении происходит запрос блока, в котором находятся один или несколько неправильно принятых знака. В системах с РОС передаваемые данные кодируются избыточными кодами, позволяющими обнаруживать одиночные ошибки или пачки (группы) ошибок. Решение о необходимости повторения блока информации, в котором обнаружена ошибка, принимается приемником на основании анализа поступившей последовательности. В случае обнаружения в принятом блоке ошибок он стирается и по каналу обратной связи (ОС) приемная станция посылает сигнал «Запрос», на основании которого передатчик повторно выдает этот же блок. При безошибочном приеме блока данные поступают потребителю, а по каналу ОС передается сигнал «Подтверждение».

В УЗО с ИОС нет необходимости вводить избыточность в передаваемые данные. Двоичная последовательность, зафиксированная приемником, запоминается и затем по каналу ОС передается вся или в виде укороченной кодовой комбинации, содержащей определенные признаки всей последовательности, на передающую сторону. Полученная по каналу ОС информация анализируется предыдущей станцией, которая по результатам анализа принимает решение о передаче следующего блока либо о повторении ошибочно принятого. Это решение сообщается на приемную сторону и на его основании полученная информация передается потребителю или стирается.

УЗО с КОС представляют собой сочетание информационной и решающей ОС. В них решение о необходимости повторной передачи может приниматься как на передающей, так и на приемной сторонах , а по каналу обратной связи могут передаваться информационные элементы или сигналы «Запрос» или «Подтверждение».

Одной из главных задач проектирования УЗО является выбор способа защиты от ошибок, который при минимальных затратах обеспечит выполнение поставленных требований. Под затратами подразумевается не только стоимость аппаратуры, но и необходимые полоса частот (требуемое число каналов связи), время на передачу сообщения, а также стоимость обслуживания устройства в процессе эксплуатации.

При наличии дуплексных каналов связи в большинстве случаев целесообразно использовать УЗО с ОС. Устройства с информационной обратной связью позволяют обнаруживать ошибки практически любой кратности, но к каналу обратной связи предъявляют такие же требования, как и к прямому. Поэтому УЗО с ИОС наиболее эффективно могут быть использованы при скоростях менее 600 бит/с. Если же передача данных ведется на скоростях 600 и более бит/с, то эффективность использования канала связи с УЗО с ИОС снижается и в этом случае для повышения помехоустойчивости передачи символов следует применять УЗО с РОС либо с КОС.

Для данного курсового проекта при анализе технических параметров было выбрано УЗО с РОС.

Передача сообщений от отправителя к получателю обычно осуществляется поблочно, длина которого определяется информационной частью, и числом служебных и проверочных символов.

Обмен данными будет проходить следующим образом:

- сначала ООД загружает в АПД весь массив данных, которые будут храниться в оперативной памяти передающего узла;

- передающая сторона берет очередной блок данных, вычисляет проверочные символы для данного блока, дополняет его ими, и в начало блока дописывает синхронизирующую комбинацию длиной 8 бит, имеющую формат 01010101, для того, чтобы приемная сторона могла засинхронизировать свои функциональные блоки. Проверочная комбинация имеет длину 16 бит. Текущий блок хранится в памяти до получения от приемника сигнала о правильности приема.

- на приемной стороне, полученный блок декодируется, проверяется на наличие ошибок, и результат проверки отправляется на передающую сторону виде подтверждения приёма, либо запроса на повторную передачу блока.

- приемная сторона, получив подтверждение правильного приема, осуществляет обработку следующего блока, в случае же запроса на повтор передачи в канал повторно отправляется текущий блок.

- процесс повторяется, пока не будут переданы все информационные блоки.

4.2 Разработка формата сообщения

В процессе разработки СПД необходимо УЗО спроектировать так, чтобы обеспечить требуемую помехоустойчивость при максимально эффективной скорости передачи данных. Помехоустойчивость и эффективная скорость передачи данных зависят от избыточности передаваемых сообщений, причем с увеличением избыточности помехоустойчивость возрастает, а эффективная скорость падает.

По техническим данным при выбранном УПС избыточность передаваемого сообщения может быть велика, а с ее увеличением, как уже говорилось, помехоустойчивость повышается. В таком случае наличие в канале связи пакета ошибок приводит к снижению эффективной скорости передачи. Допустим, что пакеты ошибок являются независимыми событиями, каждый пакет вызывает повторную передачу только одного блока сообщения и интервал между пакетами ошибок в среднем превышает длину блока. В таком случае в качестве формулы для расчета эффективной скорости СПД с решающей обратной связью можно взять

![]() (4.2.1)

(4.2.1)

заменив в ней соответственно вероятность ошибочного приема элемента Р0 на вероятность появления пачки ошибок РПО = 8×10-5.

Для повышения эффективности передачи данных метод кодирования выбирается таким образом, чтобы заданная помехоустойчивость обеспечивалась при минимальном числе проверочных элементов r, то же относится и к служебным знакам. Величина r зависит от используемого кода, который выбирается исходя из требуемой вероятности ошибочного приема кодовой комбинации Ркк и характера ошибок в дискретном канале.

Оптимальная величина блока информации может быть найдена путем построения зависимости Vэф=Ψ(nб). Приемлемой эффективной скоростью считается:

Vэф= (0,90![]() 0,95) V бит/с. (4.2.2)

0,95) V бит/с. (4.2.2)

Vэф_min=V [1 - Po nб / (1 - Po nб)] [1- (r + nсл) / nб] (4.2.3)

где Ро – вероятность ошибочного приема;

nб – длина блока;

r – число проверочных бит;

nсл – число служебных бит, используемых для введения признака начала блока.

Сообщение имеет следующие параметры:

nсл = 8;

r = 16.

Задавая значения длины блока от 100 до 700 с шагом 50, построим график зависимости относительной эффективной скорости передачи ![]() от длины блока, учитывая, эффективная скорость должна находиться в следующих пределах:

от длины блока, учитывая, эффективная скорость должна находиться в следующих пределах:

![]() (бит/с) (4.2.4)

(бит/с) (4.2.4)

В таблице 4.2.1 приведены результаты расчетов относительной скорости при разных длинах блока, на рисунке 4.2.1 показан график, построенный по результатам расчетов.

Рисунок 4.2.1 - График зависимости относительной эффективной скорости передачи информации от длины блока

Таблица 4.2.1 – Относительная эффективная скорость передачи

№ п/п |

Длина блока, бит |

Относительная эффективная скорость передачи |

| 1 | 100 | 0.754 |

| 2 | 150 | 0.83 |

| 3 | 200 | 0.866 |

| 4 | 250 | 0.886 |

| 5 | 300 | 0.897 |

| 6 | 350 | 0.905 |

| 7 | 400 | 0.909 |

| 8 | 450 | 0.911 |

| 9 | 500 | 0.912 |

| 10 | 550 | 0.912 |

| 11 | 600 | 0.912 |

| 12 | 650 | 0.91 |

| 13 | 700 | 0.908 |

Видно, что максимальная скорость передачи данных получателю имеем место при nб =500 бит. На практике рекомендуется использовать информационные блоки длиной в битах, кратной степени числа 2. Поэтому выбираем nб = 512 бит.

Поскольку общее число служебных битов равно 24, то длина информационного блока будет равна 488 бит.

Рассчитаем количество передаваемых блоков за сеанс. Это составит 1024 × 20 / 488 = 42 блока, где 1024 × 20 – количество передаваемой информации за сеанс, а 488 – число информационных бит в блоке.

Обработка информационных блоков, определение контрольной суммы на передающей стороне, формирование полного передаваемого блока, декодирование его на приемной стороне, решение о правильности передачи блока и другие сопутствующие информационные расчеты выполняются программно микропроцессорным блоком. Вследствие этого нет необходимости аппаратно реализовывать устройство защиты от ошибок.

5 Алгоритм функционирования передающей части АПД

Работа передатчика АПД начинается после подачи на него питания. В блоке начальной установки формируется импульс, устанавливающий все функциональные блоки в исходное состояние. После этого процессор начинает чтение первой команды из ПЗУ, выставляя на шину адреса/данных адрес FFFF0.

Прежде всего, процессор тестирует самого себя, память, программирует микросхему ППИ. В случае обнаружения сбоев процессор выдает в определенный порт единицу, тем самым зажигая индикатор неисправности, и прекращает работу. При отсутствии неисправностей аппаратура готова к приему данных.

После этого осуществляется автоматическое установление соединения при помощи устройства автоматического вызова. После установления соединения ООД переводит цепь 4 – «ООД готово» в состояние включено. По этому сигналу происходит переключение абонентской линии с устройства автоматического вызова на выход модема, в который посылает в линию гармонический сигнал, соответствующий уровню логической единицы-1300 Гц в течение 40 мс.

После включения цепи 4 АПД переводит цепь 5 – «АПД готово» в состояние включено. АПД переключается в режим «Данные» и включает цепь 9 – «Управление передатчика АПД».

В ответ на этот сигнал ООД включает цепь 10 – «Управление источника ООД». Состояние «включено» этой цепи указывает, что в цепях 12–19 выставлены данные.

После включения этой цепи УУ вырабатывает сигнал, по которому данные из ООД через стык 3 записываются в оперативную память АПД. Процесс загрузки данных продолжается до тех пор, пока не будет загружен весь блок данных, объемом 20 кБит.

После этого происходит переключение абонентской линии с устройства автоматического вызова на выход модема, который посылает в линию гармонический сигнал, соответствующий уровню логической единицы – 1300 Гц в течение 40 мс.

Начинается поблочный процесс передачи данных через канал связи.

Блок состоит из трех частей: синхронизирующая последовательность 01010101, информационная часть 488 бит (61 байт), и проверочные символы.

Проверочные символы формируются на основе следующего алгоритма.

Первые 8 бит представляют собой алгебраическую сумму первых 32 информационных байт без переноса, а следующие 8 бит – алгебраическую сумму оставшихся 29 информационных байт без переноса.

Микропроцессор формирует блок данных указанного формата и через Модулятор прямого канала отсылает в канал. При этом сформированный блок сохраняется в оперативной памяти АПД. После этого начинается опрос обратного канала. При получении сигнала об ошибочности приема блока на приемной стороне, происходит его повторная выдача в канал связи. Процесс повторяется до тех пор, пока не будет получен сигнал о корректности приема данного блока. После чего формируется следующий блок данных, и процесс повторяется до тех пор, пока не будет передан весь массив данных, объемом 20 кБит. Так как размер информационного блока составляет 488 бит, то необходимо передать 42 блока (см. пункт 4.2).

После окончания передачи данных АПД отключает цепь 5, на основании анализа которой ООД определяет, что передача завершена. ООД переводит цепь 4 в выключенное состояние и процесс передачи данных заканчивается.

Вышеописанный алгоритм функционирования АПД реализуется на основе программы, хранимой в ПЗУ передающей части АПД. Текст программы приведен в приложении В. Блок-схема процесса функционирования передающей части приведена в приложении А.

6 Алгоритм функционирования приемной части АПД

Работа приемника АПД начинается после подачи на него питания. В блоке начальной установки формируется импульс, устанавливающий все функциональные блоки в исходное состояние. После этого процессор начинает чтение первой команды из ПЗУ, выставляя на шину адреса/данных адрес FFFF0.

Прежде всего, процессор тестирует самого себя, память, программирует микросхему ППИ. В случае обнаружения сбоев процессор выдает в определенный порт единицу, тем самым зажигая индикатор неисправности, и прекращает работу. При отсутствии неисправностей аппаратура готова к приему данных.

Процесс передачи данных по каналу начинается после автоматического установления соединения с передающей станцией. УПС после принятия сигнала вызова включает цепь 125 «Индикатор вызова».

В ответ на этот сигнал ООД включает цепь 108.2 «ООД готово». УПС переключает абонентскую линию с приемника тонального вызова на УПС и в линию посылает ответный сигнал частотой 2100 Гц. После окончания передачи ответного сигнала УПС включает цепь 107 «АПД готово».

Через 5-15 мс после приема несущей срабатывает детектор линейного сигнала прямого канала связи и цепь 109 «Детектор принимаемого линейного сигнала канала данных» переходит во включенное состояние, разрешая работу демодулятора прямого канала.

Из канала связи побитно принимается блок данных длиной 512 бит.

Первые восемь бит служат для синхронизации узлов приемника, и, как было описано в разделе 5, представляют собой последовательность 01010101.

На основе следующих 488 бит, представляющих собой информационные данные, рассчитываются проверочные символы и сравниваются с принятыми из канала связи. Если устанавливается, что блок данных принят корректно, то увеличивается на единицу счетчик принятых блоков, и информационные биты заносятся в соответствующее место в оперативной памяти приемника АПД. Если определяется, что блок был принят неправильно, то в канал обратной связи посылается запрос на повторную передачу блока, а текущий принятый блок стирается. Процесс повторяется до тех пор, пока текущий блок не будет корректно передан по каналу связи.

Так как количество блоков, которые необходимо принять, заранее известно, то процесс передачи будет продолжаться до тех пора, пока не будут корректно приняты все 42 блока.

После завершения приема УУ включает цепь 104 «Принимаемые данные» и побитно выдаёт полученные данные ООД через стык 2.

После окончания выдачи данных, цепь 104 отключается, и цепь 107 «АПД готово» переводится в состояние выключено.

Вышеописанный алгоритм функционирования АПД реализуется на основе программы, хранимой в ПЗУ приемной части АПД. Текст программы приведен в приложении Г. Блок-схема процесса функционирования приемной части приведена в приложении Б.

7 Разработка функциональной схемы

7.1 Передающая часть АПД

Основой передающей части АПД является микропроцессорный блок, осуществляющий чтение входной информации, формирование блоков данных, расчёт проверочных символов, формирование управляющих сигналов, входных и выходных сигналов стыка С3, обработку сигналов обратного канала и другие действия.

Микропроцессорный блок построен на микропроцессорном комплект КР580. Данный комплект при частоте работы микропроцессора 2-2.5 МГц обеспечивает достаточную скорость обработки данных. Небольшой набор необходимых микросхем обеспечивают невысокую стоимость блока, компактность установки и простоту эксплуатации.

Микропроцессор КР580ВМ80А, на схеме элемент DD5, имеет 16-ти разрядную шину адреса и 8-ми разрядную шину данных, что позволяет подключить 64 килобайта памяти.

Для формирования импульсов начальной установки микросхем, тактовых импульсов, импульсов строба, служит тактовый генератор, представленный на схеме элементом DD1.

Буферные регистры DD6 и DD7 служат для удержания сигналов адресной шины, так как логика работы микропроцессора подразумевает такой принцип работы с адресной шиной, при котором сигнал адреса появляется на первом такте машинного цикла одновременно с сигналом синхронизации SYNC и далее микропроцессор отключается от этой шины. И чтобы адрес удерживался на шине в течение машинного цикла, он записывается в буферные регистры.

Так как микропроцессор не имеет отдельных выходов для сигналов чтения/записи памяти и внешних устройств, то операцию, которую микропроцессор будет выполнять в данном машинном цикле, обозначает слово состояния, которое выдаётся микропроцессором на шину данных в начале машинного цикла и сопровождается сигналом STSTB(Status Strobe). Для декодирования слова состояния и для формирования сигналов чтения/записи предназначен регистр слова состояния процессора DD8.

Для хранения программы функционирования устройства предназначена микросхема ПЗУ DD10 емкостью 24 КБайта.

Обрабатываемые данные, состояние блока, текущая информация хранится в оперативной памяти, реализованной на микросхеме статической памяти DD11. Объём оперативной памяти – 40 Кбайт.

Так как адреса ОЗУ и ПЗУ идут на одну шину адреса, то для разделения обращений предназначен дешифратор DD12, который на основе анализа адресных линий A13-A15 определяет, к какой области памяти производит обращение микропроцессор.

Логический элемент “И” (DD13.1) предназначен для разрешения работы дешифратора адреса DD12 в тот момент, когда происходит обращение к памяти.

Информация от ООД передаётся через стык С3. Для формирования сигналов стыка, а также для обработки сигналов прямого и обратного каналов предназначен параллельный приемо-передатчик DD9. Так как сигналы стыка двуполярные, а сигналы логического нуля и единицы, обрабатываемые схемой – однополярные, то для преобразования однополярных в двуполярные и обратно предназначены элементы DD2-DD4.

Перечень цепей стыка С3 представлен ниже:

1- защитное заземление;

2 - общий обратный провод

3 - индикатор вызова

4 - ООД готово

5 - АПД готова

7 - источник ООД готов

8 - передатчик АПД готов

9 - управление передатчика АПД

10 - управление источника ООД

12-19 - данные источника ООД

21 - получатель ООД готов

22 - приемник АПД готов

23 - управление получателя ООД

24 - управление приемника АПД

25 - ошибка получателя ООД

26-33 – данные приемника АПД

35 - аварийная сигнализация

Часть из этих контактов в данной схеме не используется.

Для обработки данных канального уровня, то есть для модуляции/демодуляции сигналов, регистрации единичных элементов, синхронизации используются следующие блоки:

дифференциальная система ДС1, разделяющая сигналы прямого и обратного каналов, поступающих через стык С1;

усилители прямого и обратного каналов УСвых и УСвх соответственно;

блок модуляторов прямого канала (МПрК), состоящий из двух модуляторов М1 и М2, полосовых фильтров ПФ1 и ПФ3, и задающих генераторов Г1 и Г2.

Параметры функциональных узлов были рассчитаны в пункте 3.1 и 3.2:

полоса пропускания ПФ1 – (2530-3470) Гц, ПФ3 – (1030-1970)Гц

частота генератора Г1 – 3000Гц, Г2- 1500Гц

схема построения модуляторов М1 и М2 рассмотрена в пункте 3.3;

блок демодулятора обратного канала (ДМОбрК), состоящий из полосового фильтра ПФ2, имеющего полосу пропускания (360-420) Гц, усилителя-ограничителя УО1, формирователя коротких импульсов ФК1, одновибратора ОВ1, фильтра низких частот ФНЧ1 и порогового устройства ПУ1. Расчёты параметров структурных блоков демодулятора и принцип их построения были рассмотрены в пункте 3.4

Для правильной регистрации единичных элементов используется регистрирующее устройство (РУ) на основе принципа стробирования, схема построения которой рассмотрена в пункте 3.4. Для формирования стробирующих импульсов используется устройство синхронизации (УС).

Основой приемной части АПД является микропроцессорный блок, осуществляющий чтение входной информации, формирование блоков данных, расчёт проверочных символов, формирование управляющих сигналов, входных и выходных сигналов стыка С2, обработку сигналов обратного канала и другие действия.

Микропроцессорный блок построен на микропроцессорном комплекте КР580. Данный комплект при частоте работы микропроцессора 2-2.5 МГц обеспечивает достаточную скорость обработки данных. Небольшой набор необходимых микросхем обеспечивают невысокую стоимость блока, компактность установки и простоту эксплуатации.

Микропроцессор КР580ВМ80А, на схеме элемент DD2, имеет 16-ти разрядную шину адреса и 8-ми разрядную шину данных, что позволяет подключить 64 килобайта памяти.

Для формирования импульсов начальной установки микросхем, тактовых импульсов, импульсов строба, служит тактовый генератор, представленный на схеме элементом DD1.

Буферные регистры DD3 и DD4 служат для удержания сигналов адресной шины, так как логика работы микропроцессора подразумевает такой принцип работы с адресной шиной, при котором сигнал адреса появляется на первом такте машинного цикла одновременно с сигналом синхронизации SYNC и далее микропроцессор отключается от этой шины. И чтобы адрес удерживался на шине в течение машинного цикла, он записывается в буферные регистры.

Так как микропроцессор не имеет отдельных выходов для сигналов чтения/записи памяти и внешних устройств, то операцию, которую микропроцессор будет выполнять в данном машинном цикле, обозначает слово состояния, которое выдаётся микропроцессором на шину данных в начале машинного цикла и сопровождается сигналом STSTB(Status Strobe). Для декодирования слова состояния и для формирования сигналов чтения/записи предназначен регистр слова состояния процессора DD5.

Для хранения программы функционирования устройства предназначена микросхема ПЗУ DD8 емкостью 24 КБайта.

Обрабатываемые данные, состояние блока, текущая информация хранится в оперативной памяти, реализованной на микросхеме статической памяти DD10. Объём оперативной памяти – 40 Кбайт.

Так как адреса ОЗУ и ПЗУ идут на одну шину адреса, то для разделения обращений предназначен дешифратор DD9, который на основе анализа адресных линий A13-A15 определяет, к какой области памяти производит обращение микропроцессор.

Логический элемент “И” (DD6.1) предназначен для разрешения работы дешифратора адреса DD9 в тот момент, когда происходит обращение к памяти.

Информация от АПД к ООД передаётся через стык С2. Для формирования сигналов стыка, а также для обработки сигналов прямого и обратного каналов предназначен параллельный приемо-передатчик DD11. Так как сигналы стыка двуполярные, а сигналы логического нуля и единицы, обрабатываемые схемой – однополярные, то для преобразования однополярных в двуполярные и обратно предназначены элементы DD7.

Перечень цепей стыка С2 представлен ниже:

102 - сигнальное заземление

103 - передаваемые данные

104 - принимаемые данные

105 - запрос передачи

106 - готов к передаче

107 - АПД готово

108.1 - подсоединить АПД к линии

108.2 - ООД готово

109 - детектор принимаемого линейного сигнала канала данных

113 - синхронизация элементов передаваемого сигнала (от ООД)

114 - синхронизация элементов передаваемого сигнала (от АПД)

115 - синхронизация элементов принимаемого сигнала (от АПД)

118 - передаваемые сигналы обратного канала

119 - принимаемые сигналы обратного канала

120 - включить линейный сигнал обратного канала

121 - обратный канал готов

122 - детектор принимаемого линейного сигнала обратного канала

125 - индикатор вызова

128 - синхронизация элементов принимаемого сигнала (от ООД)

Часть из этих контактов в данной схеме не используется, и поэтому была выбрана 9-ти контактная реализация стыка С2.

Для обработки данных канального уровня, то есть для модуляции/демодуляции сигналов, регистрации единичных элементов, синхронизации используются следующие блоки:

дифференциальная система ДС1, разделяющая сигналы прямого и обратного каналов, поступающих через стык С1;

усилители прямого и обратного каналов УСвых и УСвх соответственно;

блок демодулятора прямого канала (ДМПрК), состоящий из модулятора М2, полосовых фильтров ПФ1 и ПФ3 – (1030-1970)Гц и задающего генератора Г2 – 1500Гц, усилителя-ограничителя УО1, формирователя коротких импульсов ФК1, одновибратора ОВ1, фильтра низких частот ФНЧ1 и порогового устройства ПУ1. Расчёты параметров структурных блоков демодулятора и принцип их построения были рассмотрены в пункте 3.4;

для правильной регистрации единичных элементов используется регистрирующее устройство (РУ) на основе принципа стробирования, схема построения которой рассмотрена в пункте 3.4. Для формирования стробирующих импульсов используется устройство синхронизации (УС);

блок модулятора обратного канала (МОбрК), состоящий из модулятора М1, полосового фильтра ПФ2 и задающего генератора Г1.

Параметры функциональных узлов были рассчитаны в пункте 3.1 и 3.2:

полоса пропускания ПФ2 – (360-420) Гц;

частота генератора Г2 – 420Гц;

схема построения модулятора М1 рассмотрена в пункте 3.3.

В ходе выполнения курсового проекта была разработана аппаратура передачи данных в соответствии с заданным вариантом. Произведен расчет основных параметров УПС и разработана его функциональная схема. В связи с малой скоростью передачи и небольшим объемом данных, в качестве УЗО была выбрана решающая обратная связь. АПД реализована на базе микропроцессорной серии КР580, что обеспечило простоту и малую стоимость её реализации.

Список используемой литературы

Аверьянов Н.Н., Березенко А.И., Борщенко Ю.И. и др. Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Справочник: В 2 т. - Минск.: Радио и связь, т. 1, 1988. – 368 с.

Лебедев О.Н. Микросхемы памяти и их применение. - М.: Радио и связь, 1990. - 160 с.

Хвощ С.Т. и др. Микропроцессоры и микро-ЭВМ в системах автоматического управления: Справочник. - Л.: Машиностроение, 1987.-640 с.

Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. - М.: Радио и связь, 1989. 288 с.

Чернега В.С., Василенко В.А., Бондарев В.Н. Расчет и проектирование технических средств обмена и передачи информации. - М.: Высшая школа, 1990.-224 с.

Чернега В.С. Конспект лекций по курсу «Системы передачи данных» ГОСТ 20855-83