| Скачать .docx |

Курсовая работа: Створення мікропроцесорної системи обробки інформації

Содержание

Вступ

1. Розробка структурної схеми системи

2. Розробка І опис принципової схеми системи

2.1 Розробка мікропроцесорного блоку

2.2 Розробка блоку пам’яті (ОЗП і ПЗП)

2.3 Інтервальний таймер

2.4 Аналого-цифровий перетворювач (АЦП)

2.5 Контролер клавіатури і індикації

2.6 Адаптер послідовного інтерфейсу Intel 8251

Висновки

Вступ

Сьогодні розвиток комп’ютерних технологій проходить досить стрімко.

Більшість цифрових систем будується на мікропроцесорах або на мікроконтролерах. Управління різними технологічними процесами проходить за допомогою мікропроцесорних систем або технологічних операцій. Дані системи універсальні, так як вони мають дуже високу швидкодію та достатню розрядність для обробки інформації на виробництві.

Мікропроцесор являє собою функціонально закінчений пристрій, що складається із однієї або декількох програмно керуємих ВІС, та слугує для виконання операцій з обробки інформації та керування обчислювальним процесом. До числа внутрішніх схем мікропроцесора відносяться багаторозрядні регістри, рівнобіжні тракти даних, буфери для підключення зовнішніх пристроїв, багатофункціональні схеми, логічні схеми синхронізації і керування.

Центральне місце в структурі мікропроцесорних приладів займає мікропроцесор, який виконує арифметичні та логічні операції над даними, програмне керування процесом обробки інформації, а також організує взаємодію усіх пристроїв, що входять до складу системи.

Багатофункціональні схеми призначені для реалізації простих арифметичних і логічних дій над двійковими числами, що знаходяться в регістрах процесора, і пересилок даних як усередині процесора, так і між ним і зовнішніми пристроями.

Розвиток інтегральної технології і схемотехніки цифрових електронних схем призвів до появи інтегральних мікросхем із великою і дуже великою ступенями інтеграції (ВІС і ДВІС), що містять на однім кристалі (в однім корпусі) декілька десятків тисяч, а в останніх розробках сотні тисяч елементарних транзисторів. На основі таких схем створюються мікропроцесори функціонально закінчені, що управляються збереженою в пам'яті програмою, це (здебільшого малорозрядні) пристрої опрацювання цифрової інформації, виконані у виді однієї або декількох ВІС або ДВІС.

Мікропроцесорні засоби використовуються у виді мікропроцесорних комплектів інтегральних мікросхем, що мають єдине конструктивно-технологічне виконання і призначених для спільного застосування.

Мікропроцесорний комплект крім самого мікропроцесора містить мікросхеми, що підтримують функціонування мікропроцесора і розширюють його логічні можливості.

Робота мікропроцесора складається з наступних кроків:

спочатку вибирається команда, потім логічна схема її декодує, після чого здійснюється виконання цієї команди. Також відбувається обмін інформацією з зовнішніми пристроями, які приєднані до мікропроцесора.

Завданням цієї курсової роботи є створення мікропроцесорної системи обробки інформації на основі мікроконтролера ATmega128 та інших мікросхем, згідно варіанту.

1. Розробка структурної схеми системи

Структурна схема даної системи повинна мати наступні компоненти: мікроконтролер, ОЗУ, ПЗУ, АЦП, контролер клавіатури й індикації, клавіатуру та індикацію, iнтервальний таймер (згідно із завдання).

Увесь масив пам’яті поділено на дві області: ОЗП і ПЗП. В ПЗП зберігаються програми вводу і виводу інформації. В ОЗП розміщуються дані, які необхідно тимчасово зберігати у процесі обробки програми. Для забезпечення тимчасових затримок, отримання одиничних імпульсів заданої тривалості та генерації послідовностей імпульсів служить програмований iнтервальний таймер (Т).

Рис.1. - Структурна схема пристрою.

ОЗП - оперативний запам'ятовувальний пристрій

ПЗП - постійний запам'ятовувальний пристрій

МК - мікроконтролер

ККіІ - контролер індикації й клавіатури

ША - шина адреси

ШД - шина даних

ШК - шина керування

АЦП - аналого-цифровий перетворювач

T - таймер

ВЗ - вузол збросу

К - клавіатура

І - індикатор

ПІ - послідовний інтерфейс

2. Розробка І опис принципової схеми системи

Розробка принципової схеми буде проводитись кількома етапами. Буде розроблено функціональні блоки які треба буде зв`язати між собою шинами. Вибір елементів буде проводитись згідно завданню. Для побудови структурної схеми необхідно точно визначити необхідні вузли системи і зв'язку між ними.

2.1 Розробка мікропроцесорного блоку

Основний елемент системи - мікроконтролер ATmega128, ATmega128L 8-розрядний AVR-мікроконтролер з внутрісистемно програмованою флэш-пам'яттю ємкістю 128 кбайт

Відмітні особливості:

Високопродуктивний, малопотужний 8-розрядний AVR-мікроконтролер Розвинена RISC-архітектура.

133 могутніх інструкцій, більшість з яких виконуються за один машинний цикл.

32 8-разр. регістрів загального призначення + регістри управління вбудованою периферією.

Повністю статична робота.

Продуктивність до 16 млн. операцій в секунду при тактовій частоті 16 Мгц

Вбудований умножаючий пристрій виконує множення за 2 машинних циклу.

Незалежна пам'ять програм і даних.

Зносостійкість 128-ми кбайт внутрісистемно перепрограмміруємой флэш-пам'яті: 1000 циклів запис/стирання.

Опціональний завантажувальний сектор з окремим програмованим захистом.

Внутрішньосистемне програмування вбудованою завантажувальною програмою.

Гарантована двухоперационность: можливість читання під час запису

Зносостійкість 4 кбайт ЕСППЗУ: 100000 циклів запис/стирання

Вбудоване статичне ОЗУ ємкістю 4 кбайт

Опціональна можливість адресації зовнішньої пам'яті розміром до 64 кбайт.

Програмований захист коду програми.

Інтерфейс SPI для внутрішньосистемного програмування.

Інтерфейс JTAG (сумісність із стандартом IEEE 1149.1).

Граничне сканування відповідно до стандарту JTAG.

Обширна підтримка функцій вбудованої відладки.

Програмування флэш-пам'яті, ЕСППЗУ, біт конфігурації і захисту через інтерфейс JTAG.

Відмітні особливості периферійних пристроїв.

Два 8-разр. таймера-лічильника з роздільними переддільниками і режимами порівняння.

Два розширених 16-разр. таймера-лічильника з окремими переддільниками, режимами порівняння і режимами захоплення.

Лічильник реального часу з окремим генератором.

Два 8-разр. каналів ШИМ.

6 каналів ШИМ з програмованим дозволом від 2 до 16 розрядів

Модулятор виходів порівняння.

8 мультіплексованих каналів 10-розрядного аналогово-цифрового перетворення.

8 несиметричних каналів.

7 диференціальних каналів

2 диференціальних каналу з вибірковим посиленням з 1x, 10x і 200x

Двухпроводної послідовний інтерфейс, орієнтований не передачу даних в байтному форматі

Два канали програмованих послідовних УСАПП.

Послідовний інтерфейс SPI з підтримкою режимів ведучий/підлеглий.

Програмований сторожовий таймер з вбудованим генератором.

Вбудований аналоговий компаратор.

Спеціальні можливості мікро контролера.

Скидання при подачі живлення і програмована схема скидання при зниженні напруги живлення.

Вбудований RC-генератор, що калібрується.

Зовнішні і внутрішні джерела переривань.

Шість режимів зниження енергоспоживання: холостий хід (Idle), зменшення шумів АЦП, економічний (Power-save), виключення (Power-down), черговий (Standby) і розширений черговий (Extended Standby)

Програмний вибір тактової частоти

Конфігураційний біт для перекладу в режим сумісності з ATmega103

Загальне виключення підтягаючих резисторів на всіх лініях портів введення-виводу

Уведення-виведення і корпуси

53 програмуємі лінії введення-виводу

64-выв. корпус TQFP

Робоча напруга

2.7 - 5.5В для ATmega128L

4.5 - 5.5В для ATmega128

Градації по швидкодії

0 - 8 Мгц для ATmega128L

0 - 16 Мгц для ATmega128

Короткий огляд:

ATmega128 - малопотужний 8-разр. КМОП мікроконтролер, заснований на розширеній RISC-архітектурі AVR. За рахунок виконання більшості інструкцій за один машинний цикл ATmega128 досягає продуктивності 1 млн. операцій в секунду/МГц, що дозволяє проектувальникам систем оптимізувати співвідношення енергоспоживання і швидкодії.

Ядро AVR поєднує багатий набір інструкцій з 32 універсальними робочими регістрами. Все 32 регістри безпосередньо підключено до арифметико-логічного пристрою (АЛУ), який дозволяє вказати два різні регістри в одній інструкції і виконати її за один цикл. Дана архітектура володіє більшою ефективністю коду за рахунок досягнення продуктивності в 10 разів вище в порівнянні із звичайними CISC-мікроконтролерами.

ATmega128 містить наступні елементи: 128 кбайт внутрісистемно програмованої флэш-пам'яті з підтримкою читання під час запису, 4 кбайт ЕСППЗУ, 4 кбайт статичного ОЗУ, 53 лінії універсального введення-виводу, 32 універсальні робочі регістра, лічильник реального часу (RTC), чотири гнучкі таймери-лічильники з режимами порівняння і ШИМ, 2 УСАПП, двухпроводний послідовний інтерфейс орієнтований на передачу байт, 8-канальний 10-разр. АЦП з опціональним диференціальним входом з програмованим коефіцієнтом посилення, програмований сторожовий таймер з внутрішнім генератором, послідовний порт SPI, випробувальний інтерфейс JTAG сумісний із стандартом IEEE 1149.1, який також використовується для доступу до вбудованої системи відладці і для програмування, а також шість програмно вибираних режимів зменшення потужності. Режим холостого ходу (Idle) зупиняє ЦПУ, але при цьому підтримуючи роботу статичного ОЗУ, таймерів-лічильників, SPI-порту і системи переривань. Режим виключення (Powerdown) дозволяє зберегти вміст регістрів, при зупиненому генераторі і виключенні вбудованих функцій до наступного переривання або апаратного скидання. У економічному режимі (Power-save) асинхронний таймер продовжує роботу, дозволяючи користувачеві зберегти функцію відліку часу в той час, коли решта частини контроллера знаходиться в стані сну. Режим зниження шумів АЦП (ADC Noise Reduction) зупиняє ЦПУ і всі модулі введення-виводу, окрім асинхронного таймера і АЦП для мінімізації імпульсних шумів в процесі перетворення АЦП. У черговому режимі (Standby) кварцевый/резонаторный генератор продовжують роботу, а решта частини мікроконтролера знаходиться в режимі сну. Даний режим характеризується малою споживаною потужністю, але при цьому дозволяє досягти найшвидшого повернення в робочий режим. У розширеному черговому режимі (Extended Standby) основний генератор і асинхронний таймер продовжують працювати.

Мікроконтролер проводиться за технологією високощільної незалежної пам'яті компанії Atmel. Вбудована внутрісистемно програмована флэш-пам'ять дозволяє перепрограмувати пам'ять програм безпосередньо усередині системи через послідовний інтерфейс SPI за допомогою простого програматора або за допомогою автономної програми в завантажувальному секторі. Завантажувальна програма може використовувати будь-який інтерфейс для завантаження прикладної програми у флэш-пам'ять. Програма в завантажувальному секторі продовжує роботу в процесі оновлення прикладної секції флэш-пам'яті, тим самим підтримуючи двухоперационность: читання під час запису. За рахунок поєднання 8-разр. RISC ЦПУ з внутрісистемно самопрограммируемой флэш-пам'яттю в одній мікросхемі ATmega128 є могутнім мікроконтролером, що дозволяє досягти високого ступеня гнучкості і ефективної вартості при проектуванні більшості додатків вбудованого управління. ATmega128 підтримується повним набором програмних і апаратних засобів для проектування, в т. ч.: Сі-компілятори, макроасемблери, програмні отладчики/симуляторы, внутрішньосистемні емулятори і оцінні набори.

Умовне графічне позначення мікроконтроллера ATmega128 наведено на рис.2.

Рис.2 Умовне графічне позначення мікроконтроллера ATmega128

Найменування виводів ATmega128:

| VCC | вивід джерела споживання |

| RESET | вхід системного скидання |

| XTAL1, XTAL2 | виводи для підключення кварцевого резонатору |

| РА0 ÷ РА7 | 8-розрядний двунаправлений порт А вводу/виводу з третім станом, при роботі з зовнішньою пам’яттю являється суміщеною шиною адреси даних (адрес необхідно по сигналу ALE занести в регістр) |

| PB0 ÷ PB7 | 8 - розрядний двунаправлений порт В вводу/виводу з третім станом, який має альтернативні функції |

| OC0/ТО (РВО) | вход зовнішнього сигналу таймера/лічильника ТО або виход таймера/лічильника ТО в режимах Compare, PWM |

| OC2/Т1 (РВ1) | вхід зовнішнього сигналу таймера/лічильника Т1 |

| AIN0 (PB2) | позитивний вхід компаратору |

| AIN1 (PB3) | негативний вхід компаратору |

| SS (PB4) | вибір підлеглого пристрою (slave) на шині SPI (послідовний інтерфейс) |

| MOS1 (PB5) | виход головного (master) чи вхід підлеглого (slave) пристрою даних модуля SPI |

| MІS0 (PB6) | вхід головного (master) чи вихід підлеглого (slave) пристрою даних модуля SPI |

| SCK (РВ7) | виход головного (master) чи вхід підлеглого (slave) пристрою тактового сигналу модуля SPI |

| PC0 ÷ PC7 | 8 - розрядний двунаправлений порт С вводу/виводу з третім станом, має альтернативну функцію - передає старший байт адреси (А8÷А15) при роботі з зовнішньою пам’яттю |

| PD0÷PD7 | 8 - розрядний двунаправлений порт D вводу/виводу з третім станом, має альтернативні функції |

| RxD0 (PD0) | вхід приймача універсального асинхронно послідовного порта (USART) |

| TxD0 (PD1) | виход передавальника універсального асинхронно послідовного порта (USART) |

| INT0 (PD2) | вхід зовнішнього переривання 0 |

| INT1 (PD3) | вхід зовнішнього переривання 1 |

| XCK0 (PD4) | вхід/вихід зовнішнього сигналу синхронізації (тактового сигналу USART) |

| OC1A (PD5) | виход А таймера/лічильника Т1 в режимі порівняння (Compare) і в режимі шин сигнала (PWM) |

| WR (PD6) | строб запису у зовнішнє ОЗП |

| RD (PD7) | строб читання із зовнішнього ОЗП |

| РЕ0÷РЕ2 | 3-розрядний двунаправлений порт Е вводу/виводу с третім сстаном, має альтернативні функції |

| РЕ0 (INT2) | вхід зовнішнього переривання 2 |

| ICP1 | вхід захвату таймера/лічильника Т1 (режим Compare) |

| РЕ1 (ALE) | строб адреси зовнішнього ОЗУ, записується адрес в регістр-заклямку |

| PE2 (OC1B) | вихід В таймера/лічильника Т1 в режимі Compare и PWM |

| GND | загальний вивід |

Електричні характеристики

Гранично-допустимі параметри

| Робоча температура | -55°C…+125°C |

| Температура зберігання | -65°C…+150°C |

| Напруга на будь-якому виводі по відношенню до загального пі-танія, окрім RESET | -1.0В … VCC+0.5В |

| Напруга на виводі скидання RESET по відношенню до об-щему | -1.0В … +13.0В |

| Максимальна робоча напруга | 6.0В |

| Постійний струм через лінію введення-виводу | 40.0 мА |

| Постійний струм через виводи VCC і GND | 200.0 мА |

Статичні характеристики

| Обозн. | Параметр | Умови вимірювання | Мин. | Ном. | Макс. | Ед. изм. |

| VIL | Вхідна напруга низького рівня | Окрім виводів XTAL1 і RESET | -0.5 | 0.2 VCC (1) | В | |

| VIL1 | Вхідна напруга низького рівня | виведення XTAL1, ви-брана зовнішня син-хронізация | -0.5 | 0.1 VCC (1) | В | |

| VIL2 | Вхідна напруга низького рівня | виведення скидання RESET | -0.5 | 0.2 VCC (1) | В | |

| VIH | Вхідна напруга високого рівня | Окрім виводів XTAL1, RESET | 0.6 VCC (2) | VCC + 0.5 | В | |

| VIH1 | Вхідна напруга високого рівня | Виведення XTAL1, ви-брана зовнішня син-хронізация | 0.7 VCC (2) | VCC + 0.5 | В | |

| VIH2 | Вхідна напруга високого рівня | Виведення скидання RESET | 0.85 VCC (2) | VCC + 0.5 | В | |

| VOL | Вихідна напруга низького рівня (3) ( порты A,B,C,D, E, F, G) | IOL = 20 мА, VCC = 5В IOL = 10 мА, VCC = 3В | 0.7 0.5 | В | ||

| VOH | Вихідна напруга високого рівня (4) (порты A,B,C,D) | IOH = - 20 мА, VCC = 5В IOH = - 10 мА, VCC = 3В | 4.0 2.2 | В | ||

| IIL | Вхідний струм витоку через лінію введення-виводу | Vcc = 5.5В, лог.0 (абс. значение) | 8.0 | мкА | ||

| IIH | Вхідний струм витоку через лінію введення-виводу | Vcc = 5.5В, лог.1 (абс. значение) | 8.0 | мкА | ||

| RRST | Опір подтягивающего резистора на вході скидання | 30 | 100 | кОм | ||

| RPEN | Опір подтягивающего резистора на вході PEN | 25 | 100 | кОм | ||

| RPU | Опір подтягивающего резистора на лініях введення-виводу | 20 | 100 | кОм | ||

| ICC | Споживаний струм | 4 МГц, VCC = 3В, активний режим (ATmega128L) | 5 | мА | ||

| 8 МГц, VCC = 5В, активний режим (ATmega128) | 20 | мА | ||||

| 4 МГц, VCC = 3В, режим холостого хода (ATmega128L) | 2 | мА | ||||

| 8 МГц, VCC = 5В, режим холостого хода (ATmega128) | 12 | мА | ||||

| Режим виключення (Power-down) (5) | Стор. таймер включен, VCC = 3В | < 25 | 40 | мкА | ||

| Стор. таймер отключен, VCC = 3В | < 10 | 25 | мкА | |||

| VACIO | Вхідна напруга зсуву аналогового компаратора | VCC = 5В Vвх = VCC /2 | 40 | мВ | ||

| IACLK | Вхідний струм витоку аналогового компаратора | VCC = 5В Vвх = VCC /2 | -50 | 50 | нА | |

| tACID | Затримка на ініциалізацію аналогового компаратора | VCC = 2.7В VCC = 5.0В | 750 500 | нс | ||

| tACID | Затримка распространенію сигналу в аналоговому компараторі | VCC = 2.7В VCC = 5.0В | 750500 | нс |

Завдяки тому, що шина даних і адреси в МК ATmega128 сполучені й мають поділ тільки в часі, то для їхнього поділу будемо використати регістр із третім станом К1810ИР82 для зберігання адреси.

Восьмирозрядні буферні регістри К1810ИР82 використовуються для організації запам'ятовуючих пристроїв, портів уводу-виводу, мультиплексорів і т.п. Буферні регістри складаються із восьми тригерів Т з виходними схемами 5Ш з трьома станами.

Формувач має дві групи - А і В виводів, а також два керуючих виводи - SТB та ОЕ. Дозвіл передачі залежить від рівня сигналу на виводі ОЕ, а напрямок передачі визначається рівнем сигналу на виводі Т.

Електричні параметри К1830ИР82.

Вхідний струм низького рівня не більше 0,2 мА

Вхідний струм високого рівня не більше 50 мкА

Вихідна напруга низького рівня не більше 0,45 В при струмі 32мА

Вихідна напруга високого рівня не меньше 2,4 В при струмі 1мА

Рис.3 - Умовне графічне позначення К1830ИР82

Для створення адресації зовнішніх пристроїв використовується дешифратор 3-8. На входи якого потрапляють молодші розряди адреси, а на виході установлюються сигнали вибору кристалу мікросхеми.

Рис.4 - Умовне графічне позначення К155ИД7

В цій мікро ЄОМ присутні пять зовнішніх пристроїв. Таким чином селектор адреси повинен бути більше ніж на пять розрядів, а також він повинен мати інверсні виходи для керування виборкою кристалів які також інверсні. Вище приведений (SN74138N) повністю задовольняє цим вимогам.

Розробка фізичних адрес зовнішніх пристроїв:

| А13 | А14 | А15 | CS | Назва пристрою | Фізична адреса | |

| 0 | 0 | 0 | 0 | RAM1 (2K) | 0000H-1FFFH | |

| 1 | 0 | 0 | 1 | ROM1 (2K) | 2000H-3FFFH | |

| 0 | 1 | 0 | 2 | ROM2 (2K) | 4000H-5FFFH | |

| 1 | 1 | 0 | 3 | ROM3 (1K) | 6000H-7FFFH | |

| 0 | 0 | 1 | 4 | ККіІ | 8000Н | |

| 1 | 0 | 1 | 5 | АЦП | A000Н | |

| 0 | 1 | 1 | 6 | Інтервальний таймер | C000Н | |

| 1 | 1 | 1 | 7 | Послідовний інтерфейс | E000H | |

Рис.5 - Схема підключення процесорного блоку

2.2 Розробка блоку пам’яті (ОЗП і ПЗП)

Ісходні дані:

Кількість комірок зовнішнього ОЗП NОЗУ - 2К×8

Вхідні струми:

при логічному 0, IIL - 1,6 мА

при логічній 1, IIH - 0,1 мА

Вхідна ємкість логічних схем навантаження, СI - 5 пФ

Монтажні ємкості усіх ланцюгів (См = 20 пФ).

Згідно завдання кількість комірок ОЗП складає NОЗУ.

Розрядність ОЗП nОЗУ повинна відповідати розрядності обробки даних ЦП.

Інформаційна ємкість СОЗУ визначається по формулі:

![]()

У якості мікросхеми ОЗП виберемо К537РУ10.

Необхідна швидкодія ОЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128 тривалість циклу запису (зчитування) tС равно 2ТМТ , де ТМТ - тривалість машинного такту.

При частоті кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

![]()

Тривалість циклу мікросхеми пам’яті tcy повинна задовольняти нерівності:

Мікросхему ОЗП виберемо К537РУ10, тому що вона ідеально підходить і не створює збитковості для даного випадку. Для цієї мікросхеми пам’яті ємкість 2К, а розрядність слова 8 біт:

![]() .

.

Розрахуємо число ВІС ОЗП в ряду матриці:

де nБИС - розрядність обраної мікросхеми пам’яті.

Визначимо число розрядів стовбців матриці:

де NБИС - кількість комірок обраної мікросхеми пам’яті.

Загальна кількість ВІС ОЗП дорівнює:

![]()

Таким чином, кількість корпусів ОЗП дорівнює 1.

Визначимо струмове IDL и IDH і ємкістне СD навантаження для схем вводу інформації в ОЗП по формулам:

IDL = mc * IIDL = 1 * 1,6 = 1,6 мА

IDH = mc * IIDH = 1 * 0,1 = 0,1 мА

CD = mc * CID + Cm = 1 * 5 + 20 = 25 пФ

де IIDL , IIDH - вхідні струми логічного 0 і логічної 1 по інформаційним ланцюгам обраної ВІС ОЗП.

CID - вхідна ємкість по інформаційному входу ВІС ОЗП.

Визначимо стум навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу ВІС ОЗП по формулам:

IAL = m * IIAL = 1 * 1,6 = 1,6 мА

IAH = m * IIAH = 1 * 0,1 = 0,1 мА

CA = m * CIA + Cm = 1 * 5 + 20 = 25 пФ

де IIАL , IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу обраної ВІС ОЗП.

CIА - вхідна ємкість по входу адресу ВІС ОЗП.

Визначимо струми навантаження ICSL , ICSH і величину ємкісного навантаження СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 1,6 = 1,6 мА

ICSH = mp * IICSH = 1 * 0,1 = 0,1 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

де IICSL , IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS) ВІС ОЗП.

CСS - вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ОЗП.

Значення ICSL , ICSH и CCS не повинні перевищувати максимально допустимі значення для обраних мікросхем, що забезпечують вибір ВІС ОЗП.

Рис.6 Умовно графічне позначення ОЗП К537РУ10

Найменування виводів:

A0 ÷ A10 - адресні входи.

W/R - запис/зчитування.

CS1 - chip select, чіп вибору.

CEO - виход дозволу.

D0 ÷ D7 - шина даних вводу/виводу.

ОЗП представляє собою статичний асинхронний оперативно запом’ятовуючий пристрій.

Режими роботи ОЗП:

| CS | OE | WR | A0. .10 | D0. .7 | Режим |

| M | X | X | Адрес | Дані | Зберігання |

| L | X | L | Запись | ||

| L | L | H | Зчитування | ||

| L | H | H | Заборона виходу |

Технологічні та електричні характеристики К537РУ10:

Технологія - КМОП

Організація - 2К×8

Час виборки, ns - не більш 220

Напруга живлення, V - 5

Струм живлення, мА

у режимі звернення - 30

у режимі зберігання - 1-2

Вхідна напруга, V

при логічному 0 - min 0 - max 0,4

при логічній 1 - min 0,9Ucc - max 0,5

Вихідна напруга, V

при логічному 0 - min 0 - max 0,4

при логічній 1 - min 2,4 - max 0,4

Вихід - 3 с.

Діапазон робочих температур, ºС - - 10 - +70

Розрахуємо ПЗП:

Оскільки по завданню необхідно створити ПЗП емкість 5К![]() 8, то було прийнято рішення використати дві схеми емкістю 2К

8, то було прийнято рішення використати дві схеми емкістю 2К![]() 8 та одну 1К

8 та одну 1К![]() 8.

8.

Початкові дані для мікросхеми КР556РТ20 1К![]() 8:

8:

Кількість комірок зовнішнього ПЗП NОЗУ - 1К×8

Вхідні струми:

при логічному 0, IIL - 0,25 мА

при логічній 1, IIH - 0,04 мА

Вхідна ємкість логічних схем навантаження, СI - 5 пФ

Монтажні ємкості усіх ланцюгов (См = 20 пФ).

Згідно завдання кількість комірок ПЗП складає NОЗУ.

Розрядність ПЗП nОЗУ повинна відповідати розрядності обробки даних ЦП.

Інформаційна ємкість СОЗУ визначається по формулі:

![]()

Необхідна швидкодія ПЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128 тривалість циклу запису (зчитування) tС равно 2ТМТ , де ТМТ - тривалість машинного такту.

При частоті кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

![]()

Тривалість циклу мікросхеми пам’яті tcy повинна задовольняти нерівності:

У якості мікросхеми ПЗП виберемо КР556РТ20, тому що вона ідеально підходить і не створює збитковості для даного випадку. Для даної мікросхеми пам’яті ємкість 1К, а розрядність слова 8 біт:

![]() .

.

Розрахуємо число ВІС ПЗП в ряду матриці:

![]()

де nБИС - розрядність обраної мікросхеми пам’яті.

Визначимо число розрядів стовбців матриці:

![]()

де NБИС - кількість комірок обраної мікросхеми пам’яті.

Загальна кількість ВІС ПЗП дорівнює:

![]()

Таким чином, кількість корпусів ПЗП дорівнює 1.

Визначимо стум навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу ВІС ПЗП по формулам:

IAL = m * IIAL = 1 * 0,25 = 0,25 мА

IAH = m * IIAH = 1 * 0,04 = 0,04 мА

CA = m * CIA + Cm = 1 * 5 + 20 = 25 пФ

де IIАL , IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу обраної ВІС ПЗП. CIА - вхідна ємкість по входу адресу ВІС ПЗП.

Визначимо струми навантаження ICSL , ICSH і величину ємкісного навантаження СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 0,25 = 0,25 мА

ICSH = mp * IICSH = 1 * 0,04 = 0,04 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

де IICSL , IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS) ВІС ПЗП.

CСS - вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ПЗП.

Враховуючи, що на відміну від ОЗП інформація з ПЗП тільки зчитується, то необхідно визначити струми навантаження і ємкість навантаження на інформаційні виходи ВІС ПЗП по формулам:

IQL = mР * IIL = 1 * 0,25 = 0,25 мА

IQH = mР * IIH = 1 * 0,04 = 0,04 мА

CQ = mC * CQO + mР *CI + Cm = 1 * 5 + 1 * 5 + 20 = 30 пФ

де IQL , IQH - вхідні струми логічного 0 і логічної 1 мікросхем навантаження ВІС ПЗП, CQO - вихідна ємкість одного інформаційного виходу ВІС ПЗП, CI - вхідна ємкість мікросхем навантаження ВІС ПЗП.

Отримані значення струмів не повинні перевищувати граничні значення для обраних мікросхем пам’яті.

Рис.7 Умовно графічне позначення ПЗП КР556РТ20

Найменування виводів:

A0 ÷ A9 - адресні входи.

D0 ÷ D7 - шина даних вводу/виводу.

CECS, CECS1 - вибір мікросхеми

Технологічні та електричні характеристики КР556РТ20:

Технологія - ТТЛШ

Організація - 1К×8

Час виборки, ns - не більш 65

Напруга живлення, V - 5

Струм живлення, мА - 180 мА

Вхідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихід - 3 с.

Потужність споживання, mW - 875

Діапазон робочих температур, ºС - - 10 - +70

Початкові дані для мікросхеми КР556РТ18 2К![]() 8:

8:

Кількість комірок зовнішнього ПЗП NОЗУ - 4К×8

Вхідні струми:

при логічному 0, IIL - 0,25 мА

при логічній 1, IIH - 0,04 мА

Вхідна ємкість логічних схем навантаження, СI - 5 пФ

Монтажні ємкості усіх ланцюгів (См = 20 пФ).

Згідно завдання кількість комірок ПЗП складає NОЗУ.

Розрядність ПЗП nОЗУ повинна відповідати розрядності обробки даних ЦП. Інформаційна ємкість СОЗУ визначається по формулі:

![]()

Необхідна швидкодія ПЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128 тривалість циклу запису (зчитування) tС равно 2ТМТ , де ТМТ - тривалість машинного такту. При частоті кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

![]()

Тривалість циклу мікросхеми пам’яті tcy повинна задовольняти нерівності:

У якості мікросхеми ПЗП виберемо КР556РТ20, тому що вона ідеально підходить і не створює збитковості для даного випадку. Для даної мікросхеми пам’яті ємкість 1К, а розрядність слова 8 біт:

![]() .

.

Розрахуємо число ВІС ПЗП в ряду матриці:

де nБИС - розрядність обраної мікросхеми пам’яті. Визначимо число розрядів стовбців матриці:

де NБИС - кількість комірок обраної мікросхеми пам’яті.

Загальна кількість ВІС ПЗП дорівнює:

![]()

Таким чином, кількість корпусів ПЗП дорівнює 2.

Визначимо стум навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу ВІС ПЗП по формулам:

IAL = m * IIAL = 2 * 0,25 = 0,50 мА, IAH = m * IIAH = 2 * 0,04 = 0,08 мА

CA = m * CIA + Cm = 2 * 5 + 20 = 30 пФ

де IIАL , IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу обраної ВІС ПЗП.

CIА - вхідна ємкість по входу адресу ВІС ПЗП.

Визначимо струми навантаження ICSL , ICSH і величину ємкісного навантаження СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL = mp * IICSL = 1 * 0,25 = 0,25 мА

ICSH = mp * IICSH = 1 * 0,04 = 0,04 мА

CCS = mp * CICS + Cm = 1 * 5 + 20 = 25 пФ

де IICSL , IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS) ВІС ПЗП.

CСS - вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ПЗП.

Враховуючи, що на відміну від ОЗП інформація з ПЗП тільки зчитується, то необхідно визначити струми навантаження і ємкість навантаження на інформаційні виходи ВІС ПЗП по формулам:

IQL = mР * IIL = 1 * 0,25 = 0,25 мА

IQH = mР * IIH = 1 * 0,04 = 0,04 мА

CQ = mC * CQO + mР *CI + Cm = 2 * 5 + 1 * 5 + 20 = 35 пФ

де IQL , IQH - вхідні струми логічного 0 і логічної 1 мікросхем навантаження ВІС ПЗП, CQO - вихідна ємкість одного інформаційного виходу ВІС ПЗП, CI - вхідна ємкість мікросхем навантаження ВІС ПЗП.

Отримані значення струмів не повинні перевищувати граничні значення для обраних мікросхем пам’яті.

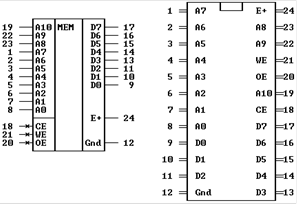

Рис.8 Умовно графічне позначення ПЗП КР556РТ18

Найменування виводів:

A0 ÷ A10 - адресні входи.

D0 ÷ D7 - шина даних вводу/виводу.

CS1 ÷ СS3 - вибір мікросхеми

Технологічні та електричні характеристики КР556РТ20:

Технологія - ТТЛШ

Організація - 2К×8

Час виборки, ns - не більш 60

Напруга живлення, V - 5

Струм живлення, мА - 180 мА

Вхідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихідна напруга, V

при логічному 0 - min 2,4 - max 0,5

при логічній 1 - min 2,4 - max 0,5

Вихід - 3 с.

Потужність споживання, mW - 875

Діапазон робочих температур, ºС - - 10 - +70

Рис.9 - Схема підключення процесорного блоку і пам’яті

2. 3 Інтервальний таймер

Одним з елементів, обумовлених завданням, є інтервальний таймер i8254. Таймер призначений для формування затримок послідовності імпульсів, формування одиночних імпульсів заданої тривалості, формування стробуємих імпульсів із програмованою затримкою. Виконаний по n-МОП технології.

Рис.10 - Умовне графічне позначення таймеру i8254

D0 - D7 - двонаправлена шина даних з високоімпедансним станом.

А0 - А1 - розряди шини даних, визначають регістр, що буде адресуватися: А1А0 = 00 - адреса каналу 0; А1А0 = 01 - адреса каналу 1; А1А0 = 10 - адреси каналу 2; А1А0 = 11 - адреса регістра керуючого слова

![]() - вибір кристала

- вибір кристала

![]() - сигнал запису

- сигнал запису

![]() - сигналу читання

- сигналу читання

CLK0 - CLK2 - вхід дозволу подачі імпульсу від зовнішнього джерела

GATE0 - GATE2 - вхід дозволу подачі імпульсу сlk на таймер/лічильник

OUT0 - OUT2 - вихід таймерів/лічильників

Вхідні сигнали CLK0 - CLK2 подаються через схеми із зовнішніми керуючими входами GATE0 - GATE2. Кожен лічильник має вихідний сигнал OUT. Інші вузли схеми призначені для установки режиму й реалізації інтерфейсу із системною шиною.

Для функціонування таймера мікроконтролер повинен завантажити керуючі слова, значення яких позначають режим кожного лічильника, і необхідні початкові значення. У завданні нам дані параметри для програмування таймера, тому ми проініціализуємо його в розділі розробки програм ініціалізації.

Електричні параметри i8254:

1. Напруга живлення - 5 В

2. Вихідна напруга:

високого рівня - 2,4 В

низькі рівні - 0,5 В

3. Вихідний струм високого рівня - 1 мА

4. Вихідний струм низького рівня - 5 мА

5. Вхідний струм високого рівня - 30 мкА

6. Вхідний струм низького рівня - 30 мкА

Рис.11 - Схема підключення таймера i8254

2.4 Аналого-цифровий перетворювач (АЦП)

Згідно із завданням, у нашій МПС повинен бути використаний аналого-цифровий перетворювач. Це пристрій, який перетворює аналоговий сигнал у цифровий код. Цей код повинен потрапляти на всі пристрої, таким чином, АЦП підключається до загальної шини.

Варіантом передбачено використання 12ти розрядного швидко-діючого АЦП послідовного наближення, працюючого із ТТЛ-рівнями. Так як дана мікросхема не має окремого блоку цифрового керування, то включення АЦП до шини даних проводиться завдяки регістру К1810ИР82. Нижче наведено УГП MAX201В (іноземний аналог).

Рис.12 - Умовно графічне позначення MAX201B

Основні електричні параметри мікросхеми приведені нижче:

Напруга живлення: +5±10%В, - 15±15%

Максимальний вхідний струм лог.1: 100мкА

Максимальний вхідний струм лог.0: 100мкА

Мінімальна вхідна напруга лог.1: 2В

Максимальна вхідна напруга лог.0: 0,8В

Максимальний вихідний струм лог.1: 0,5мА

Максимальний вихідний струм лог.0: 3,2мА

Мінімальна вихідна напруга лог.1: 2,4В

Максимальна вихідна напруга лог.0: 0,4В

Вхідна ємність по всіх виводах (на частоті 1МГц): 6пФ

Вихідна ємність (на частоті 1МГц): 5пФ

Похибка перетворення: ±1/2ОМР

Час перетворення: 20мкС

Струм живлення: 15мА

Споживана потужність: 800мВт

2.5 Контролер клавіатури і індикації

Для керування індикацією та сканування клавіатури використовується спеціалізована мікросхема i8279. Вона являє собою контролер клавіатури та індикації. Мікросхема має внутрішній ОЗП клавіатури та індикації, може працювати у декількох режимах і дозволяє керувати восьми - або шістнадцятирозрядною індикацією та опитувати до 128 клавіш або дискретних датчиків. Умовне графічне позначення мікросхеми приведене на рис.14.

Рис.13- Умовне-графічне позначення мікросхеми i8279

Внутрішня адресація виробляється по входу A0, тому на цей вхід потрібно подати сигнал з адресної шини. Обмін даними йде по шині даних. Входи RL0-RL7 мікросхеми служать для зчитування стану клавіш клавіатури; виходи OutA3-OutA0, OutB0-OutB3 підключаються до індикаторів; виходи S0-S3 - це виходи сканування рядків клавіатури й перебору індикаторів при відображенні. При надходженні інформації від клавіатури контролер виробляє запит на переривання, виставляючи на виході IRQ сигнал активного рівня. Цей сигнал надходить на один із входів зовнішніх переривань мікроконтролера.

Найменування виводів мікросхеми i8279:

D0…D7 - входи-виходи з третім станом

CS - вибір мікросхеми

RD - читання

WR - запис

A0 або C/D - команда / данні

CLK - синхронізація

RES - початкова установа

S0…S3 - сканування

BD - гасіння індикації

OUTA3… OUTA0, OUTB3… OUTB0 - коди символів

R0…R7 - прийом сигналів з клавіатури

SHIFT - верхній / нижній регістр

IRQ - запит переривання

Технологічні та електричні характеристики:

Технологія - ТТЛШ

Напруга живлення, В - 5

Вихідна напруга, В:

високого рівня - 2,4

низького рівня - 0.45

Вихідний струм, мA:

при напрузі низького рівня - 5

при напрузі високого рівня - 1

Вхідний струм, мкA:

низького рівня - 30

високого рівня - 30

Потужність - 350 мВт

Струм споживання - 60 мА

Режими роботи інтерфейсу клавіатури:

1. Послідовне опитування матриці клавіш із декодуванням і забороною уведення двох одночасно натиснутих клавіш.

2. Послідовне опитування з дешифруванням лічильника сканування з дозволом натискання N клавіш (N<=8).

3. Послідовний режим без дешифрації клавіш із забороною уведення 2х і більше натиснутих клавіш (S0-S3 - Висновки лічильника, до нього підключений 8 розрядний дешифратор (128 кл))

4. Послідовне опитування без дешифрування й з дозволом N натиснутих клавіш N<=8.

5. Послідовне опитування матриці датчиків з дешифруванням матриці сканування.

6. Послідовне опитування матриці датчиків без дешифрування матриці сканування.

7. Стробований вхід з дешифруванням лічильника сканування, що використається для опитування.

8. Стробований вхід без дешифрування лічильника сканування, що використається для опитування.

Режими роботи блоку індикації:

0. Виводить символ на 8мі розрядну індикацію, з розміщенням їх ліворуч праворуч.

1. Виводить символ на 16ти розрядну індикацію, з розміщенням їх ліворуч праворуч.

2. Виводить символ на 8мі розрядну індикацію, зі зрушенням раніше відображеної інформації вліво.

3. Виводить символ на 16ти розрядну індикацію, зі зрушенням раніше відображеної інформації вліво.

Згідно завданню треба організувати 8 індикаторів та 11 клавіш.

Для перетворення двійкового коду у семисегментний використаємо дешифратор К155ИД7, який має три входи і вісім виходів, чого достатньо для виконання поставленої задачі. Даний дешифратор у своєму составі має керуючі входи для організації динамічної індикації.

Рис.14 - Умовне графічне позначення К155ИД7

Найменування виводів:

А0-А2 - адресні входи,

Q0-Q7 - лінії виходу,

С1-С3 - ліній вибору мікросхеми.

Технологічні та електричні характеристики:

Технологія - ТТЛШ

Напруга живлення, V - 5

Вихідна напруга, V

високого рівня - 2,2

низького рівня - 0.8

Вихідний струм, mA

при напрузі високого рівня - 20

при напрузі низького рівня - 8

Струм споживання, mA – 74

Рис.15 - Схема підключення блоку i8279

Сформуємо формат команди встановлення режиму роботи контролера:

ICW1 = 00000001B = 01H

Обрано Режим 0 роботи інтерфейсу індикації та Режим 1 роботи інтерфейсу клавіатури, вивід символів на 8мі розрядну індикацію з розміщенням їх ліворуч праворуч та з запереченням натискання двох або більше клавіш.

Сформуємо формат команди програмування синхронізації: ICW2 = 00110100B = 34H. Коефіцієнт переліку вибрано рівним 20, тобто 10100В, тому що внутрішня частота інтерфейсу не повинна перевищувати 100кГц (2МГц /20 = 100кГц).

Сформуємо формат команди запису у ОЗП індикації:

ICW3 = 10010000B = 90H

Сформуємо формат команди читання ОЗП клавіатури:

ICW4 = 01010000B = 50H

Програма ініціалізації контролера клавіатури і індикації i8279

| Мітка | Мнємокод | Операнди | Коментарії |

i8279: m1: |

. equ . equ . equ . equ . equ . equ ldi sts ldi sts ldi sts ldi ldi mov sts dec cpi brne ldi lds mov ret |

ICW1 = 0x01 ICW2 = 0x34 ICW3 = 0x90 ICW4 = 0x50 Adr2 = 0x8000 Adr1 = 0x8001 R0, ICW1 Adr1, R0 R0, ICW2 Adr1, R0 R0, ICW3 Adr1, R0 R1, 0x08 R2, 0x100 R3, R2 Adr2, R3 R2 R2, 0 m1 R4, 0x300 R5, Adr2 R4, R5 |

; команда установки режиму ; команда программ. синхронізації ; команда запису в ОЗП індикації ; команда читання ОЗП клавіатури ; адреса завантаження команд ; адреса завантаження даних ; завантаження команди режиму роботи ; у контролер ; завантаження команди програмування ; синхронізації у котролер ; завантаження команди запису в ОЗП ; індикації у контролер ; завантаження лічильника ; завантаження початкової адреси ; завантаження даних в ОЗП індикації ; декремент регістру ; порівняння значення в регістрі з 0 ; перехід на мітку, якщо не рівно 0 ; завантаження початкової адреси ; читання ОЗП клавіатури ; зміст регістру R5 відправити у пам’ять по адресу, який знаходиться в R4 |

2.6 Адаптер послідовного інтерфейсу Intel 8251

Адаптер послідовного інтерфейсу слугує для обміну інформацією у послідовному коді у двох режимах: асинхронному та синхронному.

Умовно графічне зображення адаптеру наведено на Рис.16

Рис.16 - Адаптер послідовного інтерфейсу i8254

Електричні параметри i8251:

1. Напруга живлення - 5 В

2. Вихідна напруга:

високого рівня - 2,4 В

низькі рівні - 0,45 В

3. Вихідний струм високого рівня - 1 мА

4. Вихідний струм низького рівня - 5 мА

5. Вхідний струм високого рівня - 30 мкА

6. Вхідний струм низького рівня - 30 мкА

Програмування адаптеру послідовного інтерфейсу Intel 8251

Завдання: Запрограмувати адаптер i8251 для роботи у асинхронному режимі на випадок:

кількість стоп-біт: 2

кількість інформаційних біт: 8

контроль парності

коеф. ділення частоти синхронізації: 16

кількість посилок: 48

Програма:

Спочатку сформуємо слово приказу - 11011110 #DEH

Початковий адрес у пам’яті #100Н

Кінцевий адрес у пам’яті #130Н

Адреса адаптеру #E000H

i8251: ; оголошення констант

. equadr1 = 0xE001; адреса А0=1

. equadr2 = 0xE000; адреса адаптеру

. equmask1 = 0x01; відокремлення TxRDY

. equmask2 = 0x02; відокремлення RxRDY

. equmask3 = 0b00111000; виявлення помилок

ldiR0, 0xDE; слово приказу

stsadr1, R0; програмув. на асинхр. режим

m1: ldiR0, 0x01; завантаження РПД=1

stsadr1, R0; слово команда, дозвіл

; передачі

m2: ldsR0, adr1; читання слова-стану

andiR0, mask1; маскування біта TxRDY

breqm2

ldiR31, 0x01; поч. адреса для видачі 100H потрапляє у

; старший байт Z (ZH=R31)

ldiR2, 0x30; 48 посилок

m3: ; програмув. передачі

ld R3, Z+; передача із слідуючої комірки у РОН

stsadr2, R3; видача байту інформації

decR2; декримент лічильника

cpiR2, 0

brnem3

RET

m4: ldiR0, 0x04; завантаження РПД=1

stsadr1, R0; слово команда, дозвіл

; прийому

m5: ldsR0, adr1; читання слова-стану

andiR0, mask2; маскування біта RxRDY

breqm5

ldsR0, adr1; читання слова-стану

andiR0, mask3; перевірка на факт помилки

brneerror

ldiR30, 0x31; поч. адреса для прийому 131H

; потрапляє побайтово до молодшого та

; старшого байтів рег. Z (ZL=R30)

ldiR31, 0x01; (ZH=R31)

ldiR2, 0x30; 48 посилок

m6: ; програмув. прийому

ldsR3, adr2; прийом байту інформації

stZ+, R3; прийом у слідуючу комірку РОН

decR2; декримент лічильника

cpiR2, 0

brnem6

RET

2.7 Розрахунок електричних навантажень на лінії мікросхем

Проведемо розрахунок навантажувальних характеристик для виходів мікроконтролера для шини даних, адреси і керування.

Навантаження на шину даних мікроконтролера визначається по формулі:

IвихDL =IвхСKI + IвхPIТ + IвхOZU + IвхPZU + IвхACP = 0,03 + 0,03 + 1,6 + 0,25 + 0,1 = = 2,01 мА;

IвихDH = IвхCKI + IвхPIТ + IвхOZU + IвхPZU +IвхACP = 0,03 + 0,03 + 0,1 + 0,04 + 0,1 = = 0,3 мА;

СD = СCKI + СPIТ + СOZU + СPZU + СACP = 5 + 5 + 25 + 35 + 6 = 76 пФ.

Так як навантаження на шину даних не перевищує 40 мА, то використання додаткового шиного формувача не потрібне. Використаний буферний регістр відповідає поставленим вимогам.

Навантаження на шину адреси мікроконтролера визначається по формулі:

IвихАL =IвхСKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 1,6 + 0,50 = 2,16 мА;

IвихАH = IвхCKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 0,1 + 0,08 = 0,24 мА;

СА = СCKI + СPIТ + СOZU + СPZU = 5 + 5 + 25 + 30 = 65 пФ.

Так як навантаження на шину адреси не перевищує 40 мА, то використання додаткового шиного формувача не потрібне. Використаний буферний регістр відповідає поставленим вимогам.

Навантаження на шину керування мікроконтролера визначається по формулі:

IвихСL =IвхСKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 1,6 + 0,25 = 1,94 мА;

IвихСH = IвхCKI + IвхPIТ + IвхOZU + IвхPZU = 0,03 + 0,03 + 0,1 + 0,04 = 0,23 мА;

СС = СCKI + СPIТ + СOZU + СPZU = 5 + 5 + 25 + 25 = 60 пФ.

Отримані при розрахунку значення струмув та ємностей не перевищують граничні значення.

Висновки

В ході виконання курсової роботи була розроблена повна принципова схема мікропроцесорної системи. Були розглянуті різні варіанти структурної та принципової схем. Згідно із завданням складена програма ініціалізації окремих блоків. Обрані та розраховані необхідні у системі елементи. Була розглянута видача і запис інформації в пам’ять, АЦП, керування системою за допомогою клавіатури та індикації.

Виконання курсової дозволить у подальшому без труднощів розробляти подібні та ще більш складні процесорні системи.