| Скачать .docx |

Курсовая работа: Курсовая работа: Преобразователь кодов Манчестер-2

Министерство образования и науки Российской Федерации

Омский государственный технический университет

Кафедра «Автоматизированные системы обработки информации и управления»

Курсовой проект

на тему «Преобразователь кодов»

по дисциплине «Электротехника и электроника»

Пояснительная записка

Шифр проекта КП – 2068998-43-ИВТ245-05 ПЗ

Направление 230100

Зав. кафедрой, д.т.н., проф. А.В. Никонов

Студент П.Е. Бураменский

Омск 2007

Реферат

Пояснительная записка 24 с., 21 рис., 4 табл., 18 источников, 2 л. графического материала.

Манчестер-2, самосинхронизирующийся код, преобразование кодов, последовательный двоичный код, физическое кодирование

Объектом выполненной работы является преобразователь кодов.

Цель работы – изучение принципов преобразования разных типов физического кодирования, ознакомление с современными сериями ИС; проектирование преобразователя кодов.

В процессе работы проводились расчеты на структурном уровне, выбор элементов, разработка функциональной и принципиальной электрической схемы.

В результате был спроектирован преобразователь кодов, корректно кодирующий двоичный последовательный сигнал в Манчестер-2 (в уровнях КДМП ИС) в диапазоне частот 80 МГц. Устройство способно работать на нагрузку 50 Ом.

Основные технико-эксплуатационные показатели: высокая надежность и простота схемы.

Степень внедрения – учебное проектирование.

Введение

1 Выбор и обоснование направления проектирования

2 Расчёт на структурном уровне

3 Выбор элементов электрической схемы

3.1 Логические элементы «НЕ»

3.2 Логические элементы «2И»

3.3 Логические элементы «2ИЛИ»

3.4 Асинхронный RS-триггер

3 Электрическое моделирование

4 Анализ метрологических характеристик

Список использованных источников

Одним из ведущих направлений развития человеческого общества является информатизация – всё большее внедрение компьютерных технологий в различные сферы человеческой деятельности, с целью повысить эффективность его труда. Одним из направлений этого движения является создание различных сетей передачи данных, и других систем нуждающихся в обмене данными. Эти данные передаются посредством различных способов физического и логического кодирования. Одним из наиболее распространенных типов физического кодирования информации для передачи на средние и большие дистанции является код Манчестер-2.

В Манчестерском коде для кодирования единиц и нулей используется перепад сигнала, то есть фронт импульса. Каждый такт делится на две части. Так как сигнал изменяется по большей мере один раз за такт передачи одного бита данных, то манчестерский код обладает хорошими самосинхронизирующими свойствами. У него нет постоянной составляющей, а основная гармоника в худшем случае (при передаче последовательностей нулей и единиц) имеет частоту N Гц, а в лучшем (при передаче чередующихся единиц и нулей) – N/2 Гц. Поскольку отсутствие высокого или низкого уровня в течение всего интервала бита недопустимо, появление таких ситуаций может свидетельствовать об ошибке.

Эти свойства и наличие самосинхронизации, исключающей возникновение фазовых сдвигов между информационными и синхронизирующими последовательностями, определили использование кода «Манчестер-2» как основного для каналов последовательной передачи в протоколе Ethernet, бортовых САУ и целом ряде коммерческих систем.

Проектируемый кодер преобразует последовательный двоичный код (NRZ - используется для передачи данных между блоками различных вычислительных систем, в виду своей простоты) в Манчестер-2, что позволяет производить надежный обмен данными между удалёнными устройствами.

1. Выбор и обоснование направления проектирования

В результате обзора широкого спектра литературы и интернет источников, были найдены аналоги устройства, которые выполняют схожие задачи. Практически все устройства схожи с техническим заданием, но не до конца удовлетворяют его требованиям. Проблемой также стало отсутствие, в большинстве случаев, детальной информации по найденным аналогам, позволяющей использовать их проектировании необходимого устройства.

Транзитивный метод физического кодирования сигнала Манчестер-2 (Manchestercode, также за рубежом Phase Encoding или PE) на данный момент один из самых распространенных в различных САУ и ЛВС. Так, например, Манчестер-2 применятся в стандартах сетевых протоколов Ethernet, TokenRing, MIL-STD-1553B(ГОСТ. 52070-2003), MIL-STD-1760 и многих других, применяемых в различных областях от построения коммерческих локальных сетей, до бортовых САУ в авиации и судостроении. Такое широкое применение Манчестерского кодирования обуславливает довольно большое количество электронных кодирующих устройств, в частности, на западе выпускают ряд КМДП монолитных кодеров/декодеров Манчестера(CMOS Manchester Encoder/Decoder) : серий 3D7501, ACT-15530, а также HI-15530, HD-15530, HD-15531, СТ-10894 и другие. В России разнообразие не столь велико, удалось найти информацию лишь о КМДП ИС К588ВГ3 и К588ВГ6, созданных ещё в конце 80-х годов. Ниже, на рисунке 1.1, для ознакомления показаны условное графическое представление К588ВГ3.

Рисунок 1.1 – Условные графические представления К588ВГ3

Но ни одна из названных БИС не удовлетворяет условиям технического задания - все имеют недостаточный диапазон тактовых частот: для микросхем серии 3D7501, предназначенных для работы в сетевых картах, он доходит до 50 МГц, а для ACT15530, HI-15530, К588ВГ3 и К588ВГ6 предназначенных для работы в сетях протокола MIL-STD-1553, всего лишь до 1,25 МГц. Остальные существенные параметры К588ВГ3 приведены в таблице 1.

Кроме того, практически все упомянутые ИС кодируют биполярный Манчестер-2, проектируемое же устройство, согласно техническому заданию кодирует униполярную разновидность Манчестера-2.

Таблица 1 – Электрические параметры К588ВГ3, КР588ВГ3

| Номинальное напряжение питания | 5 В ± 5% |

| Выходное напряжение низкого уровня | 0,4 В |

| Выходное напряжение высокого уровня | (Uп – 0,4) В |

| Ток потребления | ≤ 0,1 мА |

| Время задержки распространения сигнала (от входа 10 до выхода 36) | ≤ 80 нс |

| Максимальная емкость нагрузки | 100 пФ |

| Частота работы канала | 1,25 МГц |

Однако причиной невысокой, по современным меркам, частоты работы канала является не принципиальный изъян используемых в этих БИС принципов кодирования, а не достаточная скорость работы элементной базы. Таким образом, используя более быстрые компоненты, можно достичь необходимой тактовой частоты без изменения схемы работы этих устройств. В этом ключе, их несомненно можно рассматривать как аналоги при разработке курсового проекта. По зарубежным ИС не удалось найти электронных принципиальных и элементных схем. Поэтому проанализируем отечественную БИС К588ВГ3, которая, в целом, идентична HI-15530 (не исключаю возможности, что К588ВГ3 была напрямую скопирована с зарубежных образцов, в виду небольшого отставания СССР в области компьютерных технологий в те годы и внедрения в производство стандарта сетевых протоколов ГОСТ 26765.52-87 (MIL-STD-1553)).

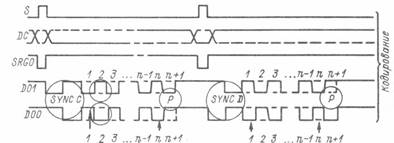

Рисунок 1.2 – Структура и принципиальная временная диаграмма работы кодера К588ВГ3

В состав кодера (CD) БИС КДК входят:

DIV 6 — делитель на 6, используемый для получения из частоты синхронизации декодера (12f) частоты синхронизации кодера (2f);

DIV 2 — делитель на 2, используемый для получения из частоты синхронизации кодера 2f частоты приема данных в кодер (1f);

CDM — кодер манчестерского кода;

СТ2 — счетчик числа передаваемых в слове битов.

Для нас наиболее важен кодер, находящийся в блоке CDM, остальные части ИС К588ВГ3 выполняют действия, в которых, согласно техническому заданию, нет необходимости.

В таблице 2 описаны выводы БИС кодера.

Временная диаграмма, поясняющая общие принципы использования БИС КДК, приведена на рисунке 1.3. При передаче строом SRGO производится запись слов, подлежащих кодированию, во внешний параллельно-последовательный регистр, данные из которого в последовательном коде поступают на вход DI по синхроимпульсам С1 . При приеме информации из МК стробом SRGI может выбираться внешний последовательно-параллельный регистр, используемый для накопления декодированных данных, поступающих с выхода DO по синхроимпульсам СО в последовательном коде. Формирование сигналов SRGI и SRGO производится внешней схемой на основе сигналов TD и GD (выходы синхронизации приема/передачи слова).

При передаче кодер в зависимости от уровня сигнала на входе DC автоматически вырабатывает нужный синхроимпульс SYNC С или SYNC D и вставляет бит четности (Р). Согласование работы кодера с оконечным устройством осуществляется сигналами запуска передачи S, запрета на выдачу очередного слова ST и строба выдачи слов CD .

Таблица 2 –Описание выводов БИС кодера К588ВГ3

Обознач. |

Номер контакта | Назначение вывода |

| DI0, DI1 | 12,13 | Униполярные фазоманипулированные инверсные входы «нуля» и «единицы» декодера (прямые) |

| DO0, DO1 | 26, 29 | Униполярные фазоманипулированные выходы «нуля» и «единицы» кодера (инверсные) |

| FO | 24 | Выход частоты синхронизации кодера (2 МГц) |

| С I | 36 | Выход тактовой частоты приема кодера (1 МГц) |

| MR | 22 | Вход общего сброса КДК |

| DC | 32 | Вход задания типа генерируемого синхроимпульса (SYNCD или SYNC С) |

| S | 34 | Вход запуска кодера |

| ST | 28 | Вход разрешения выдачи биполярного кода |

| PS | 33 | Вход задания полярности контрольного бита шифратора кодера |

| F | 39 | Вход делителя на шесть (12 МГц) |

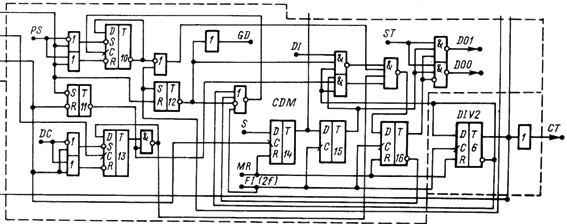

Рассмотрим организацию непосредственно кодера Манчестерского кода, обозначенного на схеме аббревиатурой CDM. На рисунке 4 представлена его функциональная схема вместе с другими блоками, работающими в кодере К588ВГ.

Перед тем как попасть непосредственно на шифратор информация проходит через счётчик битов СТ2, (показан на рисунке 3), который сравнивает код на входах С0 – С4 с числом тактов, в течение которого принимается слово, причёмподсчет битов ведется по модулю п +4 (n – число битов), так как слово включает синхроимпульс и бит четности. Также перед шифратором находятся счетчики/делители, организованные по обычной схеме и реализуемые на основе одного (Т6) и трех ( T 7— T 9) триггеров (соответственно DIV 2 и DIV 6 – показан только на рисунке 3).

Схема шифратора (построена на триггерах Т10—Т16) подстраивает фазу передаваемых сигналов к частоте 2f, принимаемой по входу FI , и синхрочастотой С I стробирует ввод данных с входа DI ; код «Манчестер-2» выдается на выходы DO 0, DO 1. Сигнал ST заведен на выходные элементы, стробирующие выдачу информации. Триггер Т10 включен по схеме счетчика и накапливает сумму передаваемого кода по четности или нечетности в зависимости от полярности сигнала PS .

Несложно заметить, что данная схема, как и другие найденные аналоги, избыточна и чрезмерно сложна, по сравнению с устройством, которое необходимо разработать по техническому заданию.

Рисунок 1.3 – Функциональная схема кодирующей части К588ВГ3

Это объясняется тем, что эти БИС являются не просто кодерами Манчестера-2, полноценными блоками бита/слова входящими в состав любого терминала САУ выполняя функции шифрации/дешифрации информации в формате слов определенных стандартом, формирует синхроимпульсы, генерирует бит четности, обнаруживает при приеме ошибки кода и четности слова. Поэтому эффективней самостоятельно создать кодирующую схему, чем вычленять необходимые компоненты из блока CDM БИС КДК К588ВГ3.

Для этого подробней рассмотрим суть Манчестерского кодирования. В Манчестерском коде для кодирования единиц и нулей используется перепад сигнала, то есть фронт импульса. Каждый такт делится на две части. Информация кодируется перепадами потенциала, происходящими в середине каждого такта. Единица кодируется перепадом от низкого уровня сигнала к высокому, а ноль – обратным перепадом (хотя существует стандарт Манчестера-2, где наоборот единица кодируется переходом от высокого к низкому уровню, а ноль - соответственно от низкого к высокому). В начале каждого такта может происходить служебный перепад сигнала, если нужно представить несколько единиц или нулей подряд. Графически это представлено на рисунке 1.4.

Рисунок 1.4 – Представление сигнала в коде Манчестер-2

Так как сигнал изменяется по большей мере один раз за такт передачи одного бита данных, то манчестерский код обладает хорошими самосинхронизирующими свойствами. У него нет постоянной составляющей, а основная гармоника в худшем случае (при передаче последовательностей нулей и единиц) имеет частоту N Гц, а в лучшем (при передаче чередующихся единиц и нулей) – N/2 Гц. Поскольку отсутствие высокого или низкого уровня в течение всего интервала бита недопустимо, появление таких ситуаций может свидетельствовать об ошибке. Ложное декодирование («1» →«0» или «0» → «1») в манчестерском коде может произойти только тогда, когда из-за помехи инверсия логических уровней будет иметь место в каждой половине интервала одного бита, однако вероятность одновременной инверсии фазы в пределах одного бита невелика.

Из всего вышесказанного можно прийти к следующим выводам:

1. Чтобы преобразовать последовательный двоичный код (он представляет собой потенциальный код, где единица кодируется высоким уровнем сигнала, а ноль низким уровнем сигнала, причём состояния меняются на границе тактов) в Манчестер-2 кодер должен выполнять 4 типа операций:

а) При низком уровне в такте входящего кода (кодирование логического нуля), создать в исходящем коде перепад с высокого уровня на низкий в середине такта;

б) При высоком уровне в такте входящего кода (кодирование логического единицы), создать в исходящем коде перепад с низкого уровня на высокий в середине такта;

в) При кодировании двух и более подряд идущих логических нулей, обеспечить подъём сигнала с нижнего на верхний уровень на границе тактов (чтобы на следующем такте можно было выполнить операцию а));

г) При кодировании двух и более подряд идущих логических единиц, обеспечить переход сигнала с верхнего на нижний уровень на границе тактов (чтобы на следующем такте можно было выполнить операцию б));

2. Кроме сигнала последовательного двоичного кода для кодирования Манчестера-2 необходимо два вида синхросигнала:

а) Синхросигнал, синхроимпульсы в котором приходятся на начало каждого такта. Обозначим его как SYNCB (от англ. сокращения SYNC – synchronizingsignal(синхронизирующий сигнал) и B – boundary (граница));

б) Синхросигнал, синхроимпульсы в котором приходятся на середину каждого такта. Обозначим его как SYNCM (от англ. M – middle (середина)).

Согласно техническому заданию синхросигналы внешние, что существенно упрощает разработку устройства, в виду избавления от необходимости проектировать генератор синхросигнала и решать проблему с подстройкой синхрочастоты.

Итак, определив конкретный круг задач, приступим непосредственно к созданию функциональной схемы проектируемого устройства. Начнём проектировать «с конца», т.е. с конечных элементов устройства. Очевидно, что внутри устройства логические элементы будут работать на кратковременных импульсах, однако сигнал выходящий из устройства в коде Манчестер-2, должен обладать высоким уровнем в течении необходимого по протоколу кода времени (такт или полтакта). Следовательно, надо использовать цифровое устройство способное при получении кратковременного импульса на вход подавать длительный сигнал на выход. В качестве такого устройства используем асинхронный RS-триггер.

Асинхронного RS-триггер обладает двумя информационными входами: S – По которому производится установка триггера в состояние логической «1» и R - по которому производится установка триггера в состояние логического «0». Следовательно, на вход S мы будем подавать сигналы, соответствующие подъему сигнала в Манчестерском коде с низкого уровня на высокий. А так как такой подъём происходит в Манчестерском коде либо при кодировании логической единицы (тогда он происходит в середине такта), либо при кодировании двух и более нолей расположенных непосредственно друг за другом (тогда в начале такта), то на вход S будет работать блок элементов, формирующий именно эти сигналы. И соответственно для информационного входа R мы создадим структуры формирующие сигналы, соответствующие переходу Манчестерского кода с высокого уровня на низкий (случай кодирования логического ноля – в середине такта или последовательности единиц – в начале такта).

![]() Для того чтобы сформировать импульс для входа S, который будет приходиться на границу тактов и обозначать служебный переход с низкого уровня на высокий, используем двухвходовый логический элемент «И». На один из его входов подадим синхросигнал SYNCB (потому что его синхроимпульсы как раз приходятся на границу тактов), а на другой вход - инвертированный последовательный двоичный код. На выходе из логического элемента «И» получим импульсы равные по длительности синхроимпульсам и располагающиеся только в тех тактах, в которых входящий в устройство последовательный двоичный код имеет низкий уровень, то есть кодирует логический ноль. Работа этого узла изображена на рисунке 1.5, где - это инвертированный последовательный двоичный код, SYNC B – синхросигнал, а нижняя кривая показывает результат логического умножения этих двух сигналов.

Для того чтобы сформировать импульс для входа S, который будет приходиться на границу тактов и обозначать служебный переход с низкого уровня на высокий, используем двухвходовый логический элемент «И». На один из его входов подадим синхросигнал SYNCB (потому что его синхроимпульсы как раз приходятся на границу тактов), а на другой вход - инвертированный последовательный двоичный код. На выходе из логического элемента «И» получим импульсы равные по длительности синхроимпульсам и располагающиеся только в тех тактах, в которых входящий в устройство последовательный двоичный код имеет низкий уровень, то есть кодирует логический ноль. Работа этого узла изображена на рисунке 1.5, где - это инвертированный последовательный двоичный код, SYNC B – синхросигнал, а нижняя кривая показывает результат логического умножения этих двух сигналов.

Рисунок 1.5 –

Для получения на вход S импульса, устанавливающего триггер в состояния логической единицы и соответствующего моменту кодирования единицы в Манчестере-2, т.е. располагающегося в середине такта, используем элемент «И», к входам которого подключаем последовательный двоичный код, на этот раз не инвертированный, и синхросигнал SYNC M. На выходе получаем в середине каждого такта, в котором последовательный двоичный код обладает высоким уровнем сигнал по длительности равный синхросигналу. Этот процесс визуализирован на рисунке 1.6.

Рисунок 1.6 –

Чтобы оба полученных на элементах «И» сигнала попали на информационный вход триггера S, складываем их посредством логического элемента «ИЛИ».

Практически такой же блок элементов необходимо подключить к входу R. В него также включены 2 элемента «И» и один «ИЛИ», а также элемент «НЕ» для инвертирования ПДК. Отличие заключается в том, что инвертированный ПДК логически перемножается с синхросигналом SYNCM, а не с SYNCB, как в предыдущем случае. Таким образом, мы получаем сигнал, вызывающий переключение триггера в состояния логического ноля в середине такта, в результате на выходе Q триггера в манчестерском коде происходит переход с высокого уровня на низкий в середине такта.

Соответственно, ко второму элементу «И» подключены ПДК и SYNCB, на выходе мы получаем сигнал, который позволяет производить служебное переключение уровней с низкого на высокий в манчестерском коде, при кодировании подряд идущих логических единиц.

Как видно из сказанного выше, логическая формула сигнала поступающего на вход S выглядит соответствующим образом:

![]() . (1)

. (1)

А для сигнала на вход Rформула имеет следующий вид:

![]() . (2)

. (2)

Рисунок 1.7 – Функциональная схема проектируемого кодера Манчестера-2

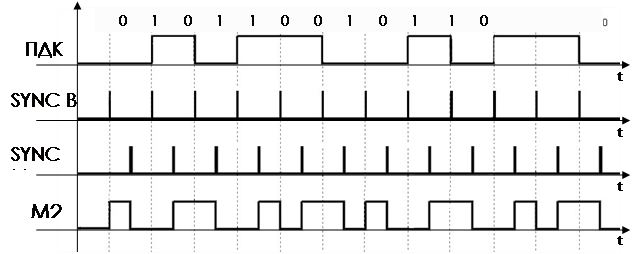

Временные диаграммы работы кодера Манчестера-2 построенного по данной функционально схеме, представлены на рисунке 1.8.

Рисунок 1.8 – Временные диаграммы работы кодера Манчестера-2

2. Расчет на структурном уровне

Проведём назначение требований к блокам функциональной схемы, представленной на рисунке 1.7, в соответствии с техническим заданием.

Так как проектируемый кодер Манчестера-2 не преобразует аналоговую величину в цифровую или наоборот, то отпадает необходимость рассчитывать уровни квантования и погрешности блоков. Это существенно уменьшает объём расчётов на структурном уровне.

Особенностью составленной функциональной схемы является то, что все блоки, кроме RS-триггера представляют собой стандартные логические вентили.

Наиболее критическим параметром для всех узлов проектируемого устройства является время задержки распространения сигнала (tPHL и tPLH ), которое, согласно эмпирически полученным значениям, для устойчивой и корректной работы кодера должно быть около 0,5 - 1 нс при длительности стробирующих синхроимпульсов – 2-3 нс, так как при предельной тактовой частоте работы кодера, равной 80 МГц, длина такта составляет всего 12,5 нс.

Согласно техническому заданию синхросигналы внешние, в уровнях КМДП ИС. Таким образом, верхний уровень напряжения равен 5В, нижний нулю. Длительность строб-импульса должна быть чуть больше или равна максимальной задержке логических вентилей используемых в устройстве, для их надёжного срабатывания. В устройство подаётся два вида синхросигнала: строб-импульсы первого приходятся на начало такта, стробы-импульсы второго на середину. Внешняя схемотехника, генерирующая синхроимпульсы отвечает за их тактовую синхронизацию с поступающим в устройство последовательным кодом.

Входное и выходное напряжение высокого уровня для сигнала для всех блоков должно равняться 5 В, а напряжение низкого уровня фактически нулю. RS-триггер, согласно указанным в техническом задании требованиям о величине внешней нагрузки, должен работать на нагрузку 50 Ом.

3. В ыбор элементов электрической схемы

Согласно условиям, поставленным в техническом задании, и расчёта на структурном уровне логические должен быть построен на базе КМДП-технологии и обладать высоким быстродействием – время задержки должно быть порядка 0,5 - 1 нс. Входное и выходное напряжение высокого уровня для сигнала для всех блоков должно равняться 5 В, а напряжение низкого уровня фактически нулю. Этим требования почти в полной мере удовлетворяют микросхемы быстродействующей серии ИС КР1554, разработанной по современной технологии обеспечивающей сочетание малого энергопотребления, характерного для КМДП схем, с высоким быстродействием, свойственного биполярным технологиям. Быстродействие КР1554 вполне удовлетворяет требованиям, поставленным в техническом задании, в любом случае более быстрые КМДП ИС в широком доступе отсутствуют [4]. (Западные аналоги серии КР1554 не превосходят её по быстродействию, так например инвертор КР1554ЛН1, имеет среднюю задержку распространения сигнала 3,5 нс и максимальную 7,0 нс, в то время как для зарубежного аналога этой микросхемы – 74ACT04 эти величины равны соответственно 4,5 и 7,5 нс). Кроме того вся серия КР1554 способна работать на нагрузку 50 Ом. Напряжение питания для всех элементов выбирается равным +5,5В, так как при таком значении быстродействие вентилей максимально, а также такое напряжение питания обеспечивает необходимое выходное напряжение высокого уровня в 5В.

Микросхемы серии КР1554 изготовляются по 1,4 мкм КМДП технологии с окисной изоляцией, поликремниевым затвором. Использование двухуровневой металлизации позволяет наряду с уменьшением размера кристалла, получить уменьшение амплитуды помех по шинам земли и питания [9].

3.1 Логические элементы «НЕ»

Для реализации логической операции инверсии сигналов используем микросхему КР1554ЛН1, состоящую из шести независимых логических вентилей (инверторов) в одном корпусе. Из шести мы используем в проектируемом устройстве только два. На рисунке 3.1 представлено условно-графическое представление этой микросхемы и таблица истинности, где H – высокий уровень напряжения, а L – низкий уровень.

| Входы | Выходы |

| DIn | DOn |

| H | L |

| L | H |

а) б)

Рисунок 3.1 – Таблица истинности (а) и условно-графическое обозначение (б) микросхемы КР1554ЛН1

В таблице 1 представлены важнейшие статические и динамические характеристики данной микросхемы в следующих условиях:

– напряжение питания UCC = 5В±0,5В,

– рабочая температура T = 25C°,

– емкость нагрузки CL =50 пф.

Таблица 1 – Важнейшие статические и динамические характеристики КР1554ЛН1

| Параметр | Значение | Ед. изм. |

| Входное напряжение высокого уровня (UIH ) | 3,85 (мин.) | В |

| Входное напряжение низкого уровня (UIL ) | 1,65 (макс.) | В |

| Выходное напряжение высокого уровня (UIH ) | 4,86 (мин.) | В |

| Выходное напряжение низкого уровня (UIL ) | 0,1 (макс.) | В |

| Входной ток (II ) | ±0,1 (макс.) | мкА |

| Время задержки распространения сигнала при включении (tPHL ) | 6,5 (макс.) | нс |

| Время задержки распространения сигнала при выключении (tPLH ) | 7.0 (макс.) | нс |

3.2 Логические элементы «2И»

Для реализации функции логического умножения сигналов используем микросхему КР1554ЛИ1, состоящую из четырёх независимых логических вентилей в одном корпусе. В проектируемом устройстве задействованы все четыре элемента 2И. На рисунке 3.2 представлено условно-графическое представление этой микросхемы и таблица истинности, где H – высокий уровень напряжения, а L – низкий уровень.

| Входы | Выходы | |

| DIx | DIy | DOn |

| L | L | L |

| L | H | L |

| H | L | L |

| H | H | H |

а) б)

Рисунок 3.2 – Таблица истинности (а) и условно-графическое обозначение (б) микросхемы КР1554ЛИ1

В таблице 2 представлены важнейшие динамические характеристики данной микросхемы в следующих условиях:

– напряжение питания UCC = 5В±0,5В,

– рабочая температура T = 25C°,

– емкость нагрузки CL =50 пф.

Таблица 2 – Важнейшие динамические характеристики КР1554ЛИ1

| Параметр | Значение | Ед. изм. |

| Время задержки распространения сигнала при включении (tPHL ) | 7,0 (макс.) | нс |

| Время задержки распространения сигнала при выключении (tPLH ) | 7.5 (макс.) | нс |

Статические характеристики полностью идентичны соответствующим характеристикам микросхемы КР1554ЛН1. Среднее значение задержки для всех элементов серии КР1554 равно 3,5 нс.

3.3 Логические элементы «2ИЛИ»

Для реализации функции логического сложения сигналов используем микросхему КР1554ЛЛ1, состоящую из четырёх независимых логических вентилей в одном корпусе. В проектируемом устройстве задействованы два вентиля 2ИЛИ. На рисунке 3.3 представлено условно-графическое представление этой микросхемы и таблица истинности, где H – высокий уровень напряжения, а L – низкий уровень.

| Входы | Выходы | |

| Dn.1 | Dn.2 | Dn |

| L | L | L |

| L | H | H |

| H | L | H |

| H | H | H |

а) б)

Рисунок 3.3 – Таблица истинности (а) и условно-графическое обозначение (б) микросхемы КР1554ЛЛ1

Статические характеристики и динамические характеристики КР1554ЛЛ1 полностью идентичны соответствующим характеристикам микросхемы КР1554ЛИ1, рассмотренной выше.

3.4 Асинхронный RS-триггер

Функцию асинхронного RS-триггера в проектируемом кодере Манчестера-2 могут выполнять микросхемы КР1554ТВ9, КР1554ТВ15, КР1554ТМ2 [9].

ИС КР1554ТВ9 и КР1554ТВ15 состоят из двух независимых JK-триггеров, имеющих общую цепь питания и асинхронные входы установки ![]() и сброса

и сброса ![]() c активным низким уровнем, что позволяет использовать их как RS-триггер. КР1554ТМ2 содержит два независимых D-триггера, каждый из которых имеет два дополнительных входа

c активным низким уровнем, что позволяет использовать их как RS-триггер. КР1554ТМ2 содержит два независимых D-триггера, каждый из которых имеет два дополнительных входа ![]() и

и ![]() асинхронной установки триггера в единичное и нулевое состояние.

асинхронной установки триггера в единичное и нулевое состояние.

Однако в ходе разработки было выяснено, что наиболее оптимальным решением является реализация RS-триггера на базе двух логических вентилей ИЛИ-НЕ [5]. Такую функцию реализует микросхема КР1554ЛЕ1, состоящая из четырёх вентилей ИЛИ-НЕ в одном корпусе. Причины такого решения вполне очевидны: два логических элемента обладают меньшим энергопотреблением, большим быстродействием (9,5 нс для микросхем КР1554ТВ9, КР1554ТВ15 и КР1554ТМ2 против 6,5 нс для КР1554ЛЕ1 выполняющего функцию 2ИЛИ-НЕ), и, в конечном счёте, меньшей аппаратной избыточностью (в структуру производимых промышленностью микросхем-триггеров входит 20-24 логических элемента, в то время как функцию RS-триггера можно реализовать всего лишь на двух), чем микросхемы КР1554ТВ9, КР1554ТВ15 и КР1554ТМ2. На рисунке 3.4 показана структурная схема асинхронного RS-триггера на двухвходовых логических элементах ИЛИ-НЕ, а также его таблица переходов и временная диаграмма.

| S | R | Qn+1 |

| 1 | 0 | 1 |

| 0 | 1 | 0 |

| 0 | 0 | Qn |

| 1 | 1 | X |

а) б) в)

Рисунок 3.4 – Структурная схема асинхронного RS-триггера на логических элементах ИЛИ-НЕ (а), его таблица переходов (б) и временные диаграммы (в)

Полная схема кодера Манчестера-2, полученная после объединения описанных выше элементов, показана на рисунке 2.9.

Рисунок 3.5 – Преобразователь кода в Манчестер-2

4. Электрическое моделирование

Рисунок 4.1 – Схема преобразователя кода для моделирования.

Осуществим моделирование полученного преобразователя последовательного двоичного кода в Манчестер-2 в пакете программ схемотехнического моделирования Micro-Cap 7. Благодаря простоте устройства смоделировать работу сразу всего кодера, а не отдельных его узлов. Схема для моделирования представлена на рисунке 4.1.

В качестве источника последовательного кода используем генератор цифровых сигналов Stim1. Зададим цифровой сигнал, например, зацикленную последовательность из шести бит 011010. Данная последовательность выбрана, потому что в ней присутствует все виды переходов и чередований: переход с логического нуля в логическую единицу и наоборот, подряд идущие единицы и нули (два подряд идущих нуля получаются на стыке циклов, каждый из которых начинается и заканчивается нулем). Частоту последовательного двоичного кода установим максимально возможную из рабочего диапазона частот устройства – 80 МГц. При такой частоте длина одного такта составит

![]() . (3)

. (3)

Окно свойств генератора цифровых сигналов Stim1 c заданными атрибутами представлено на рисунке 4.2.

Сходным образом зададим параметры для генераторов синхросигнала, роль которых также будет выполнять Stim1. Длительность строб-импульса возьмём для удобства равной 1 наносекунде, хотя в идеальном случае длительность строба может быть бесконечно малой. Строб-импульс SYNCB будет находиться в начале такта, а строб SYNCM смещён на полтакта, то есть на 6,25 нс. Окно свойств компонентов Stim1, выполняющих роль генераторов синхроимпульсов представлено на рисунке на 4.3.

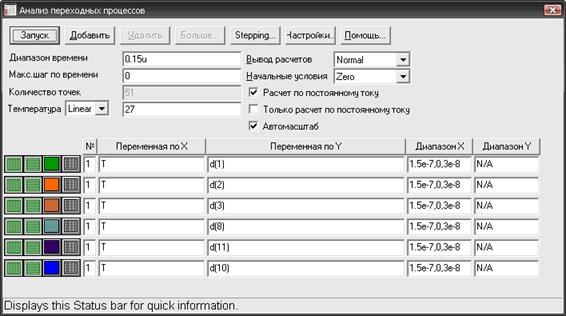

В первую очередь проведём моделирование без задержек, чтобы проверить правильно ли в принципе работает созданная схема. Для всех логических компонентов, содержащихся в схеме, в таком режиме моделирования устанавливаются нулевые задержки. Тип моделирования – анализ переходных процессов, длительность моделирования равна 150 нс. Окно настроек моделирования показано на рисунке 4.4.

Рисунок 4.2 – Окно свойств компонента генерирующего входящий двоичный сигнал

а)

а)

б)

б)

Рисунок 4.3 – Окна свойств генераторов синхросигналов SYNCB (а) и SYNC М (б)

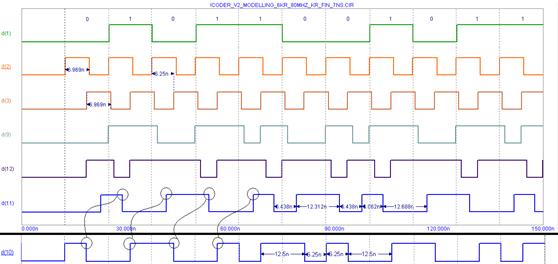

В свойствах анализа переходных процессов задаем построение временных диаграмм работы генератора последовательного двоичного кода (значения с 1-го узла), генератора синхросигнала SYNCB (значения с 2-го узла), генератора синхросигнала SYNCM (значения с 3-го узла), логического входа S асинхронного RS-триггера (значения с 11-го узла), логического входа R (значения с 11-го узла). Конечный результат работы схемы в виде сигнала в коде Манчестер-2 получаем на выходе QRS-триггера (10-ый узел схемы).

Рисунок 4.4 – Окно свойств анализа переходных процессов

Рисунок 4.5 – Моделирование работы кодера Манчестера-2

На рисунке 4.5 представлены временные диаграммы работы некоторых узлов проектируемого устройства, полученные в результате моделирования в среде Micro-CAP. Как видно из картины моделирования в идеальных условиях, при нулевой задержке на логических элементах, схема работает корректно. Строб-импульсы располагаются на соответствующих местах: стробы синхросигнала SYNCB в начале каждого такта (такты для наглядности отмечены пунктирной линией), и чередуются через каждые 12,5 нс, приходясь соответственно на 12,5 нс, 25 нс, 37,5 нс, 50 нс и так далее. Ровно на 6,25 нс от него отстаёт строб синхросигнала SYNCM и приходится на середину такта, как и полагается по теоретическим выкладкам. Стробированные сигналы без искажений и замедлений, пройдя через цепочку логических вентилей, поступают на входы S (d(11)) и R (d(8)) входы триггера, вызывая необходимые для формирования Манчестера-2 переключения логических уровней. И в результате на 10-ом узле мы получаем искомый сигнал в Манчестерском кодировании. В его правильности легко убедится, визуально анализируя временные диаграммы. Действительно, на логический нуль последовательного двоичного кода всегда приходится переход манчестерского кода с верхнего уровня на нижний и наоборот. Также корректно осуществляются рабочие переходы с уровня на уровень при кодировании подряд идущих нулей и единиц. Таким образом, мы убедились, что схема принципиально работает правильно.

Однако в реальности не существует элементов с мгновенным быстродействием, поэтому необходимо исследовать, будет ли соответствовать данное устройство требованиям, предъявляемым техническим заданием, при использовании реального элементного базиса. На этапе выбора элементов проектируемого устройства было принято решение использовать наиболее быстродействующие на данный момент КМПД микросхемы серии КР1554. Задержки распространения сигнала реальных логических вентилей были внесены в параметры компонентов используемых в Micro-CAP. Свойства элементов с внесёнными реальными параметрами приведены на рисунке 4.6.

а)

а)

б)

б)

в)

в)

г)

г)

Рисунок 4.6 – Параметры логических элементов входящих в моделируемую схему: элемент «НЕ» (а), элемент «И» (б), элемент «ИЛИ» (в), элемент «ИЛИ-НЕ» (г)

После задания реальных задержек для логических элементов, было анализ переходных процессов, он показал достаточно странную картину, приведённую на рисунке 4.7.

Рисунок 4.7 – Моделирование с задержками при длительности стробов 1 нс

Рисунок 4.7 – Моделирование с задержками при длительности стробов 1 нс

Логические вентили, несмотря на поступающие, на их логические входы сигналы, на выходе давала лишь непрерывный низкий уровень. В результате анализа данной ситуации было выяснено, что причиной такого поведения логических элементов является то, что элемент не реагирует на сигнал, длительность которого меньше, чем среднее время задержки распространения сигнала в данном логическом элементе. Путем многократного моделирования с различными длительностями строб-импульса, было выяснено, что устройство корректно работает, начиная с длительности 4 нс, однако конечный сигнал в Манчестерском коде при этом сильно искажен, что может привести к ошибкам декодирования на устройстве, принимающем закодированный сигнал. Оптимальная длительность строб-импульса равна 7 нс, так как искажение выходящего из кодера сигнала при этом минимально возможное (на частоте 80 МГц). Полученные при таких условиях временные диаграммы приведены на рисунке 4.8.

Рисунок 4.8 – Моделирование с задержками при длительности стробов 7 нс

В нижней части рисунка 4.8 помещена временная диаграмма кода Манчестер-2 полученного без задержек. Она позволяет визуально оценить время задержки устройства в целом и, сравнивая, убедится в правильности кодирования при наличии задержек у элементов схемы. Согласно измерениям, сделанным в Micro-CAP, задержка распространения сигнала, создаваемая кодером равно 16,5 или 20 нс, в зависимости от пути прохождения сигнала в кодере. Убедится, в этом можно взглянув на рисунок 4.9.

Разница в 3,5 нс объясняется темп, что в некоторых случаях сигналу нужно пройти через инверторы, которые добавляют эти 3,5 нс, а в некоторых – нет.

В результате проведённого моделирования мы удостоверились, что созданное устройство удовлетворяет требованиям, поставленным в техническом задании, и корректно кодирует последовательный двоичный код в код Манчестер-2 с небольшой задержкой в 20 нс.

5. Анализ метрологических характеристик

Для подтверждения работоспособности проектируемого устройства «Преобразователь кода» из последовательного двоичного в Манчестер-2 и соответствия его требованиям технического задания приведем его основные характеристики:

– Обеспечено кодирование поступающего последовательного двоичного сигнала с верхним уровнем 5 В и нижним ≈0 В в код униполярный двухуровневый Манчестер-2, также обладающим напряжением верхнего уровня 5В, при параллельном поступлении двух синхросигналов, отличающихся друг от друга на время поступления строб-импульсов: у первого синхросигнала строб-импульс в начале каждого такта, у второго – в середине. Подтверждено в ходе моделирования.

– Устройство способно корректно работать во всём диапазоне тактовых частот вплоть до 80 МГц.

– Обеспечена возможность работы на внешнюю нагрузку 50 Ом.

Список использованных источников

1 Хвощ С.Т. и др. Организация последовательных мультиплексных каналов систем автоматического управления / С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой; Под общ. ред. С.Т. Хвоща – СПб.: Машиностроение, 1989. – 271 с.

2 Никонов А.В. Электротехника и электроника: Конспект лекций.- Омск: Изд-во ОмГТУ, 2005. – 84 с.

3 Никонов А.В. Основные узлы цифровых измерительных устройств: Учебное пособие. Омск: Издательство ОмГТУ, 2001. – 50 с.

4 Никонов А.В., Никонова Г.В. Разработка электрических функциональных устройств: Методическое указание для курсового проектирования. Омск: Издательство ОмГТУ, 2005. – 66 с.

5 Забродин Ю.С. Промышленная электроника: Учебн. для вузов. – М.: Высшая школа, 1982. – 496 с.

6 Одинец А.И. Цифровые устройства: Учеб. Пособие. – Омск: Изд-во ОмГТУ, 2000. – 64 с.

7 Разевиг В.Д. Схемотехническое моделирование с помощью Micro-CAP 7.– М.: Горячая линия–Телеком, 2003.– 368 с.

8 Хоровиц П., Хилл У. Искусство схемотехники: В 2-х т. Т.1. Пер. с англ. Изд. 2-е, стереотип.— М.: Мир, 1984. – 601 с.

9 Логические ИС. КР1533, КР1554: Справочник в 2-х ч. Ч.2. / Сост.: Е.П. Лисовый – М.: Книга, 1997. – 496 с.

10 Нефедов, А.В Интегральные схемы и их зарубежные аналоги: В 8-х т. Т.6 Серии К565-599. – М.: Высшая школа, 1997 – 511 с.

11 Олифер В.Г. Основы четей передачи данных: курс лекций / В.Г. Олифер, Н.А. Олифер, Интернет ун-т информ. технологий. – М.: Интернет-Ун-т Информ. Технологий, 2003. – 246 с.

12Олифер В.Г. Компьютерные сети. Принципы, технологии, протоколы: учебник для вузов / В.Г. Олифер, Н.А. Олифер. – 3-е изд. – СПб: Питер, 2006 – 957 с.

13 Халсалл, Фред. Передача данных, сети компьютеров и взаимосвязь открытых систем Ф. Халсалл; Пер. с англ. Т. М. Тер-Микаэляна – М.: Радио и связь, 1995 – 408 с.

14 Гук, М. Аппаратные средства локальных сетей: энцкл. / М. Гук, Гл. ред. Е. Строганова. – СПб.: Питер, 2001. – 572 с.

15 Алексенко А.Г. Основы микросхемотехники. Элементы морфологии микроэлектронной аппаратуры. – 2-е изд., перераб и доп. М.: Сов. радио, 1977 – 408 с.

16 Потемкин И.С. Функциональные узлы цифровой автоматики. – М.: Энергоатомиздат, 1988. – 320 с.

16. Александров К.К, Кузьмина Е.Г, Электротхнические чертежи и схемы. – М.: Энергоатомиздат, 1990. – 288 с.

17 Шило В.Л. Популярные микросхемы КМОП: Справочник – М.: «Ягуар», 1993. – 63 с.

18 Бирюков, С.А. Цифровые устройства на МОП - интегральных микросхемах – М: Радио и связь, 1990 – 576 с.