| Скачать .docx |

Курсовая работа: Курсовая работа: Синтез управляющего устройства процессора в форме Автомата Мили

РОССИЯ

Федеральное агентство связи

Бурятский филиал ГОУ ВПО СибГУТИ

КУРСОВАЯ РАБОТА

по дисциплине: «Вычислительная техника»

|

на тему: Синтез управляющего устройства процессора в форме «Автомата Мили»

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

Руководитель работы:

Выполнил студент:

группы: 3М-07(2)

Улан-Удэ2008 г.

Содержание

Введение

1. Постановка задач

2. Основная часть

2.1 Теоретические основы процессоров

2.1.1. Построение процессоров

2.1.2. Общая структура процессоров

2.1.3. Цифровые автоматы

2.2. Практическая часть

2.2.1. Определение состояний ЦА

2.2.2. Расчёт количества триггеров и кодирование состояний ЦА

2.2.3. Структурная схема управляющего устройства

2.2.4. Построение графа функционирования устройства

2.2.5. Заполнение таблицы функционирования устройства

2.2.6. Запись логических выражений в заданном базисе

2.2.7. Выбор микросхем

2.2.8. Описание работы

3.Заключение

4. Список используемой литературы

Задание

Постановка задачи:

По заданному алгоритму функционирование управляющего устройства процессора с жесткой логикой синтезировать принципиальную электрическую схему на заданной серии интегральных микросхем и типы триггеров.

Начальное состояние цифрового автомата для всех вариантов взять а0 .

Исходные данные:

| № варианта | № алгоритма | Серия ИМС | Тип триггера |

| 3 | 3 | КР1533 | ТМ8 |

Введение

В наступившем двадцать первом веке человечество не мыслит себя без цифровых технологий. Цифровое телевидение, цифровая фото и видео съёмка, цифровая сотовая и стационарная связь и т. д.; человек пользуется этими благами цивилизации, не задумываясь о том, как и что там работает. А ведь там происходят очень сложные действия над информацией, представленной в двоичной системе счисления.

Устройства, которые обеспечивают цифровую обработку информации, называются цифровыми. Эти устройства выполнены на цифровых интегральных микросхемах, что позволяет значительно уменьшить габариты устройств, массу, потребляемую мощность, стоимость и намного улучшить надёжность. Применение технологий больших и сверхбольших интегральных микросхем позволило перенести компьютеры из лабораторий и специальных учреждений в каждый дом. Помимо улучшения качества и надёжности аппаратуры интегральные микросхемы также влияют на производительность и качество труда человека, посредством того, что работа становится автоматизированной и, следовательно, увеличивается в разы вычислительная способность и уменьшается риск ошибки.

С появлением цифровых устройств в технике связи стало возможным предоставление огромного числа услуг, улучшилось качество связи и увеличился объём передаваемой информации.

Вершиной цифровой техники является микропроцессор. Мало кто знает, что в современных японских автомобилях автоматической подкачкой колёс управляет микропроцессор.

Микропроцессорные устройства широко используются в аппаратуре, которая обеспечивает обмен, обработку, распределение информации. Поэтому нам, связистам необходимы знания в области вычислительной техники. Углубить полученные в курсе лекций знания нам поможет данная курсовая работа. Мы будем синтезировать управляющее устройство процессора и ознакомимся с принципом его работы.

2. Основная часть

2.1 Теоретическая часть

2.1.1 Построение процессоров

Существует два подхода к проектированию микропрограммного автомата: использование принципа схемной (жёсткой) логики или принципа программируемой логики.

При использовании процессора со схемной логикой при проектировании выбирается набор микросхем и выбирается та схема, которая обеспечивает требуемое функционирование. Устройства, построенные по такому принципу, способны обеспечить наивысшее быстродействие. Недостаток: трудность использования интегральных микросхем большой и сверхбольшой степени интеграции. Это связано с тем, что для разных процессоров потребуются различные БИС. Число БИС окажется большим, а потребность в каждом типе БИС окажется низкой.

Принцип программируемой логики предполагает использование одной или нескольких БИС некоторого универсального устройства, функционирование которого обеспечивается заключением в память устройства определённой программы. В зависимости от программы такое устройство может выполнить самые разнообразные функции. Число БИС окажется небольшим, а потребность БИС каждого типа высокой.

2.1.2 Общая структура процессоров

Процессор осуществляет непосредственно обработку данных и программное управление процессом обработки данных. Он синтезируется в виде соединения двух устройств: операционного и управляющего (рис. 1)

Вход данных

Вход данных

U1 U2.. Un

Y1 Х1

Y2

x s+1

Yn XS

XL

|

Z1 Z2 ..Zn

Выход данных

![]()

![]() Операционное устройство (ОУ) – устройство, в котором выполняются операции. Оно включает в качестве узлов регистры, сумматоры, каналы передачи информации, мультиплексоры для коммутации каналов, шифраторы, дешифраторы и т. д. Управляющее устройство (УУ) координирует действия узлов операционного устройства; оно вырабатывает в некотором временной последовательности управляющие сигналы, под действием которых в узлах операционного устройства выполняются требуемые действия.

Операционное устройство (ОУ) – устройство, в котором выполняются операции. Оно включает в качестве узлов регистры, сумматоры, каналы передачи информации, мультиплексоры для коммутации каналов, шифраторы, дешифраторы и т. д. Управляющее устройство (УУ) координирует действия узлов операционного устройства; оно вырабатывает в некотором временной последовательности управляющие сигналы, под действием которых в узлах операционного устройства выполняются требуемые действия.

Процесс функционирования операционного устройства распадается на последовательность элементарных действий в его узлах:

1) установка регистра в некоторое состояние (например, запись в регистр R1 числа 0, обозначаемая R1 ← 0);

2) инвертирование содержимого разрядов регистра (например, если регистр R2 содержал двоичное число 101101, то после инвертирования его содержимое будет равно 010010; такое действие обозначают R2 ← (![]() ));

));

3) пересылка содержимого одного узла в другой (например, пересылка содержимого регистра R2 в регистр R1, обозначаемая R1 ← (R2));

4) сдвиг содержимого узла влево, вправо (например, сдвиг на один разряд влево содержимого регистра R1, обозначаемый R1 ← СдвЛ (R1));

5) счет, при котором число в счетчике (регистре) возрастает или убывает на единицу (Сч ← (Сч ±1));

6) сложение (например, R2 ← (R2) + (R1));

7) сравнение содержимого регистра на равенство с некоторым числом; результат сравнения: лог.1 (при выполнении равенства) либо лог.0 (при невыполнении равенства);

8) некоторые логические действия (поразрядно выполняемые операции конъюнкции, дизъюнкции и др.).

Каждое такое элементарное действие, выполняемое в одном из узлов ОУ в течение одного тактового периода, называется микрооперацией.

В определенные тактовые периоды одновременно могут выполняться несколько микроопераций, например R2 ← 0, Сч ← (Сч)-1. Такая совокупность одновременно выполняемых микроопераций называется микрокомандой, а весь набор микрокоманд, предназначенный для решения определенной задачи, - микропрограммой.

Таким образом, если в операционном устройстве предусматривается возможность исполнения n различных микроопераций, то из управляющего устройства выходят n управляющих цепей, каждая из которых соответствует определенной микрооперации. И если необходимо в операционном устройстве выполнить некоторую микрооперацию, достаточно из управляющего устройства по определенной управляющей цепи, соответствующей этой микрооперации, подать сигнал (например, напряжение уровня лог.1). В силу того, что управляющее устройство определяет микропрограмму, т.е. какие и в какой временной последовательности должны выполняться микрооперации, оно получило название микропрограммного автомата.

Формирование управляющих сигналов Y1 ,…,Yn (рис.1) для выполнения микрокоманд может происходить в зависимости от состояния узлов операционного устройства, определяемого сигналами Х1 ,…,ХS , которые подают с соответствующих выходов операционного устройства на входы управляющего устройства. Управляющие сигналы Y1 ,…,Yn могут также зависеть от внешних сигналов ХS +1 , …, ХL .

Для сокращения числа управляющих цепей, выходящих из управляющего устройства (в тех случаях, когда оно конструктивно выполняется отдельно от операционного), микрокоманды могут кодироваться.

2.1.3 Цифровые автоматы.

Цифровые автоматы – это логическое устройство, в которых помимо логических элементов имеются элементы памяти. Значение выходных сигналов такого устройства зависит не только от аргументов на входе в данный момент времени, но и от предыдущего состояния автомата, которое фиксируется элементами памяти. В качестве элементов памяти могут использоваться триггеры. Каждое внутреннее состояние цифрового автомата определяется исходным состоянием триггеров и последовательностью входных сигналов, действующих на входе в данный момент времени, поэтому такие устройства называются последовательностными схемами. К последовательностным схемам можно отнести: триггеры, счетчики, регистры.

В общем случае структурная схема цифрового автомата может быть представлена в виде набора трех узлов: комбинационной схемы формирования выходных сигналов, комбинационной схемы формирования сигналов управления триггерами и, собственно, памяти (рис.2)

Рис.2. Управляющее устройство со схемной логикой.

На вход комбинационной схемы управления триггерами поступают комбинации входных сигналов Х1 , Х2 ,…ХК , комбинации сигналов, отражающих состояние элементов памяти Q1 , Q2 ,…Qm . С учетом этих множеств комбинационная схема формирует серии сигналов, управляющих состоянием триггеров. Кодовые комбинации состояния триггеров образуют внутренние состояния цифрового автомата, которые принято обозначать буквой а .

Комбинационная схема формирования выходных сигналов создает сигналы У1 , У2 ,…УР . которые могут использоваться для управления некоторыми узлами, для активизации процессов в других схемах. Эти сигналы могут зависеть только от внутренних состояний: в этом случае устройство принято называть автоматом Мура. А если выходные сигналы зависят и от входных сигналов Х1 , Х2 ,…ХК, то – автоматом Мили.

Таким образом, для задания цифрового автомата необходимы три множества:

- множество входных сигналов: Х1 , Х2 ,…ХК ;

- множество выходных сигналов: У1 , У2 ,…УР ;

- множество внутренних состояний: а1 , а2 ,…аZ .

На указанных трех множествах задают две функции: функцию переходов и функцию выходов. Для автомата Мили эти функции имеют вид:

а ( t +1) = f( a ( t ), ( x ( t ))

y( t ) = φ( a ( t ), x ( t )) ;

где а ( t +1) – новое состояние цифрового автомата;

a(t) – предыдущее состояние автомата;

y( t ) – выходные сигналы текущего времени;

x(t)- сигналы на входе в данный момент времени.

Для автомата Мура:

а ( t +1) = f( a ( t ), ( x ( t ))

y( t ) = φ( a ( t )) ;

Последовательность действий автомата по формированию выходных сигналов и сигналов управления триггерами с учетом выходных сигналов может быть задана с помощью алгоритма. Алгоритм фактически является формализованным представлением задачи по построению цифрового устройства, где определены группы выходных сигналов для инициализации устройств схемы (например, операционное устройство процесса в зависимости от поступления тех или иных входных сигналов - х). Задавать цифровой автомат удобно с помощью графа. Графом называется непустое конечное множество узлов (вершин) вместе с множеством дуг (ветвей), соединяющих пары различных узлов. Граф обычно представляется в наглядной форме, при этом вершины изображаются точками или кругами, которые помечаются с целью идентификации, а ветви изображаются линиями, соединяющими соответствующие узлы. Если каждой дуге также приписано направление, то такой граф называется ориентированным. Если направления не указаны, то граф называется неориентированным. Данные представления полезны ввиду их наглядности.

Вершины обычно соответствуют объектам некоторого вида (в цифровом автомате – внутренним состоянием), а дуги – физическим или логическим связям между ними.

Таким образом, графы можно использовать для математического моделирования самых разнообразных систем и структур: электрических схем, вычислительных сетей и т.д.

2.2 Практическая часть.

2.2.1 Определение состояний ЦА.

На заданной по варианту блок-схеме алгоритма проставим состояния цифрового автомата. Новым состоянием обозначается вход блока следующего за “процессом”. За исходное состояние возьмём а0.

Состояние цифрового автомата изменится после каждого блока «процесс», т. к. данный блок указывает на выходные сигналы, сформированные автоматом при заданном переходе. Состояния следует проставлять по возрастанию. На алгоритме каждое новое состояние автомата фиксируется крестиком на стрелке перехода к следующему блоку и проставлено буквенное обозначение с соответствующим индексом.

В результате получили 11 разных состояний переходов автомата. Далее этим состояниям присваивается двоичный код. Для того, чтобы было меньше разрядов, а следовательно и меньше триггеров воспользуемся двоичным кодом «8-4-2-1». Соответствие кодовых комбинаций внутренним состояниям приведено в таблице 2.

2.2.2. Расчет числа триггеров

Для расчета числа триггеров воспользуемся формулой:

N≥log2 an

где an – количество состояний в алгоритме

N= log2 an = log2 11 = 3,26 ≈ 4.

Для всех состояний автомата достаточно выбрать триггер как минимум с четырьмя выходами «Q». Каждый выход фиксируется в таблице, затем этому выходу присваивается «0» или «1» в зависимости от выбранного состояния автомата.

Таблица 1. Кодирование состояний цифрового автомата

| Состояние | Выходтриггера | |||

| ai | Q4 | Q3 | Q2 | Q1 |

| a0 | 0 | 0 | 0 | 0 |

| a1 | 0 | 0 | 0 | 1 |

| a2 | 0 | 0 | 1 | 0 |

| a3 | 0 | 0 | 1 | 1 |

| a4 | 0 | 1 | 0 | 0 |

| a5 | 0 | 1 | 0 | 1 |

| a6 | 0 | 1 | 1 | 0 |

| a7 | 0 | 1 | 1 | 1 |

| a8 | 1 | 0 | 0 | 0 |

| a9 | 1 | 0 | 0 | 1 |

| a10 | 1 | 0 | 1 | 0 |

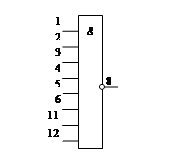

2.2.3 Структурная схема управляющего устройства

Структурная схема управляющего устройства приведена на рис. .

Входами комбинационного узла будут являться выходы триггеров (Q1; Q2; Q3; Q4), а также условные переходы (Х1; Х2; Х3; Х4; Х5).

Выходами будут являться сигналы (У1; У2; У3; У4; У5; У6) и сигналы управления триггерами (D1; D2; D3; D4). Также на триггеры подаются сигналы синхронизации (С) и сигналы установки нуля (R).

Рис.4. Структурная схема управляющего устройства.

2.2.4. Построение графа функционирования устройства.

Граф функционирования устройства строится на основе, данного в задании курсовой работы алгоритма работы, управляющего устройства. Для того чтобы начать составление нужно отметить на алгоритме все состояния устройства (а0 ... а10). Эти состояния и определят узлы графа. Кругами обозначаются состояния, а дугами переходы из одного состояния в другое. На дугах указываются условные переходы Xi, а также выходные сигналы Yi

Рис 5. Граф функционирования

2.2.5. Заполнение таблицы работы

Для заполнения таблицы работы нам понадобится таблица переходов D-триггера(табл.2).

Табл.2. Таблица переходов D-триггеров

| Переход | D |

| 0 → 0 | 0 |

| 0 → 1 | 1 |

| 1 → 0 | 0 |

| 1→ 1 | 1 |

Табл.3 . Таблица работы

| Состояние автомата | Условные переходы | Выходные сигналы | |||||||||

| исходное | новое | ||||||||||

| ai | Q4 | Q3 | Q2 | Q1 | ai | Q4 | Q3 | Q2 | Q1 | Xi | Ji; Ki; Yi |

| a0 | 0 | 0 | 0 | 0 | a1 | 0 | 0 | 0 | 1 | ----- | D1; Y1, Y2 |

| a1 | 0 | 0 | 0 | 1 | a2 | 0 | 0 | 1 | 0 | ----- | D2; Y2, Y3, Y4 |

| a2 | 0 | 0 | 1 | 0 | a3 | 0 | 0 | 1 | 1 | ----- | D1,D2; Y1, Y3, Y4, Y6 |

| a3 | 0 | 0 | 1 | 1 | a4 | 0 | 1 | 0 | 0 | D3; Y2 | |

| a3 | 0 | 0 | 1 | 1 | a5 | 0 | 1 | 0 | 1 | X2 | D1, D3; Y2, Y5, Y6 |

| a4 | 0 | 1 | 0 | 0 | a6 | 0 | 1 | 1 | 0 | X3 | D2,D3; Y1, Y5, Y6 |

| a4 | 0 | 1 | 0 | 0 | a7 | 0 | 1 | 1 | 1 | D1, D2,D3; Y2, Y3,Y4 | |

| a6 | 0 | 1 | 1 | 0 | a10 | 1 | 0 | 1 | 0 | D2, D4; Y5, Y6 | |

| a6 | 0 | 1 | 1 | 0 | a8 | 1 | 0 | 0 | 0 | X5 | D4; Y5 |

| a7 | 0 | 1 | 1 | 1 | a0 | 0 | 0 | 0 | 0 | X4 | ---------- |

| a7 | 0 | 1 | 1 | 1 | a8 | 1 | 0 | 0 | 0 | D4; Y5 | |

| a8 | 1 | 0 | 0 | 0 | a9 | 1 | 0 | 0 | 1 | X1 | D1,D4; Y2, Y6 |

| a8 | 1 | 0 | 0 | 0 | a0 | 0 | 0 | 0 | 0 | Y2, Y4, Y5 | |

| a9 | 1 | 0 | 0 | 1 | a10 | 1 | 0 | 1 | 0 | ----- | D2, D4; Y5, Y6 |

| a10 | 1 | 0 | 1 | 0 | a1 | 0 | 0 | 0 | 1 | ----- | D1; Y1, Y2, Y5 |

| a5 | 0 | 1 | 0 | 1 | a7 | 0 | 1 | 1 | 1 | ----- | D1,D2,D3; Y2, Y3, Y4 |

Таблица заполняется по графу (рис.4). Строк в таблице будет столько, сколько дуг в графе. Пример заполнения: для примера возьмём девятую строку, состояние автомата «а6» (кодируемое как «0110») переходит в состояние «а8 » (кодируемое как «1000»). Мы видим, что «Q2» и «Q3» были равны 1, а стали равны 0. Так как по варианту задан D-триггер, то по таблице переходов D -триггера видим, что нужно подать «0» на входы «D2» и «D3», на вход «D4» надо подать «1», для того чтобы «Q4» установился в «1», эти изменения вносим в графу «Сигналы управления триггерами; выходы КУ». Так же мы видим, что должны быть сформированы выходной сигнал У5, эти сигналы так же вносим в графу «Сигналы управления триггерами; выходы КУ». Этот переход условный, поэтому в столбце «Условие перехода» заносим условный переход «Х5». Аналогично заполняются остальные строки таблицы.

2.2.6. Выведение уравнений работы автомата.

После заполнения таблицы № 4 переходим к записи выходных уравнений в СДНФ:

![]() D1 = a0 V a2 V a3 * x2 V a4 * x3 V a8 * x1 V a10 V a5

D1 = a0 V a2 V a3 * x2 V a4 * x3 V a8 * x1 V a10 V a5

![]()

![]() D2 = a1 V a2 V a4 * x3 V a4 *x3 V a6 * x5 V a9 V a5

D2 = a1 V a2 V a4 * x3 V a4 *x3 V a6 * x5 V a9 V a5

![]()

![]() D3 = a3 * x2 V a3 * x2 V a4 * x3 V a4 * x3 V a5

D3 = a3 * x2 V a3 * x2 V a4 * x3 V a4 * x3 V a5

![]()

![]() D4 = a6 * x5 V a6 * x5 V a7 * x4 V a8 * x1 V a9

D4 = a6 * x5 V a6 * x5 V a7 * x4 V a8 * x1 V a9

Y1 = a0 V a2 V a4 * x3 V a10

![]()

![]()

![]() Y2 = a0 V a1 V a3 * x2 V a3 * x2 V a4 * x3 V a8 * x1 V a8 * x1 V a10 V a5

Y2 = a0 V a1 V a3 * x2 V a3 * x2 V a4 * x3 V a8 * x1 V a8 * x1 V a10 V a5

![]() Y3 = a1 V a2 V a4 * x3 V a5

Y3 = a1 V a2 V a4 * x3 V a5

![]()

![]() Y4 = a1 V a2 V a4 * x3 V a8 * x1 V a5

Y4 = a1 V a2 V a4 * x3 V a8 * x1 V a5

![]()

![]()

![]() Y5 = a3 * x2 V a4 * x3 V a6 * x5 V a6 * x5 V a7 * x4 V a8 * x1 V a10 V a9

Y5 = a3 * x2 V a4 * x3 V a6 * x5 V a6 * x5 V a7 * x4 V a8 * x1 V a10 V a9

![]() Y6 = a2 V a3 * x2 V a4 * x3 V a6 * x5 V a8 * x1 V a9

Y6 = a2 V a3 * x2 V a4 * x3 V a6 * x5 V a8 * x1 V a9

Теперь полученные уравнения мы можем минимизировать с помощью закона склеивания, также для упрощения принципиальной схемы мы можем применить правило Де Моргана. Таким образом, уравнения будут иметь вид:

D1 = a0 & a2 & a3 * x2 & a4 * x3 & a8 * x1 & a10 & a5

D2 = a1 V a2 V a4 * (x3 V x3) V a6 * x5 V a9 V a5 = a1 & a2 & a4 & a6 * x5 & a9 & a5

D3 = a3 * (x2 V x2) V a4 * (x3 V x3) V a5 = a3 & a4 & a5

D4 = a6 * (x5 V x5) V a7 * x4 V a8 * x1 V a9= a6 & a7 * x4 & a8 *x1 & a9

![]()

![]()

![]() Y1 = a0 & a2 & a4 * x3 & a10

Y1 = a0 & a2 & a4 * x3 & a10

![]()

![]()

![]() Y2 = a0 V a1 V a3 * (x2 V x2) V a4 * x3 V a8 * (x1 V x1) V a10 V a5 =

Y2 = a0 V a1 V a3 * (x2 V x2) V a4 * x3 V a8 * (x1 V x1) V a10 V a5 =

![]()

![]()

![]()

![]()

![]()

![]() = a0 & a1 & a3 & a4 * x3 & a8 & a10 & a5

= a0 & a1 & a3 & a4 * x3 & a8 & a10 & a5

![]()

![]()

![]()

![]() Y3 = a1 & a2 & a4 * x3 & a5

Y3 = a1 & a2 & a4 * x3 & a5

![]()

![]()

![]()

![]()

![]() Y4 = a1 & a2 & a4 * x3 & a8 * x1 & a5

Y4 = a1 & a2 & a4 * x3 & a8 * x1 & a5

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Y5 = a3 * x2 V a4 * x3 V a6 * (x5 V x5) V a7 * x4 V a8 * x1 V a10 V a9 = a3 * x2 & a4 * * x3 & a6 & a7 * x4 & a8 * x1 & a10 & a9

Y5 = a3 * x2 V a4 * x3 V a6 * (x5 V x5) V a7 * x4 V a8 * x1 V a10 V a9 = a3 * x2 & a4 * * x3 & a6 & a7 * x4 & a8 * x1 & a10 & a9

![]()

![]()

![]() Y6 = a2 & a3 * x2 & a4 * x3 & a6 * x5 & a8 * x1 & a9

Y6 = a2 & a3 * x2 & a4 * x3 & a6 * x5 & a8 * x1 & a9

2.2.7 Выбор микросхем в заданном базисе.

а) Общая характеристика микросхем серии ТТЛ:

Серия представляет собой комплект микросхем построенной на транзисторно-транзисторной логике. Назначение: построение узлов ЭВМ и устройств дискретной информатики высоким быстродействием и малой потребляемой мощностью.

В настоящее время выпускается несколько серий микросхем серии ТТЛ. Это стандартные серии 133, К155; маломощные микросхемы серий 134, КР134; микросхемы с диодами Шотки серий 530, КР531; усовершенствованные маломощные микросхемы с диодами Шотки серий 1533, КР1533; усовершенствованные микросхемы с высоким быстродействием и малым потреблением мощности серий 1531, КР1531.

Схемотехнически почти все логические элементы, входящие в состав указанных серий, могут быть образованы комбинированием двух базовых схем: элементами И-НЕ и элементом ИЛИ. Элементы И-НЕ и элемент ИЛИ образуют логический элемент И-ИЛИ-НЕ.

Одним из преимуществ серии микросхем ТТЛ является наличие в их составе таких схем как JK-триггер, D-триггеры, дешифраторы, регистры сдвига, счётчики, сумматоры и элементы памяти (ОЗУ и ПЗУ) со схемами управления.

Наличие схем, представляющих собой готовые узлы ЭВМ на несколько двоичных разрядов, позволяет значительно уменьшить число корпусов цифровых микросхем и получить существенный выигрыш в объёме аппаратуры.

б) общая характеристика микросхем серии КР1533:

Серия ИС 1533 является функционально полной и содержит в своём составе логические элементы, счётчики, регистры, АЛУ, схемы сравнения, Формирователи и т.д.

Микросхемы выполнены по биполярной технологии на основе транзисторно-транзисторной логики с диодами Шотки (ТТЛШ). Микросхемы полностью совместимы с ИС К133; К155; КМ155 по логическим уровням, напряжению питания, помехоустойчивости и при одинаковом быстродействии потребляют в пять раз меньшую мощность от источника питания на один базовый ЛЭ.

Параметры серии КР1533:

Напряжение питания – 5В + 5%

Напряжение логической единицы – 2,5 В

Напряжение логического нуля – 0,4 В

Мощность – 1 мВт/ЛЭ

Быстродействие (время задержки распространения сигнала) – 14 нс

1. Микросхема КР 1533 ЛН 1 – инвертор. Данная микросхема включает в себя 6 элементов «НЕ». Микросхема преобразует сигнал в обратный ему же, то есть 0→1 или 1→0. Форма записи функции: f(x) = ![]() .

.

Табл.4 Таблица истинности:

|

|

|

|

|

|

|

|

|

|

|

|

| х | f |

| 0 | 1 |

| 1 | 0 |

|

Микросхема КР 1353 ЛА 3 – элемент Пирса. Данная микросхема включает в себя 4 логических элемента «2И-НЕ». Каждый из четырех логических элементов выполняет конъюнкцию над двумя сигналами, затем полученный результат инвертирует. Форма записи функции:

f(x1

,x2

)= ![]()

Табл.5.Таблица истинности.

:

| x2 | x1 | f |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

![]()

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Микросхема КР 1533 ЛА 2. Данная микросхема включает в себя один элемент «8И-НЕ». Логический элемент выполняет конъюнкцию над 8 сигналами, затем полученный результат инвертирует. Форма записи функции:f (x1

,x2

,х3

,х4

,x5

,x6

,х7

,х8

) = ![]()

|

Микросхема КР 1533 ЛА 1. Данная микросхема включает в себя 2 логических элемента «4И-НЕ». Каждый из двух логических элементов выполняет конъюнкцию над четырьмя сигналами, затем полученный результат инвертирует. Форма записи функции: f(x1

,x2

,х3

,х4

)= ![]()

| х4 | х3 | x2 | x1 | f |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Табл.6 Таблица истинности КР 1533 ЛА 1

Микросхема КР 1533 ЛА 4. Данная микросхема включает в себя 3 логических элемента «3 И–НЕ». Каждый из трёх логических элементов выполняют конъюнкцию над тремя, затем полученный результат инвертирует.

Форма записи функции: f(x1

,x2

,х3

,х4

)= ![]()

2.2.8.Описание работы

Чтобы описать работу устройства для примера мы возьмём из графа одну дугу

|

||

|

||

При подаче на триггеры импульса синхронизации, на вход дешифратора с выходов триггеров подаётся сигнал 1000. На восьмом выходе дешифратора образуется логический ноль, а на остальных выходах единица. На комбинационный узел также будет подаваться сигнал Х1. После прохождения через логические элементы на входах триггеров образуется сигнал 1001, что означает изменение состояния триггеров в a9, также образуются сигналы У2 У6.

Заключение

В процессе написания курсовой работы нами были закреплены полученные теоретические знания и практические умения. А так же углубленны теоретические знания по данной теме.

Мы научились использовать справочную, учебную и другую литературу. Получили представление о цифровых автоматах и научились выбирать подходящие для синтеза микросхемы. Разрозненные знания о вычислительной технике начали собираться в систему так, как данная курсовая работа является комплексной и охватывает весь курс вычислительной техники.

4. Список использованной литературы

1. Цифровые устройства и микропроцессорные системы, Б.А.Калабеков, И.А.Мамзелев, 1997, М. «Радио и связь».

2. Аналоговые и цифровые интегральные микросхемы, справочное

пособие под редакцией С.В.Якубовского, 1984, М. «Радио и связь».

3. Интегральные микросхемы, Б.В. Тарабрина 1983, М. «Радио и связь».

Дата:

Подпись: