| Скачать .docx |

Курсовая работа: Расчет геометрических размеров резисторов и разработка топологии интегральных микросхем

Калужский техникум электронных приборов

ЗАДАНИЕ

на курсовое проектирование по дисциплине «ИМС и основы их проектирования»

Тема задания

«Расчет геометрических размеров резисторов и разработка топологии ИМС»

Содержание

Введение

1. Исходные данные для проектирования

1.1 Схемотехнические параметры

1.2 Конструктивно-технологические данные и ограничения

2. Обзор литературы по теме курсового проекта

2.1 Классификация интегральных схем и их сравнение

2.2 Краткая характеристика полупроводниковых интегральных микросхем

3. Расчёт полупроводниковых резисторов

3.1 Общие сведения об изготовлении полупроводниковых резисторов

3.2 Порядок расчёта полупроводниковых резисторов

3.3 Расчёт полупроводниковых резисторов

4. Проектирование топологии ИМС

5. Выводы о проделанной работе

Список использованной литературы

Введение

Микроэлектроника — это направление электроники, охватывающее проблем исследования, конструирования, изготовления и применения электронных устройств с высокой степенью интеграции.

Микроэлектроника развивается по определенным закономерностям, имеющим ярко выраженное диалектическое содержание: переход количества в новое качество (от простого элемента к сложным системам); противоречия между основными технико-экономическими показателями (степенью интеграции и быстродействием, качеством и стоимостью, энергопотреблением и надежностью); взаимная зависимость выходных параметров изделий и технологической базы производства. Данные закономерности формируются в силу существующих физических процессов и в результате прямых и обратных связей между исследователями, разработчиками и технологами.

Микроэлектроника подразделяется на функциональную и интегральную. Современная микроэлектроника в значительной степени является интегральной, в основу которой положен схемотехнический принцип, заключающийся в сохранении традиционных методов реализации узлов и блоков аппаратуры на базе дискретных радиокомпонентов (резисторов, конденсаторов, диодов, транзисторов и т. д.) и разработке электрических схем на основе теории цепей. В микросхемах элементы объединяются (интегрируются) в объеме полупроводника или на поверхности диэлектрической подложки.

Факторами, определяющими развитие интегральной микроэлектроники, являются наличие сверхчистых материалов, использование совершенной технологии, применение высокопроизводительного специального оборудования. Современное производство микросхем характеризуется внедрением новых групповых технологических процессов (ионно-плазменных и плазмохимических, молекулярно-лучевой эпитаксии, электронной, рентгеновской и ионной литографии, ионной имплантации и др.) В перспективе к 2000 г. ожидается создание технологии, представляющей комплексную технологию промышленной обработки изделий с точностью 1 нм. При этом имеется в виду объединение в единую взаимосогласованную систему многочисленных обрабатывающих инструментов, контрольно-измерительных и управляющих устройств. Использование прецизионной технологии требует широкого ассортимента специального технологического оборудования.

Технический уровень сложности микросхем характеризуется степенью интеграции. Темпы развития микросхем впечатляющие. В 1959 г. кристалл содержал несколько элементов, к 1970 г. число элементов возросло до 103 , к 1976 г.— до 104 , к 1985 г. уже более 105 , к 1992 г. ожидается 108 —109 элементов. При этом стоимость одного кристалла повышалась весьма умеренно, так что стоимость одного элемента резко уменьшалась. Главным направлением исследований в микроэлектронике продолжает оставаться поиск возможности уменьшения размеров микросхем, а значит, повышение степени интеграции. Возможны три пути: уменьшение топологических размеров элементов микросхем; увеличение площади кристалла; переход к расположению элементов микросхем в нескольких слоях, так называемые трехмерные микросхемы. Каждый из этих путей характеризуется весьма существенными трудностями и не может рассматриваться как единственное верное решение проблемы повышения степени интеграции.

Наибольшие сложности в этом отношении представляет переход к трехмерной микроэлектронике. Это связано с очень серьезными технологическими трудностями, хотя поиски в этом направлении ведутся весьма интенсивно.

Наиболее простым способом на первый взгляд представляется увеличение размера кристалла. Однако практика промышленного производства микросхем показывает, что с увеличением площади кристалла резко возрастает вероятность появления дефектов. К числу таких дефектов могут относиться и внутренние дефекты исходного полупроводникового материала, и дефекты, вносимые в ходе технологических операций изготовления микросхем.

Чем большее число последовательных прецизионных технологических операций включает технологический процесс, тем более вероятным становится поражение кристалла тем или иным дефектом. В результате процент выхода годных микросхем с увеличением площади кристалла падает по экспоненциальному закону. Поэтому площадь кристалла должна быть достаточно малой, чтобы вероятность возникновения дефектов была минимальна. В результате усовершенствования производства кремниевых подложек и технологии изготовления микросхем плотность дефектов постоянно уменьшается, что позволяет увеличивать размеры кристаллов. При существующем в настоящее время технологическом оборудовании разумные уровни технологических потерь удается обеспечить при площади кристалла 50—60 мм. Уменьшение топологических размеров элементов микросхем связано с совершенствованием технологии.

Параллельно с интегральной микроэлектроникой начинает развиваться функциональная микроэлектроника, основанная на использовании физических принципов интеграции и динамических неоднородностей, обеспечивающих несхемотехнические принципы работы приборов и устройств.

Поскольку ИС, подобно электронной лампе или транзистору, представляет собой конструктивно единое целое, выполняет определенную функцию и должна удовлетворять определенным требованиям при испытаниях, поставках и эксплуатации, она относится к разряду электронных приборов. Однако по сравнению с диодом, транзистором и т. п. ИС является качественно новым типом прибора.

1. Исходные данные для проектирования

1.1 Схемотехнические параметры

На рисунке 1 изображена электрическая схема варианта № 5

Рис.1 Электрическая схема варианта № 1

1.2 Конструктивно-технологические данные и ограничения

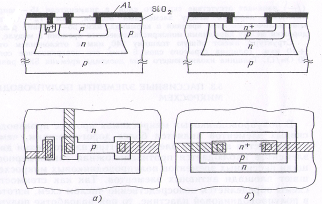

Конструктивные и технологические ограничения, которые учитываются при разработке топологии интегральной микросхемы на биполярных транзисторах, изображены на рисунке 2. Расшифровка рисунка приведена в таблице 1.

Рис. 2 Конструктивно-технологические ограничения при разработке топологии интегральной микросхемы на биполярных транзисторах.

Таблица 1 Конструктивно-технологические данные и ограничения

| Минимально допустимые размеры | мкм | ||

| Ширина линии скрайбирования слоя | 60 | ||

| Расстояние от центра скрайбирующей полосы до края слоя металлизации или до края диффузионной области | 50-100 |

||

| Ширина проводника d3 при длине < 50 мкм | 4 | ||

| Расстояние между проводниками d4 при длине < 50 мкм | 3 | ||

| Перекрытие металлизации контактных окон в окисле к элементам ИМС d20 | 2 | ||

| Расстояние от края контактного окна р+ разделительных областей для подачи смещения до края области разделения <d21 | 6 |

||

| Расстояние от края контактного окна к изолированным областям n-типа для подачи смещения до края области разделения d22 | 6 |

||

| Размер контактных площадок для термокомпрессионной приварки проводников dl | 100 | ||

| Расстояние между контактными площадками d2 | 70 | ||

| Ширина проводника d3 при длине > 50 мкм | 6 | ||

| Расстояние между проводниками d 4 при длине > 50 мкм | 4 | ||

| Размер контактных площадок текстовых элементов рабочей схемы | 50x50 | ||

| Размеры контактного окна к базе dl5 | 4x6 | ||

| Размеры контактного окна к эмиттеру dl6 | 4х4;3х5 | ||

| Размеры окна вскрытия в окисле | 2,5x2,5 | ||

| Размеры окна в пассивирующем окисле d 23 | 100x100 | ||

| Ширина области разделительной диффузии d 5 | 4 | ||

| Расстояние от базы до области подлегирования разделительной диффузии d 6 | 10 | ||

| Расстояние между краем области подлегирования коллекторного контакта и краем разделительной области d7 | 10 |

||

| Расстояние между краем разделительной области и краем скрытого п+ -, слоя d 8 | 7 | ||

| Расстояние между краем контактного окна в окисле и к базе и краем базы d 1 | 3 | ||

| Расстояние между эмиттерной и базовой областями d 11 | 3 | ||

| Расстояние между краем контактного окна в окисле к эмиттеру и краям эмиттера dl | 3 | ||

| Расстояние между контактными окнами к базе и эмиттеру | 4 | ||

| Расстояние между базовыми областями, сформированными в одном коллекторе | 9 | ||

| Расстояние между контактным окном к коллектору и областью разделительной диффузии dl4 | 6 |

||

| Ширина области подлегирования п+ - слоя в коллекторе dl7 | 8 | ||

| Ширина к контактному окну к коллектору dl8 | 4 | ||

| Ширина резистора dl3 | 5 | ||

| Ширина диффузионной перемычки | 3 | ||

| Расстояние от края окна в пассивации до края контактной площадки d 20 | 6 | ||

| Расстояние между соседними резисторами d25 | 7 | ||

| Расстояние между диффузионными и ионно-легированными резисторами | 4 | ||

| Расстояние между контактной площадкой и проводящей дорожкой d 26 | 20 | ||

| Ширина скрытого п+ - слоя | 4 | ||

| Расстояние между контактными площадками текстовых элементов | 40 | ||

| Перекрытие металлизации контактных окон в окисле к элементам ИМС d2o | 2 | ||

| Расстояние от края контактного окна р+ к разделительным областям для подачи смещения до края области разделения d 21 | 6 |

||

| Расстояние от края контактного окна к изолированным областям n-типа для подачи смещения до края области разделения d 22 | 6 |

||

2. Обзор литературы

2.1 Классификация ИМС и их сравнение

В процессе развития микроэлектроники (МЭ), начиная с 1960 г., номенклатура ИС непрерывно изменялась. При этом отдельные типы ИС нередко рассматривались как альтернативные, т. е. исключающие все другие. В настоящее время каждый из основных типов ИС занял свое, относительное стабильное место в микроэлектронике. Выше, иллюстрируя общую идею интеграции, мы имели в виду главный тип ИС — полупроводниковые.

По способу изготовления и получаемой при этом структуре различают два принципиально разных типа интегральных схем: полупроводниковые и пленочные.

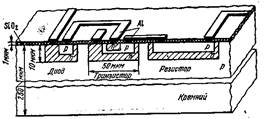

Рис. 3. Структура элементов полупроводниковой ИС

Полупроводниковая ИС — это микросхема, элементы которой выполнены в приповерхностном слое полупроводниковой подложки. Эти ИС составляют основу современной микроэлектроники (рис. 3).

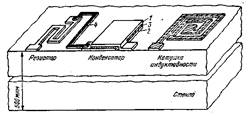

Пленочная ИС — это микросхема, элементы которой выполнены в виде разного рода пленок, нанесенных на поверхность диэлектрической подложки (рис. 4). В зависимости от способа нанесения пленок и связанной с этим их толщиной различают тонкопленочные ИС (толщина пленок до 1—2 мкм) и толстопленочные ИС (толщина пленок от 10—20 мкм и выше).

Рис. 4 . Структура элементов пленочной ИС:

1 — верхняя обкладка; 2 — нижняя обкладка; 3 — диэлектрик; 4 — соединительная металлическая полоска

Поскольку до сих пор никакая комбинация напыленных пленок не позволяет получить активные элементы типа транзисторов, пленочные ИС содержат только пассивные элементы (резисторы, конденсаторы и т. п.). Поэтому функции, выполняемые чисто пленочными ИС, крайне ограничены. Чтобы преодолеть эти ограничения, пленочную ИС дополняют активными дискретными компонентами, располагая их на той же подложке и соединяя с пленочными элементами (рис. 5). Тогда получается смешанная — пленочно-дискретная ИС, которую называют гибридной. Гибридная ИС (или ГИС) — это микросхема, которая представляет собой комбинацию пленочных пассивных элементов и дискретных активных компонентов, расположенных на общей диэлектрической подложке. Дискретные компоненты, входящие в состав гибридной ИС, называют навесными, подчеркивая этим их обособленность от основного технологического цикла получения пленочной части схемы. Помимо диодов и транзисторов, навесными компонентами могут быть и полупроводниковые ИС, т. е. компоненты повышенной функциональной сложности.

Ещё один тип «смешанных» ИС, в которых сочетаются полупроводниковые и плёночные интегральные элементы, называют совмещёнными.

Совмещённая ИС – это микросхема, Укоторой активные элементы выполнены в поверхностном слое полупроводникового кристалла (как у полупроводниковой ИС), а пассивные нанесены в виде пленок на предварительно изолированную поверхность того же кристалла (как у пленочной ИС).

Рис. 5.Структура гибридной ИС:

1 – резистор; 2 – полоска металлизация; 3 – навесной бескорпусный транзистор.

Совмещенные ИС выгодны тогда, когда необходимы высокие номиналы и высокая стабильность сопротивлений и емкостей; эти требования легче обеспечить с помощью пленочных элементов, чем с помощью полупроводниковых.

Во всех типах ИС межсоединения элементов осуществляются с помощью тонких металлических полосок, напыленных или нанесенных на поверхность подложки и в нужных местах контактирующих с соединяемыми элементами. Процесс нанесения этих соединительных полосок называют металлизацией, а сам «рисунок» межсоединений — металлической разводкой.

Как уже отмечалось, пленочные, а значит, и гибридные ИС в зависимости от технологии изготовления делятся на толсто- и тонкопленочные.

Толстопленочные ГИС (обозначим их ТсГИС) изготавливаются весьма просто, на первый взгляд — примитивно. На диэлектрическую пластинку-подложку довольно большой площади (несколько квадратных сантиметров) наносят пасты разного состава. Характерная особенность этого метода состоит в том, что пленка сразу приобретает заданную толщину. Проводящие пасты обеспечивают межсоединения элементов, обкладки конденсаторов и выводы к штырькам корпуса; резистивные — получение резисторов; диэлектрические — изоляцию между обкладками конденсаторов и общую защиту поверхности готовой ГИС. Каждый слой должен иметь свою конфигурацию, свой рисунок.

Рис. 6. Накладная маска — трафарет для Рис. 7. Послойное

локального нанесения пасты наращивание тонкой пленки

Поэтому при изготовлении каждого слоя пасту наносят через свою маску — трафарет — с отверстиями (окнами) в тех местах, куда должна попасть паста данного слоя (рис 6). После того как пленочная часть ТсГИС закончена, на заранее отведенные «пустые» места или на защитный диэлектрический слой приклеивают навесные компоненты и соединяют их выводы с контактными площадками, предусмотренными в проводящих слоях. Главные особенности ТсГИС:

— «механический» способ нанесения паст не позволяет делать толщину пленок менее 10—20 мкм (типичные значения 50—100 мкм), отсюда — названия толстопленочная технология и толстопленочные ГИС;

— простота технологии обеспечивает ее доступность и низкую стоимость изделий;

— «механический» способ нанесения пленок не может обеспечить достаточно малых допусков на номиналы резисторов и конденсаторов, т. е. прецизионность элементов.

Тонкопленочные ГИС (обозначим их ТкГИС) изготавливаются по более сложной технологии, чем ТсГИС, причем используется специфическое оборудование, обычно весьма дорогое. Поэтому стоимость ТкГИС выше, чем ТсГИС.

Классическая тонкопленочная технология характерна тем, что пленки осаждаются на подложку из газовой фазы. При этом пленки приобретают свою конечную толщину не сразу (как после нанесения пасты в ТсГИС), а постепенно — один мономолекулярный слой за другим (рис. 7). Вырастив очередную пленку, меняют химический состав газа и тем самым электрофизические свойства следующей пленки. Таким образом поочередно получают проводящие, резистивные и диэлектрические слои. Конфигурация (рисунок) каждого слоя определяется либо трафаретом, наложенным на подложку (как в случае ТсГИС), либо маской, выращенной на поверхности подобно окисной маске в полупроводниковых ИС.

Для того чтобы атомы или молекулы пара беспрепятственно проходили от источника до подложки, необходимо создать достаточное разрежение атмосферы, т. е. проводить осаждение (нанесение) пленок в замкнутом пространстве (под колпаком), в котором создан вакуум той или иной степени.

Навесные элементы в ТкГИС, как и в ТсГИС, приклеивают на поверхность готовой пленочной части схемы и соединяют с соответствующими контактными площадками элементов.

Особенности ТкГИС, вытекающие из приведенного описания, следующие:

—поскольку пленки растут со сравнительно небольшой скоростью, получение пленок толщиной более 1 мкм требует много времени; кроме того, напыленные пленки толщиной более 1—2 мкм легко отслаиваются от подложки; поэтому характерная толщина пленок в ТкГИС составляет не более 0,5—1 мкм, отсюда — названия тонкопленочная технология и тонкопленочн ы е ГИС;

—поскольку пленки растут с небольшой скоростью, можно сравнительно легко регулировать их толщину, обеспечивая малые допуски на номиналы сопротивлений и емкостей, т. е. прецизионность элементов.

Степень интеграции ГИС не может оцениваться так же, как в случае полупроводниковых ИС, поскольку отсутствует «начало отсчета» в виде пленочного активного компонента. Тем не менее существует термин большая ГИС (или БГИС), который означает, что в состав ГИС в качестве навесных компонентов входят не отдельные транзисторы, а целые полупроводниковые ИС, так что функция, выполняемая БГИС, может быть значительно более сложной, чем функция отдельной ИС и даже БИС.

Микросхемы классифицируют по степени интеграции, частотному диапазону, функциональному назначению, конструктивно-технологическому исполнению.

По функциональному признаку микросхемы подразделяются на цифровые, и аналоговые. Цифровые микросхемы предназначены для преобразования и обработки сигналов, изменяющихся по закону дискретной функции, цифровые — для работы в логических устройствах, в частности в ЭВМ. Использование логических схем позволяет различные логические зависимости и решения представить в виде электрических сигналов. В современных цифровых вычислительных машинах информация выражается в помощью двух состояний уровней напряжения и тока: низкого и высокого, что соответствует в двоичной системе символам 0 и 1.

Аналоговые микросхемы предназначены для преобразования и обработки сигналов, изменяющихся по закону непрерывной функции. Частным случаем аналоговых микросхем являются микросхемы с линейной характеристикой, так называемые линейные микросхемы.

Степень интеграции микросхем — показатель степени сложности микросхемы К характеризуется числом содержащихся в ней элементов и компонентов: К=lgN, где К — коэффициент, округляемый до ближайшего большего целого числа; N — число элементов и компонентов, входящих в микросхему. По степени интеграции микросхемы подразделяют на:

малые интегральные схемы (МИС) – схемы (1 – 2)-й степени интеграции, содержащие от нескольких до 100 элементов и компонентов, в состав которых входит один или несколько видов функциональных аналоговых или логических элементов, например логических элементов И, ИЛИ, НЕ, триггеров, усилителей, фильтров и т. п.;

средние интегральные схемы (СИС)— схемы (2—3)-й степени интеграции, содержащие от нескольких десятков до 1000 элементов и компонентов, в состав которых входит один или несколько одинаковых функциональных узлов электронных устройств (регистр, счетчик, дешифратор, постоянное запоминающее устройство);

большие интегральные схемы (БИС)— схемы (3—4)-й степени интеграции, содержащие от нескольких сотен до 10 000 элементов, в состав которых входит одно или несколько функциональных устройств (например, арифметико-логическое устройство, оперативное запоминающее устройство, перепрограммируемое постоянное запоминающее устройство и др.);

сверхбольшие интегральные схемы (СБИС) — схемы (5—7)-й степени интеграции, представляющие собой законченное изделие, способное выполнять функции аппаратуры (например, ЭВМ).

Наибольшей степенью интеграции обладают полупроводниковые микросхемы, затем тонкопленочные и, наконец, толстопленочные. По степени интеграции полупроводниковые микросхемы на биполярных транзисторах уступают интегральным микросхемам на МДП-транзисторах.

2.2 Краткая характеристика полупроводниковых интегральных микросхем

Полупроводниковые ИС. В настоящее время различают два класса полупроводниковых ИС: биполярные ИС и МДП МС. Сочетание биполярных и МДП-транзисторов на одном кристалле является особым случаем.

Технология полупроводниковых ИС обоих классов основана на легировании полупроводниковой (кремниевой) пластины поочередно донорными и акцепторными примесями, в результате чего под поверхностью образуются тонкие слон с разным типом проводимости и р—n- переходы на границах слоев. Отдельные слои используются в качестве резисторов, а р —n-переходы — в диодных и транзисторных структурах.

Легирование пластины приходится осуществлять л о к а л ь н о, т. е. на отдельных участках, разделенных достаточно большими расстояниями1 *. Локальное легирование осуществляется с помощью специальных масок с отверстиями, через которые атомы примеси проникают в пластину на нужных участках, При изготовлении полупроводниковых ИС роль маски обычно играет пленка двуокиси кремния SiO2 , покрывающая поверхность кремниевой пластины. В.этой пленке специальными методами гравируется необходимая совокупность отверстий или, как говорят, необходимый рисунок (рис. 8). Отверстия в масках, в частности и окисной пленке, называют окнами.

Теперь кратко охарактеризуем составные части (элементы) двух основных классов полупроводниковых ИС.

Рис 8, Окисная маска с окнами дли локального легирования

Основным элементом биполярных ИС является п—р—п- транзистор: на его изготовление ориентируется весь технологический цикл. Все другие элементы должны изготавливаться, по возможности, одновременно с этим транзистором, без дополнительных технологических операннй. Так, резисторы изготавливаются одновременно с базовым слоем п—р —транзистора и поэтому имеют ту же глубину, что и базовый слой. В качестве конденсаторов используются обратносмещенные р —n-переходы, в которых слои соответствуют коллекторному слою п—р —n-транзнстора, и слою р— базовому.

Основным элементом МДП ИС является МДП-транзистор с индуцированным каналом. Роль резисторов выполняют транзисторы, включенные по схеме двухполюсника, а роль конденсаторов — МДП-структуры, у которых слой диэлектрика получается одновременно с подзатворным слоем транзистора, а полупроводниковая обкладка — одновременно со слоями истока и стока.

Элементы биполярной ИС необходимо тем или иным способом изолировать друг от друга с тем, чтобы они не взаимодействовали через кристалл. Методы изоляции элементов рассматриваются Элементы МДП ИС не нуждаются в специальной изоляции друг от друга, так как взаимодействие между смежными МДП-транзисторами не имеет места и их можно располагать на минимальном расстоянии друг от друга. В этом одно из главных преимуществ МДП ИС но сравнению с биполярным.

Характерная особенность полупроводниковых ИС состоит в том, что среди их элементов отсутствуют катушки индуктивности и тем более трансформаторы. Эго объясняется тем. Чти до сих пор не удалось использовать в твердом теле какое-либо физические явление, эквивалентное электромагнитной индукции. Поэтому при разработке ИС стараются реализовать необходимую функцию без использования индуктивности, что в большинстве случаев удается. Если же катушка индуктивности или трансформатор принципиально необходимы, их приходится использовать в виде навесных компонентов.

Размеры кристаллов у современных полупроводниковых ИС лежат в пределах от 1,5 X 1,5 мм до б X 6 мм. Чем больше площадь кристалла, тем боле*' сложную, более многоэлементную ИС можно на нем разместить. При одной н той же площади кристалла можно увеличить количество элементов, уменьшая их размеры и расстояния между ними.

Функциональную сложность ИС принято характеризовать степенью интеграции, т. е, количеством элементов (чаще всего транзисторов) ни. кристалле. В 1978—1979 гг. максимальная степень интеграции составляла (5—6) • 104 элементов на кристалле. Повышение степени интеграции (а вместе с нею и сложности функций, выполняемых ИС) — одна из главных тенденций в микроэлектронике.

Кроме степени интеграции, используют еще такой показатель, как плотность упаковки — количество элементов (чаще всего транзисторов) на единицу площади кристалла, Этот показатель, который характеризует главным образом уровень технологии, в настоящее время составляет до 500—1000 элементов/мм.

3. Расчёт полупроводниковых резисторов

3.1 Общие сведения об изготовлении полупроводниковых резисторов

Интегральные резисторы. В полупроводниковых микросхемах функцию резистора выполняет объем полупроводника, имеющий определенные размеры и конфигурацию, или транзисторная схема (аналог резистора). Интегральные резисторы могут быть разделены на следующие типы в зависимости от структуры: диффузионные (на основе эмиттерной или базовой области); эпитаксийльные (на основе коллекторной области); пинч-резкеторы, а также резисторы, изготовляемые методом ионного легирования. Все интегральные резисторы, кроме последнего из перечисленных типов, изготовляются одновременно с активными элементами микросхем без введения дополнительных этапов обработки. Они создаются на основе коллекторной, базовой или эмиттеркой областей транзистора.

Диффузионные резисторы. Диффузионные резисторы изготавливают одновременно с диффузией примесей, в процессе которой создаются базовые или эмнттерные области п-р-п- транзнстора. Сопротивление диффузионного резистора представляет собой объемное сопротивление участка диффузионного слоя, ограниченного р-п -переходом. Оно определяется геометрическими размерами резистивной области и распределением примеси по глубине диффузионного слон, которое, в свою очередь, характеризуется удельным поверхностным сопротивлением R*- Значение Rs является конструктивным параметром резистора, зависящим от технологических факторов (режима диффузии). Типичные значения сопротивлении диффузионных резисторов, которые можно получить при данном значении R лежит в пределах 4/?6 </?< <1()4 ^. Нижний предел ограничивается сопротивлением контактны* областей, которое должно быть значительно меньше сопротивления основной области резистора. В качестве контактирующего металла используется алюминий. Верхний предел ограничивается допустимой площадью, отводимой под резистор. Чаще всего резисторы выполняются на основе базовой области 100—300 Ом. В этом случае и качестве резистора используется область n-типа (рис 9, а). К слою n-типа прикладывается положительный потенциал, смещающий р-n-переход в обратном направлении. Обратносмещенный переход, обладающий большим сопротивлением, определяет границы диффузионной области и обеспечивает развязку по постоянному току между резистором и подложкой. На основе базового диффузионного слояможно получать резисторы с номиналами сопротивлений от 100 Ом до 60 кОм.

Рис. 9. Структуры диффузионных резисторов, a — резистор на основе базовой области; 6 — резистор на основе эмиттерцой области

Для резисторов с номиналами от 3 до 100 Ом целесообразно использовать эмиттерный диффузионный слой (рис, 10), поскольку значение R% эмиттерного слоя невелико R — 10 Ом.

Пинч-резисторы. При необходимости создания высокоомных резисторов с сопротивлением более 60 кОм используют пинч-резнеторы (канальные, сжатые или закрытые). Пинч-резнсторы могут создаваться на основе базового слоя или коллекторного. представлена конструкция пкнч-резистора на основе базового слоя, ограниченного по тол шиле эмиттерным слоем n+ -типа. Резистор представляет собой тонкий канал р-типа. используется донном, слаболегированная часть базовой области с R,=:2— 5 кОм/П. изолированная со всех сторон обратносмещенным р-n-переходом, так как эмиттерный слой n-тмпа За пределами резистора соединяется с зпитаксиальным n-слоем изолированной области. Максимальное сопротивление таких резисторов составляет 200—300 кОм при простейшей полосковой конструкции. На рис. 5.6, б приведена конструкция пинч-резистора на основе коллекторной области, поперечное сечение которого уменьшено на глубину базового слоя (L, = 4—8 кОм). Для получения качественного омического контакта используют диффузионные n+ -области, которые создают на стадии эмиттернон диффузии, пинч-резисторы имеют большой разброс номиналов (до 50%) из-за трудностей получения точных значений толщины донной части, сопротивление их сильно зависит от температуры вследствие малой степени легирования областей, на основе которых они выполняются.

Рис10. Конструкция пинч-резисторов: а — на основе базового слоя; б — на основе коллекторной области

Эпитаксиальные резисторы. Из трех областей транзистора коллекторная имеет наименьшую концентрацию легирующей примеси и максимальное R2 (500—5000 Ом). Поскольку эпитаксиальный слой легирован однородно, проводимость эпитаксиального резистора постоянна по всему сечению в отличие от диффузионных резисторов. У эпитаксиального резистора поперечное сечение по форме существенно отличается от сечений диффузионных резисторов, так как эпитаксиальный резистор формируется разделительной диффузией. Поскольку эта диффузия самая продолжительная и точная регулировка размеров диффузионных областей, особенно величины боковой диффузии, затруднена, разброс номиналов сопротивления эпитаксиальных резисторов значителен. Эти резисторы имеют большой ТКС, поскольку коллекторная область легирована слабо. Таким образом, если в микросхеме можно использовать некритичные резисторы с высокими номинальными значениями, то их целесообразно формировать на основе эпитаксиального слоя, что позволит сэкономить площадь кристалла.

Ионно-легированные резисторы. Высокоомные резисторы, занимающие малую площадь на кристалле, можно получить, используя метод ионной имплантации. Поверхностное сопротивление резисторов, изготовленных методом ионного легирования, при соответствующем выборе дозы легирования и режиме термообработки может составлять от 500 Ом до 20 кОм. Абсолютное значение удельного поверхностного сопротивления может выдерживаться с точностью ±6%. Температурные коэффициенты сопротивления резисторов, полученных методом ионного легирования, обычно меньше ТКС диффузионных резисторов. Структура ионно-легированных резисторов такая же, как и диффузионных резисторов, но глубина ионно-легированных слоев составляет 0,1—0,3 мкм (рис. 11). Создание диффузионных р- или n-областей необходимо для получения качественных омических контактов. Низкий ТКС, высокое удельное сопротивление и хорошая совместимость с другими элементами позволяют, использовать ионно-легированные резисторы для изготовления прецизионных аттенюаторов, а также в микромощных микросхемах. Типичные характеристики интегральных резисторов приведены

Рис. 11. Конструкция ионно-легированных резисторов:

а — с р-ионно-легироваиным слоем; б— с n-ионно-легированным слоем

3.2 Порядок расчета полупроводниковых резисторов

Как уже отмечалось, один из способов реализации резистивных элементов в полупроводниковых микросхемах заключается в использовании диффузионных слоев, полученных при формировании базовых или эмиттерных областей транзисторов. Кроме того, применяются эпитаксиальные и ионно-легированные резисторы.

Исходными данными для определения геометрических размеров интегральных полупроводниковых резисторов являются:

а) заданные в принципиальной электрической схеме номинальное значение R и допуск на него yR =R/R;

б) поверхностное сопротивление легированного слоя Rs , на основе которого формируется резистор;

в) средняя мощность, рассеиваемая резистором Р, и максимально допустимая удельная мощность Р;

г) основные технологические и конструктивные ограничения. Сопротивление резистора R = RS l/b, где l и Ь — длина и ширина резистора.

Проектирование резистора с заданным номиналом сводится к определению конфигурации резистивного слоя, так как при известном поверхностном сопротивлении слоя Rs номинальное значения сопротивления резистора зависит от отношения его длины к ширине (коэффициента формы K = l/b). Контактные площадки, расположенные на концах полупроводникового резистора, вносят дополнительные сопротивления. Поэтому в расчетную формулу вводится поправочный коэффициент, зависящий от конфигурации контактных областей. На рис. 12 приведены' несколько типовых топологий полупроводниковых резисторов. Конфигурации, приведенные на рис. 12, а, б, пригодны для реализации низкоомных резисторов с номинальными значениями от нескольких ом до одного килоома. При этом оказывается, что для очень низкоомных резисторов ширина превышает его длину. Сопротивления резисторов, показанных на рис. 12, а, б, равны соответственно R=R(L\b+2K) R=R(L+L)

Для резисторов с номинальными значениями,, превышающими 400 Ом, можно использовать топологию, приведенную на рис. 12. Расчетное соотношение для определения сопротивления резистора в этом случае

R=R(L\b+2k)

Резисторам с номинальными значениями более 1 кОм целесообразно придавать форму змейки (рис. 12, г), что позволяет значительно уменьшить площадь, занимаемую резистором.

Рис. 12. Топологии диффузионных резисторов:

а. б — низкоомные до 1 кОм; в, г — свыше 400 Ом

Расчет геометрических размеров интегральных полупроводниковых резисторов начинают с определения их ширины. За ширину резистора принимают значение, которое не меньше наибольшего значения одной из следующих величин:

минимальной ширины резистора £те х, определявши разрешающей способностью технологических процессов

минимальной ширины резистора 6ТО чи, при которой точность его изготовления равна заданной;

минимальной ширины резистора ЬР определяемой исходя из максимально допустимой рассеиваемой мощности:

абсолютные погрешности ширины и длины резистивной полоски (для типовых технологических процессов мкм); Кф —коэффициент формы, определяется из соотношения относительная погрешность коэффициента формы резистора:

Здесь относительная погрешность удельного поверхностного сопротивления легированного слоя, для типовых технологических процессов температурная погрешность сопротивления. Минимальное значение ширины определяется как где максимально допустимая удельная мощность рассеяния, выбираемая в зависимости от типа корпуса микросхемы и условий ее эксплуатации в пределах,

Расчетную длину резистора определяют исходя из формул

Для составления топологического чертежа определяют вначале промежуточные значения ширины и длины резистора, учитывающие технологические отклонения размеров где погрешность, вносимая счет систематического растравления контактных окон в окисле для типовых технологических погрешность, вносимая за счет ухода базовой (эмиттерной) диффузии под окнсел в боковую сторону. Через Обозначен коэффициент, учитывающий распределенно примесей вблизи границы резистора, причем обычно. Для резисторов шириной более 10 мкм боковой диффузией можно пренебречь (а — 0). В более узких резистора боковая диффузии оказывает значительное влияние, поэтому в расчеты необходимо вводить соответствующую поправку.

Затем выбирают шаг координатной сетки и т. д., определяют топологические значения ширины и длины резистора;

где Целые положительные числа.

После этого оценивают получающуюся погрешность сопротивление, рассчитанное по

Если то ширину резистора увеличивают на величину и все вычисления повторяют.

3.3 Расчёт полупроводниковых резисторов

Все расчёты проводятся по упрощённой схеме с использованием табличных значений из справочника. Выбираем ширину базовой области для резистора:

1) Низкоомные резисторы с номиналом R ≤ 1 кОм имеют ширину базовой области В=30 мкм;

2) Высокоомные резисторы с номиналом от 1 кОм до 5 кОм(1кОм ≤R≤ 5кОм) выполняются с шириной базового слоя В=20 кОм;

3) Высокоомные резисторы с номиналом R>5 кОм выполняются с шириной базового слоя В=15 кОм

Таким образом достигаются воспроизводимость параметров резисторов в обьёие партии в следствии малого влияния боковой диффузии и погрешностей технологических операций.

Из справочных данных применяем следующие величины удельного поверхностного сопротивления ρs:

1) При 100 Ом ≤R≤ 300 Ом ρs= 120 Ом

2) При 300 Ом ≤R≤ 2,5 кОм ρs= 222 Ом

3) При 3 кОм ≤R≤ 4 кОм ρs= 320 Ом

4) При 5 кОм ≤R≤ 10 кОм ρs= 240 Ом

Составим таблицу значений (Таблица 2)

Значения для расчёта длинны резистора.

Таблица 2

| Позиция | R1 | R2 | R3 | R4 |

| Номинал | 2500 | 100 | 8000 | 2000 |

| Ширина диффузионной области в, мкм | 20 | 30 | 15 | 20 |

| Удельное поверхностное сопротивление, ρs, Ом | 222 | 120 | 240 | 222 |

Исходя из того, что коэффициент формы "n" можно представить двумя формулами:

n =![]() и n =

и n = ![]()

Прировняем правые части этих уравнений:

![]() =

= ![]() ,

,

где В- ширина резистора

L- длинна резистора

Формула для расчёта длинны резистора L:

L=![]()

Все величины входящие в формулу нам известны поэтому рассчитаем длину каждого из резисторов.

1)![]()

![]()

2)![]()

В![]()

3)![]()

![]()

4) ![]()

![]()

4. Проектирование топологии ИМС

Важнейший этап проектирований полупроводниковой микросхемы заключается в преобразовании ее электрической схемы в топологию. Сущность разработки топологии микросхем состоит в определении взаимного расположения элементов на подложке Разработка топологии не сводится к размещению элементов на подложке. Этот процесс должен осуществляться так, чтобы обеспечить оптимальное расположенеэлементов, при котором уменьшается влияние паразитных аффектов, присущих полупроводниковым микросхемам. Поэтому одной из основных задач при разработке топологии микросхемы является выбор критерия оптимальности размещения элементов. В настоящее время при разработке топологии полупроводниковых микросхем с однослойной металлизацией обязательными считаются следующие критерии: минимизация общей суммарной длины соединений; минимизация числа пересечений межэлементных соединений. Проектирование топологии микросхем носит индивидуальный характер и зависит от степени сложности принципиальной электрической схемы,*Тем не менее при разработке топологии необходимо выполнять следующие основные правила:

1 Для учета влияния диффузии примеси под маскирующий окисел, растравливания окисла, ошибок фотолитографии при составлении топологической схемы все элементы схем, кроме контактных площадок, рекомендуется размещать на расстоянии от щели под разделительную диффузию, равном удвоенной толщине эпитаксиального слои,

2 К изолирующим р-n-переходам всегда должно быть при ложе но напряжение обратного смещения, что практически осуществляется подсоединением подложки р-типа, или области разделительной диффузии р-типа, к точке схемы с наиболее отрицательным потенциалом. При этом обратное напряжение, приложенное к изолирующему р-n-переходу, не должно превышать напряжения пробоя.

3. При размещении элемента микросхем и выполнении зазоров между ними, необходимо строго выполнять ограничения, соответствующие типовому технологическому процессу.

4. Резисторы, формируемые на основе базового диффузионного слоя, можно располагать и одной изолированной области, которая подключается к самому положительному потенциалу схемы, т. е. к коллекторному источнику питания.

5. Резисторы на основе эмиттерного и коллекторного слоев следует располагать в отдельных изолированных областях.

6. Реальная форма резисторов, кроме ширины подоски, не является критичной. Резисторы могут быть прямыми, изогнутыми или иметь любую другую форму одна ко во всех случаях отношение длины резистора к его ширине должно быть согласовано с удельным сопротивлением исходного диффузионного слоя и обеспечено получением заданного номинала. Высокоомные резисторы рекомендуется выполнять в виде параллельных полосок с перемычками между ними. Номинальное значение резистора в этом случае будет выдержано более точно, чем при изогнутом резисторе.

7.Для уменьшения мест локального нагрева резисторы с большой рассеиваемой мощностью ме следует располагать вблизи активных элементов а рекомендуется выносить их на край кристалла

8. Резисторы, у которых необходимо точно выдержать отношение номиналов, должны иметь одинаковую ширину и конфигурацию и располагаться рядом друг с другом. Это правило относится И к другим элементам микросхем, для роторых требуется обеспечить согласование характеристик, т. е. их топологии должны быть одинаковы, а взаимное расположение — как можно более близким.

9. Любой диффузионный резистор может пересекаться проводящей дорожкой, гак как проведение металлизированного проводника по слою двуокиси кремния, покрывающему резистор, не оказывает существенного вредного влияния.

10. Форма и место расположения конденсаторов не являются критичными

11. Для диффузионных конденсаторов требуются отдельные изолированные области. Исключение составляют случаи, когда один из выводов конденсатора является общим с другой изолированной областью.

12. Транзисторы n-р-n-типа, работающие в режиме эмиттерного повторителя, можно размещать в одной изолированной области вместе с резисторами.

13. Все коллекторные области n-типа, имеющие различные потенциалы, должны быть изолированы.

14. Для каждого диода, формируемого на основе перехода коллектор — база, должна быть предусмотрена отдельная изолированная область. Диоды, формируемые на основе перехода эмиттер— база,, можно размещать в одной изолированной области.

15. Для улучшения развязки между коллекторными изолированными областями контакт к подложке рекомендуется выполнять в непосредственной близости от мощного транзистора.

16. Для диффузионных перемычек всегда требуются отдельные изолированные области.

17- Для уменьшения паразитной емкости между контактными площадками и подложкой под каждой из них рекомендуется создавать изолированную область. В этом случае емкость между контактной площадкой и подложкой оказывается включенной последовательно с емкостью изолирующего перехода и, следовательно, результирующая паразитная емкость уменьшается.

18. Соединения, используемый для ввода питания и заземления, следует вы полегать в виде коротких широких полосок, что обеспечивает уменьшение паразитных сопротивлении.

19, Число внешних выводов в схеме, а также порядок расположения и обозначения контактных площадок выводов микросхем на кристалле должны соответствовать выводам корпуса.

20- Коммутация элементов микросхем должна иметь минимальное количество пересечений. Если полностью избежать пересечений не удается, их можно осуществить, используя обкладки конденсаторов, формируя дополнительные контакты к коллекторным областям транзисторов, применяя диффузионные перемычки и, наконец, создавая дополнительный слой изоляции между пересекающимися проводниками. При разработке топологической схемы необходимо стремиться к получению минимально возможной длины межэлектродных соединений.

21. Когда наличие паразитных емкостей не существенно, резисторы могут быть размещены в тех же изолированных областях, что и транзисторы. При этом не имеет значения, должны ли они соединяться между собой. Расстояние между резисторами должно быть не менее 10 мкм. Коллектор транзистора и резистор должны располагаться на расстоянии не менее 12 мкм.

22. Расстояние между диффузионной базовой областью н контактом коллектора может быть увеличено, чтобы провести одну или две металлические дорожки между контактами коллектора и базы. Это можно сделать, так как коллекторный ток главным образом протекает от базы через скрытый слон к коллекторному контакту. Однако чем больше расстояние между базой и коллектором, тем больше паразитное сопротивление и паразитная емкость коллектора. Металлический проводник не может быть размещен между контактами базы и эмиттера за счет удлинения диффузионного базового слоя.

23. Наиболее важным.правилом при разработке топологии является минимизации площади. за1гимаемой микросхемой. Это позволяет увеличить число микросхем, изготовляемых на пластине с заданным диаметром, Кроме того, необходимо учесть, что вероятность случайных дефектов н полупроводниковом кристалле возрастает с увеличением площади.

5. Выводы о проделанной работе

В данном курсовом проекте разработана топология интегральной микросхемы.

Разработанная мной топология соответствует электрической принципиальной схеме, учитывая топологические ограничения, и использует исходные конструктивные данные.

Для изготовления заданной схемы была выбрана планарная технология на кремниевой пластине. Изоляция элементов схемы осуществляется с помощью обратно смещённого р-n перехода.

Топология кристалла была разработана с учётом конструктивно-технологических ограничений' и требований. Размеры диффузионных резисторов, использованных в схеме, были рассчитаны упрощённым методом.

Разработанная топология интегральной микросхемы не требует сложного оборудования и обеспечивает приемлемый результат для заданной схемы.

Список использованной литературы

1.Николаев И.М., Филинюк Н.А. Интегральные микросхемы и основы их проектирования. - М.: Радио и связь. 1992.

2.Конструирование и технология микросхем. Курсовое проектирование под ред. Коледова Л.А. - М: высшая школа. 1984

3.Степаненко И. П. Основы микроэлектроники - М.: Советское радио, 1980

4.Черчение под ред. Куликова А.С. - М: высшая школа, 1989

5.Малышева И. А. Технология производства интегральных микросхем - М: Радио и связь, 1991.