| Скачать .docx |

Реферат: Проектирование Цифрового устройства

МИНИСТЕРСТВО ВЫСШЕГО ОБРАЗОВАНИЯ УКРАИНЫ

Сумской Государственный Университет

Кафедра Автоматики и Промышленной Электроники

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА

к курсовому проекту по курсу: «Цифровая схемотехника»

по теме: «Проектирование Цифрового устройства»

ФЗ 51.6.090803.574ПЗ

Руководитель проекта Мировицкий Г. П.

Проектировал студент Симоненко А.В.

группы ПЭЗ-51

Оценка работы

Члены комиссии:

Сумы 1999

СОДЕРЖАНИЕ

ВВЕДЕНИЕ.............................................................................................................. 3

1. РАЗРАБОТКА СТРУКТУРНОЙ и ФУНКЦИОНАЛЬНОЙ СХЕМЫ УСТРОЙСТВА......................................................................................................... 5

1.1 Разработка структурной схемы устройства.......................................... 5

1.2 Разработка функциональной схемы устройства..................................... 6

2. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ УСТРОЙСТВА................... 8

2.1 Проектирование схемы детектора фронтов........................................... 8

2.2. Генератор тактовых импульсов............................................................... 9

2.3 Схема подсчета тактовых импульсов..................................................... 10

2.4 Схема преобразования параллельного кода в последовательный........... 11

2.5 Схема управления...................................................................................... 12

3. Заключение................................................................................................. 15

Список ЛИТЕРАТУРЫ..................................................................................... 16

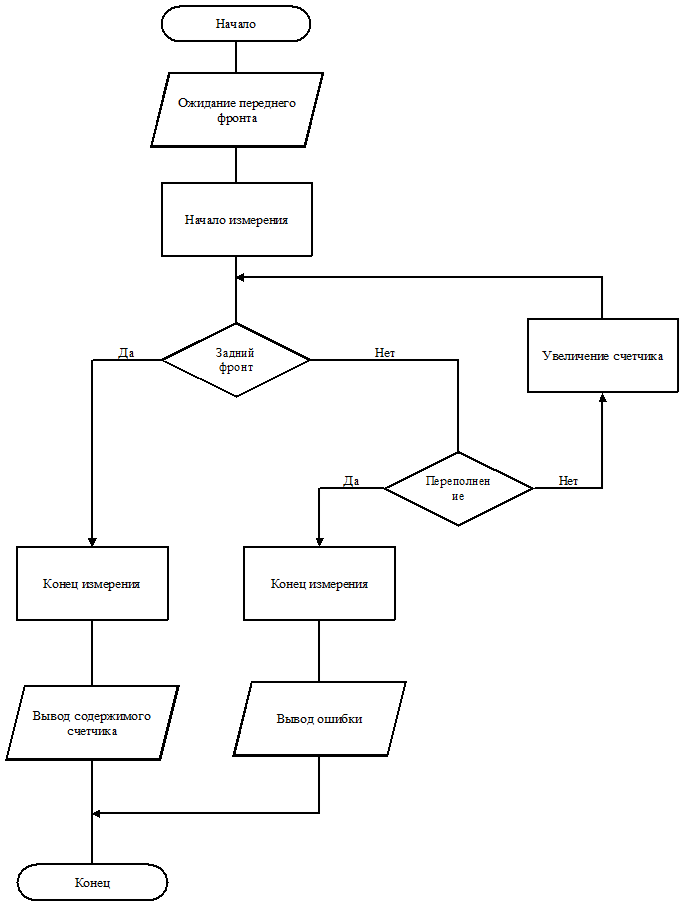

ПРИЛОЖЕНИЕ 1. Алгоритм работы устройства.............................. 17

ВВЕДЕНИЕ

Внедрение микропроцессорной, и вообще цифровой, техники в устройства управления промышленными объектами требует от специалистов самого различного профиля быстрого освоения этой области знания. В процессе разработки функциональных схем цифровых устройств отчетливо выделяются два характерных этапа. На первом этапе, который можно назвать структурным проектированием, заданный неформально алгоритм разработчик представляет в виде последовательности некоторых операторов, таких, как получение результата, счет, преобразование кода, передача информации. При этом он старается использовать ограниченный набор общепринятых операторов. При использовании этих операторов, как правило, алгоритм можно представить довольно небольшим их числом. Структура алгоритма становится обозримой, понятной, легко читаемой и однозначной. На основе полученной структуры алгоритма формулируются технические требования к схемам, реализующим отдельные операторы. По техническим требованиям в качестве функциональных узлов схемы можно применить либо готовые блоки в интегральном исполнении, либо, если таких микросхем в наличии нет, синтезировать их из более простых элементов. Подобный синтез первоначально производится при помощи алгебры логики, после чего по полученным функциям строится эквивалентная схема. Однако, как правило, синтезированные схемы хуже их аналогов в интегральном исполнении. К этому приводят следующие обстоятельства: большее время задержки, большие габариты, большее потребление энергии. Поэтому результативного проектирования цифровых устройств разработчик должен уметь: выбрать наиболее приемлемый вариант решения поставленной задачи, работать с алгеброй логики, знать основные цифровые элементы и уметь их применять, по возможности знать наиболее простые и распространенные алгоритмы решения основных задач. Знание наиболее распространенных инженерных приемов в проектировании устройств позволит в будущем сразу воспользоваться готовой схемой, не занимаясь бесполезной работой. Необходимо заметить, что реализация схемы гораздо сложнее, чем простое решение задачи в алгебре логики и наборе полученной функции из логических элементов. В действительности даже, казалось бы, самые простые элементы, необходимо включать по определенной схеме, знать назначения всех выводов. Необходимо знать, чем различаются элементы в пределах серии. Понимание внутренней логики микросхемы особенно важно именно для специалистов по автоматике и промышленной электронике, поскольку цифровые микросхемы изначально создавались для выполнения строго определенных функций в составе ЭВМ. В условиях автоматики и радиотехники они часто выполняют функции, не запланированные в свое время их разработчиками, и грамотное использование микросхем в этих случаях прямо зависит от понимания логики их работы. Хорошее знание тонкостей функционирования схем узлов становится жизненно необходимым при поиске неисправностей, когда нужно определить, имеется ли неисправность в данном узле или же на его вход поступают комбинации сигналов, на которые схема узла не рассчитана. Составление тестов, а тем более разработка само проверяемых схем также требуют очень хороших знаний принципов работы узлов.

1. РАЗРАБОТКА СТРУКТУРНОЙ и ФУНКЦИОНАЛЬНОЙ СХЕМЫ УСТРОЙСТВА

1.1 Разработка структурной схемы устройства

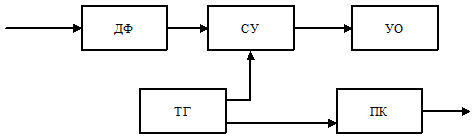

Работу устройства можно представить следующим образом. По переднему фронту импульса начинается отсчет. При поступлении заднего фронта импульса или при превышении заданного интервала времени отсчет останавливается. Если значение в счетчике превышает заданный предел, на панели отображения выводится сигнал «ошибка». В противном случае на панели отображения отображается содержимое счетчика и величина измеренного интервала передается в устройство обработки. Описанный алгоритм отображен в приложении 1.

В состав структурной схемы войдут следующие элементы:

· Детектор фронтов

· Схема подсчета тактовых импульсов

· Тактовый генератор

· Схема преобразования параллельного кода в последовательный

· Схема отображения

Структурную схему можно представить так, как отображено на рисунке 2.

|

Рисунок 1. Структурная схема

При поступлении переднего фронта измеряемого импульса детектор фронтов (ДФ) формирует управляющий сигнал на начало счета. Формируемые тактовым генератором (ТГ) импульсы поступают на схему подсчета тактовых импульсов (СУ). При поступлении заднего фронта измеряемого импульса ДФ формирует сигнал останавливающий .счет. При этом количество подсчитанных импульсов выводится на схему отображения (УО) и через схему преобразования параллельного кода в последовательный (ПК) в устройство обработки.

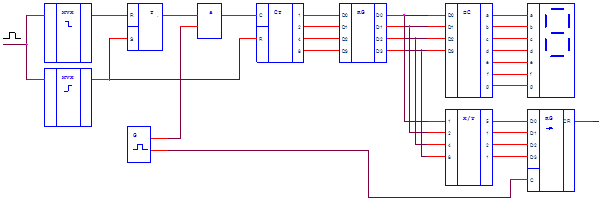

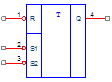

1.2 Разработка функциональной схемы устройства

Детектор фронтов состоит из двух ждущих мультивибраторов и триггера. Один ждущий мультивибратор предназначен для выделения заднего фронта импульса и сбрасывает триггер. Другой ждущий мультивибратор предназначен для выделения переднего фронта импульса и переключает триггер в единичное состояние и вырабатывает сигнал сброса счетчика. Оба мультивибратора вырабатывают импульсы длительности необходимой для надежного переключения триггера.

Схема подсчета тактовых импульсов состоит из элемента «И» и счетчика. Элемент «И» пропускает тактовые импульсы от генератора, только если триггер находится в единичном состоянии. Счетчик обеспечивает подсчет импульсов.

Схема отображения содержит регистр, дешифратор и индикаторы. Использование регистра позволяет избежать мерцания во время подсчета. Запись в регистр выполняется только по окончанию подсчета длительности импульса. Дешифратор необходим для преобразования двоично-десятичного кода в код обеспечивающий отображение соответствующей цифры.

|

Рисунок 2. Функциональная схема

Схема преобразования параллельного кода в последовательный состоит из преобразования кода 8421 в код 8421+3 и сдвигового регистра обеспечивающего преобразование параллельного кода в последовательный.

В состав тактового генератора входит генератор прямоугольных импульсов заданной частоты и делитель частоты для сдвигового регистра.

Определим разрядность индикатора по формуле:

![]() ,

,

где ![]() - максимальное значение измеряемой величины;

- максимальное значение измеряемой величины; ![]() -точность измерения.

-точность измерения.

![]()

Разрядность регистра с параллельным вводом и последовательным выводом информации определим исходя из того, что для отображения каждого десятичного разряда требуется 4 бита:

![]()

2. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ УСТРОЙСТВА

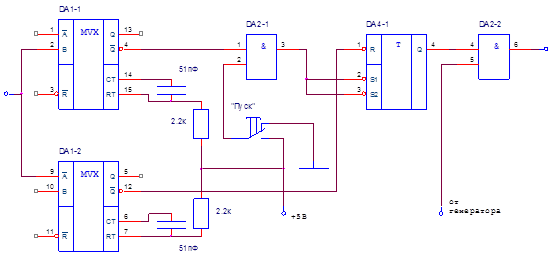

2.1 Проектирование схемы детектора фронтов

Рисунок 6. Схема детектора фронтов

|

Ждущий мультивибратор можно реализовать на основе микросхемы К155АГ3. Она содержит два ждущих мультивибратора с возможностью перезапуска. Каждый мультивибратор содержит выходы ![]() и

и ![]() , вход сброса

, вход сброса ![]() и два входа запуска:

и два входа запуска: ![]() - прямой и

- прямой и ![]() - инверсный, с активным низким уровнем.

- инверсный, с активным низким уровнем.

Длительность импульса (при

Длительность импульса (при ![]() ) вычислим по формуле:

) вычислим по формуле:

![]() .

.

Паразитная емкость вывода RT на землю около 50пФ, поэтому максимальное время выходного импульса 40нс.

Потребляемый микросхемой К155АГ3 ток составляет 66мА, стекающий коллекторный ток выводов может быть до 40мА.

Вход ![]() используется для прямого запуска мультивибратора. Сигнал сброса формируется с помощью RC звена: времязадающий конденсатор

используется для прямого запуска мультивибратора. Сигнал сброса формируется с помощью RC звена: времязадающий конденсатор ![]() подключается между выводами 14 и 15 а также 6 и 7; резисторы

подключается между выводами 14 и 15 а также 6 и 7; резисторы ![]() подключаются от выводов 15 и 7 к положительной шине питания 5В. Примем номиналы

подключаются от выводов 15 и 7 к положительной шине питания 5В. Примем номиналы ![]() и

и ![]() :

:

Триггер можно реализовать на основе микросхемы К555ТР2. Она содержит 4 независимых RS - триггера, имеющих общую шину питания. У каждого триггера есть входы

Триггер можно реализовать на основе микросхемы К555ТР2. Она содержит 4 независимых RS - триггера, имеющих общую шину питания. У каждого триггера есть входы ![]() и

и ![]() , а также комплиментарный выход

, а также комплиментарный выход ![]() .

.

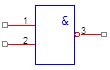

Логический элемент «И» можно реализовать на основе микросхемы К155ЛИ1. Она содержит четыре логических элемента «И». Время задержки для микросхемы К155ЛИ1: ![]() ,

, ![]() , потребляемый ток

, потребляемый ток ![]() ,

, ![]() .

.

Схема детектора фронтов и электронного ключа отображена на рисунке 6. Между микросхемой К155АГ3 и RS триггером стоит логический элемент «И», на один вход которого подается логический нуль и предусмотрена кнопка «Пуск» для установки RS триггера в исходное (нулевое) состояние. В качестве элемента «И» используется один элемент микросхемы К155ЛИ1.

Схема детектора фронтов и электронного ключа отображена на рисунке 6. Между микросхемой К155АГ3 и RS триггером стоит логический элемент «И», на один вход которого подается логический нуль и предусмотрена кнопка «Пуск» для установки RS триггера в исходное (нулевое) состояние. В качестве элемента «И» используется один элемент микросхемы К155ЛИ1.

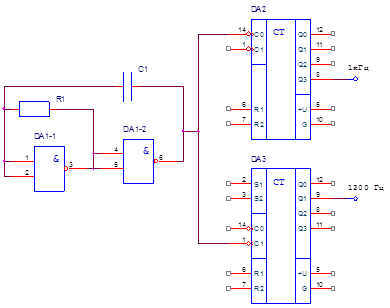

2.2. Генератор тактовых импульсов

Рисунок 7. Схема тактового генератора

|

Для работы счетчика и сдвигового регистра необходим генератор тактовых импульсов. Схема генератора приведена на рисунке 7. Он построен на двух элементах И-НЕ микросхемы К155ЛА3. Частота генерации определяется из соотношения:

Для работы счетчика и сдвигового регистра необходим генератор тактовых импульсов. Схема генератора приведена на рисунке 7. Он построен на двух элементах И-НЕ микросхемы К155ЛА3. Частота генерации определяется из соотношения:

![]() ,

,

где НОК - наименьшее общее кратное,

где НОК - наименьшее общее кратное,

![]() - точность измерения,

- точность измерения,

![]()

![]() - скорость передачи.

- скорость передачи.

![]()

Частота генерации определяется как:

![]() .

.

Приняв ![]() , определим номинал резистора:

, определим номинал резистора:

![]()

Примем значение из номинального ряда ![]() .

.

Для получения частот в 10000Гц и 1200Гц необходимо применить делители частоты. В качестве делителей удобно использовать счетчики К155ИЕ2 и К155ИЕ4. Для реализации деления на 5 используем счетчик К155ИЕ2 (DA3) подавая тактовые импульсы на вход C1 на выходе Q1 получим частоту деленную на 5. Для реализации деления на 6 используем счетчик К155ИЕ4.

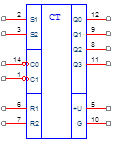

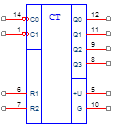

2.3 Схема подсчета тактовых импульсов

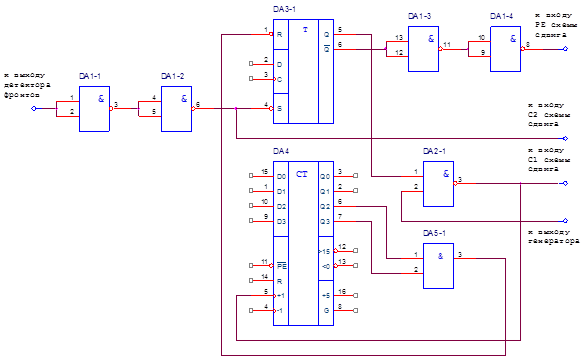

Рисунок 8. Схема подсчета тактовых импульсов

|

Для реализации схемы подсчета тактовых импульсов используем счетчики К155ИЕ6. В этих счетчиках имеется возможность последовательного подключения с целью увеличения разрядности. При этом выход «>15» подключается к тактовому входу следующего счетчика. Для получения на выходе 12 разрядного двоично-десятичного кода требуется 3 счетчика К155ИЕ6. Вывод переноса последнего счетчика используем для индикации ошибки.

Для реализации схемы подсчета тактовых импульсов используем счетчики К155ИЕ6. В этих счетчиках имеется возможность последовательного подключения с целью увеличения разрядности. При этом выход «>15» подключается к тактовому входу следующего счетчика. Для получения на выходе 12 разрядного двоично-десятичного кода требуется 3 счетчика К155ИЕ6. Вывод переноса последнего счетчика используем для индикации ошибки.

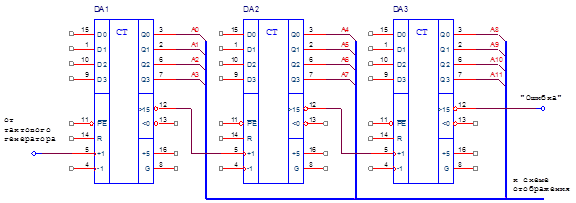

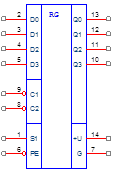

2.4 Схема преобразования параллельного кода в последовательный

Рисунок 9. Схема преобразования

Для реализации схемы преобразования параллельного кода в последовательный выберем параллельно-последовательный регистр сдвига с параллельной записью данных К155ИР1. К155ИР1 - четырехразрядный сдвиговый регистр.

Для реализации схемы преобразования параллельного кода в последовательный выберем параллельно-последовательный регистр сдвига с параллельной записью данных К155ИР1. К155ИР1 - четырехразрядный сдвиговый регистр.

Вход разрешения параллельной загрузки ![]() служит для выбора режима работы регистра. Если на вход

служит для выбора режима работы регистра. Если на вход ![]() подается напряжение высокого уровня, разрешается работа тактового входа C2. В момент прихода на этот вход отрицательного перепада тактового импульса в регистр загружаются данные с параллельных входов D0-D3.

подается напряжение высокого уровня, разрешается работа тактового входа C2. В момент прихода на этот вход отрицательного перепада тактового импульса в регистр загружаются данные с параллельных входов D0-D3.

Если на вход ![]() подано напряжение низкого уровня, то разрешается работа тактовому входу С1. Отрицательные фронты последовательности тактовых импульсов сдвигают данные от последовательности входа S1 на выход Q0, затем на Q1,Q2,Q3, т.е. вправо.

подано напряжение низкого уровня, то разрешается работа тактовому входу С1. Отрицательные фронты последовательности тактовых импульсов сдвигают данные от последовательности входа S1 на выход Q0, затем на Q1,Q2,Q3, т.е. вправо.

Для построения 12 разрядного регистра сдвига необходимо соединить 3 регистра последовательно, причем выход Q3 предыдущего регистра соединяется со входом S1 последующего.

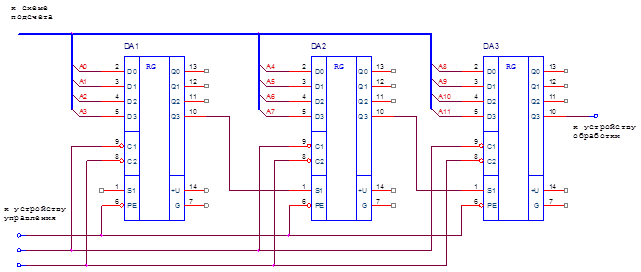

2.5 Схема управления

|

Рисунок 10. Схема управления

Для согласования отдельных узлов устройства необходима схема управления. В ее функции входит следующее:

· Управление записью данных в регистры сдвига

· Управление сдвигом данных записанных в регистры сдвига

· Прекращение передачи данных в устройство обработки после передачи 12 разрядов

Анализ вышесказанного, позволяет сделать следующие выводы о необходимых компонентах схемы управления:

1. Для управления сдвигом потребуется счетчик с пересчетом до 12

2. Для прекращения передачи потребуется электронный ключ на триггере

3. Для согласования по времени переключения логических элементов потребуются элементы задержки.

Предлагаемая схема управления изображена на рисунке 10.

По заднему фронту изменяемого импульса с выхода детектора фронтов на входную схему задержки поступает положительный импульс. Со схемы задержки этот импульс поступает на вход ![]() триггера (электронного ключа), а также на вход C2 регистров сдвига. На выходе

триггера (электронного ключа), а также на вход C2 регистров сдвига. На выходе ![]() формируется логический ноль и через элемент задержки поступает на вход

формируется логический ноль и через элемент задержки поступает на вход ![]() регистров сдвига, что переводит регистры в режим сдвига. После поступления заднего фронта импульса на вход С2 регистров сдвига происходит запись в эти регистры с выхода схемы подсчета. В это время триггер уже установлен в единичное состояние и логическая единица с выхода

регистров сдвига, что переводит регистры в режим сдвига. После поступления заднего фронта импульса на вход С2 регистров сдвига происходит запись в эти регистры с выхода схемы подсчета. В это время триггер уже установлен в единичное состояние и логическая единица с выхода ![]() поступает на элемент «И-НЕ», что дает возможность тактовым импульсам поступать на вход C1 регистров сдвига. По достижении счетчиком значения 12 через элемент «И» сигнал поступает на вход R триггера и переводит его в нулевое состояние, тем самым закрывая тактовым импульсам путь через элемент «И-НЕ».

поступает на элемент «И-НЕ», что дает возможность тактовым импульсам поступать на вход C1 регистров сдвига. По достижении счетчиком значения 12 через элемент «И» сигнал поступает на вход R триггера и переводит его в нулевое состояние, тем самым закрывая тактовым импульсам путь через элемент «И-НЕ».

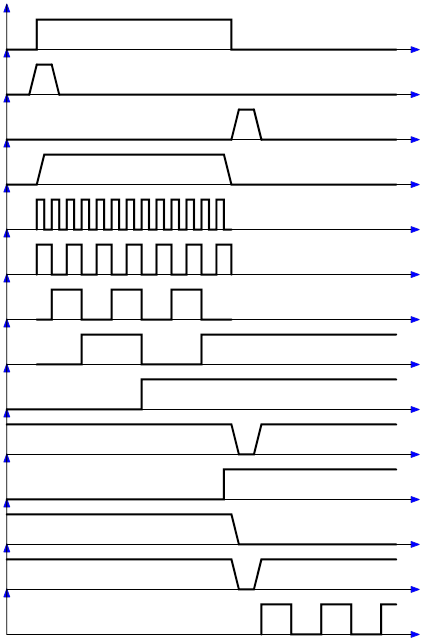

|

Рисунок 11. Временные диаграммы работы устройства

3. Заключение

При выполнении данной курсовой работы были проведены расчет и построение узлов и комбинационных схем.

Учитывались основные параметры влияющие на работу цифрового устройства. Был произведен синтез структурной, функциональной и электрической принципиальной схем заданного устройства, выбраны и обоснованы критерии подбора интегральных микросхем, проведена их сравнительная оценка.

Список ЛИТЕРАТУРЫ

1. Методические указания к курсовой работе по дисциплине «Цифровая схемотехника» на тему «Проектирование цифрового устройства».

2. Шило В.Л. Популярные цифровые микросхемы: справочник, - Москва; металлургия, 1988,-352 с.

3. Орнадский П.П. Автоматические измерения и приборы. - К.; Техника,1990 - 448с.

4. Цифровые и аналоговые интегральные микросхемы: Справочник / С.В.Якубовский, Л.И.Нильсон, В.И.Кулешова и др./ Под ред. С.В.Якубовского.-М.: Радио и связь, 1990.-496с.

ПРИЛОЖЕНИЕ 1. Алгоритм работы устройства

|