| Скачать .docx |

Реферат: Шпаргалка по Цифровому устройству

ВОПРОС 1. Одной из наиболее увлекательных и полезных областей применения электроники является сбор и обработка информации об эксперименте. Существует ряд наук, основанных на опыте и неспособных обойтись без него. Одна из таких наук – физика. Сигналы должны быть представлены в цифровом виде.Преобразование сигнала из аналоговой в цифровую форму осуществляется с помощью аналого-цифровых преобразователей (АЦП). Получаемый цифровой сигнал вводится в управляющую ЭВМ или микроконтроллер с помощью портов ввода, обрабатывается, и выводится с использованием портов вывода. Обратное преобразование цифрового сигнала в аналоговый осуществляется с помощью цифро-аналоговых преобразователей (ЦАП). Совокупность перечисленных элементов (датчик – АЦП – ЭВМ – ЦАП – исполнительное устройство) в различных комбинациях позволяет создавать системы управления широкого применения, использующиеся и для автоматизации научных исследований.

Что нужно для автоматизированного эксперимента?

-Экспериментальная установка. Но непростая, а оснащенная датчиками, измерительными устройствами для дистанционных измерений и если необходимо, исполнительными устройствами для дистанционного управления.

-Аппаратура. Измерительная и управляющая. Какие будут применяться приборы — зависит от выполняемого эксперимента

-Линии связи экспериментальной установки с аппаратурой. По ним передаются измерительные и управляющие сигналы.

-ЭВМ.

-Интерфейс. Это средство связи ЭВМ с аппаратурой. По интерфейсу осуществляется прием/передача данных и команд.

-Методика проведения автоматизированного эксперимента. Обязательно учитывает увеличение скорости сбора данных и объема данных, ориентируется на новые методы анализа данных.

-Программа на ЭВМ.

Обычно автоматизируются только два этапа эксперимента.

Этап 1.Процесс эксперимента (полного объема данных еще нет). I Управление приборами. Сбор данных. Простевшая первичная обработка данных. Запись данных на магнитный носитель для последующей обработки. Этап 2. Вторичная обработка данных (объем данных уже полный). 1 Выработка математических моделей. Описание опытных данных формулами. Создание базы данных. Использование данных в разработке теоретических моделей изучаемого процесса.

ВОПРОС 2

Обычно автоматизируются только два этапа эксперимента.

Этап 1.

Процесс эксперимента (полного объема данных еще нет). I Управление приборами. Сбор данных. Простевшая первичная обработка данных. Запись данных на магнитный носитель для последующей обработки

Здесь от ЭВМ требуется только способность управлять приборами в реальном времени. Но объем памяти и быстродействие для большинства экспериментов на этом этапе не критичны. Продуктивная активность ЭВМ сводится к посылке на прибор команды запуска процесса измерения, ожиданию готовности данных и. наконец, к приему от прибора уже готовых данных

Этап 2.

Вторичная обработка данных (объем данных уже полный). 1 Выработка математических моделей. Описание опытных данных формулами. Создание базы данных. Использование данных в разработке теоретических моделей изучаемого процесса.

Здесь от ЭВМ уже не требуется способность управлять приборами. Однако появляется необходимость в высоком быстродействии и достаточном объеме памяти.

Если на обоих этапах использовать одну ЭВМ, то мы наверняка встретимся с противоречивой ситуацией. Если ЭВМ мощная, то на этапе выполнения эксперимента она будет фактически простаивать. Если же ЭВМ слабая, то трудно будет выполнить серьезную вторичную обработку данных.ТАКИМ ОБРАЗОМ, ДЛЯ ЭВМ ОПТИМАЛЬНОЙ СС ПО ЗАТРАТАМ ОБОРУДОВАНИЯ ЯВЛЯЕТСЯ ТРОИЧНАЯ, А ЗАТЕМ, ЧУТЬ ХУЖЕ, ДВОИЧНАЯ. УЧИТЫВАЯ ТО, ЧТО МНОГИЕ АЛГОРИТМЫ АРИФМЕТИЧЕСКИХ ОПЕРАЦИЙ В ДВОИЧНОЙ СС ВЫПОЛНЯЮТСЯ ПРОЩЕ, ЧЕМ В ТРОИЧНОЙ, И НАМНОГО БЫСТРЕЕ И УДОБНЕЙ ЗАПОМИНАТЬ И ПЕРЕДАВАТЬ ЦИФРЫ 1,0 (ВКЛЮЧЕНО, ВЫКЛЮЧЕНО), ВСЯ ИНФОРМАЦИЯ В ЭВМ КОДИРУЕТСЯ, ПРЕОБРАЗУЕТСЯ И ЗАПОМИНАЕТСЯ В ДВОИЧНОЙ СС. КРОМЕ ДВОИЧНОЙ СС ИЗ-ЗА КРАТНОСТИ ОСНОВАНИЙ ИСПОЛЬЗУЮТСЯ ТАКЖЕ ВОСЬМЕРИЧНАЯ И ШЕСТНАДЦАТЕРИЧНАЯ СС, ЦИФРЫ И СИМВОЛЫ КОТОРЫХ КОДИРУЮТСЯ ДВОИЧНЫМИ ЭКВИВАЛЕНТАМИ.

ВОПРОС 3

Алгебра логики оценивает высказывания. Под высказыванием понимают любое утверждение, в отношении которого имеет смысл утверждать, истинно оно или ложно. Высказывания могут быть простыми и сложными (простыми - если они содержат одну простую законченную мысль, сложными - если образованы из двух или более простых высказываний). Простые высказывания называют логическими переменными, а сложные - логическими функциями этих переменных.

Считают, что высказывание равно 1, если оно истинно, и равно 0, если оно ложно. Два высказывания называют эквивалентными, если их значения истинности одинаковы.

Образование сложных высказываний из простых высказываний А, В, С,... осуществляется посредством основных логических операций (связей) НЕ, ИЛИ, И. Схемы, реализующие логические операции, называются логическими элементами.

Элементарные логические операции

-Конъюнкция (логическое умножение, операция И, AND).Для записи используется:

![]()

![]()

-Дизъюнкция (логическое сложение, операция ИЛИ, OR)

![]()

![]()

-Инверсия (отрицание, операция НЕ, NOT

![]()

![]()

Минимальный базис:

-Элемент И-НЕ реализует функцию двух переменных

![]()

![]()

-Элемент ИЛИ-НЕ реализует функцию: ![]()

![]()

ВОПРОС 5

Имея элементы, осуществляющие элементарные операции, можно выполнить любую сложную логическую операцию. Такую систему функций можно назвать полной системой или базисом.

Последовательно исключая из базиса функции, можно получить так называемый минимальный базис. Под минимальным базисом понимают такой набор функций, исключение из которого любой функции превращает полную систему в неполную.

С помощью логических операций И, ИЛИ, НЕ можно выразить любую другую из элементарных функций. Следовательно, эта совокупность логических функций образует базис. Это означает, что любая логическая функция, как бы сложна она ни была, может быть представлена через логические операции И, ИЛИ, НЕ. Иначе, можно построить любое логическое устройство, имея лишь три типа логических элементов, выполняющих операции И, ИЛИ, НЕ.

Базис И, ИЛИ, НЕ не является минимальным. Из этой совокупности функций можно исключить функцию И либо функцию ИЛИ и оставшийся набор будет удовлетворять свойствам базиса. Действительно, если исключить функцию И, то операцию И можно выразить через оставшиеся ИЛИ и НЕ, но это сложно, поэтому на практике используется не минимальный базис, включающий все три функции И, ИЛИ, НЕ.

Используются некоторые другие базисы. При этом выбранный набор логических функций будет удовлетворять свойствам базиса, если с помощью этого набора функций окажется возможным выразить функции И и НЕ (либо функции ИЛИ и НЕ).

• Базис образует функция Шеффера (И-НЕ) (рис. 2а). Элементов одного типа, реализующих функцию И-НЕ, достаточно для построения логического устройства произвольной сложности.

• Базис образует функция Вебба (ИЛИ-НЕ) (рис. 2б). Используя однотипные элементы, реализующие операцию ИЛИ-НЕ, можно построить логическое устройство произвольной сложности.

• В настоящее время базис И, ИЛИ, НЕ обычно используется при начальной стадии проектирования устройств для построения функциональной схемы. Для реализации устройств обычно используются базисы И-НЕ либо ИЛИ-НЕ. Элементы этого базиса широко выпускаются промышленностью в интегральном исполнении.

• Логические элементы могут быть выполнены на диодах, транзисторах и в интегральном исполнении. Интегральные логические элементы завоевали в последние годы основные позиции в электронном машиностроении. Интегральное исполнение логических схем обеспечивает высокую плотность размещения элементов, что значительно сокращает размеры, массу модулей, повышает их надежность, быстродействие и т. д.

• Наибольшее распространение получили интегральные элементы, построенные на транзисторах и использующие в качестве межкаскадных связей транзисторы (элементы транзисторно-транзисторной логики ТТЛ).

• Основой каждой серии является базовый логический элемент. Как правило, базовые логические элементы выполняют операции И - НЕ либо ИЛИ - НЕ и по принципу построения делятся на следующие основные типы: элементы диодно-транзисторной (ДТЛ), резистивно-транзисторной логики (РТЛ), транзисторно-транзисторной логики (ТТЛ), эмиттерно-связанной транзисторной логики (СТЛ), микросхема на так называемых комплиментарных структурах (КМДП или КМОП). Элементы КМДП (КМОП) цифровых микросхем используют пары МДП-транзисторов (со структурой металл-диэлектрик-полупроводник) - с каналами р - и n -типов.

• В радиолюбительской практике наибольшее распространение получили микросхемы ТТЛ серии К155 и КМДП (КМОП) серии К176 и К561.

• Имеется свыше 100 наименований микросхем серии К155. При всех своих преимуществах - высоком быстродействии, обширной номенклатуре, хорошей помехоустойчивости - эти микросхемы обладают большой потребляемой мощностью. Поэтому им на смену выпускают микросхемы серии К555, принципиальное отличие которых - использование транзисторов с коллекторными переходами, зашунтированными диодами Шоттки. В результате транзисторы микросхем серии К555 не входят в насыщение, что существенно уменьшает задержку выключения транзисторов.

• Дальнейшее развитие микросхем серий ТЛЛ - разработка микросхем серии КР1533. Основное эксплуатационное отличие их от схем серии К555 - в 1,5 . . . 2 раза меньше потребляемая мощность при сохранении и повышения быстродействия.

• В настоящее время выпускается огромное количество разнообразных цифровых микросхем: от простейших логических элементов до сложнейших процессоров, микроконтроллеров и специализированных БИС (Больших Интегральных Микросхем). Производством цифровых микросхем занимается множество фирм — как у нас в стране, так и за рубежом. Поэтому даже классификация этих микросхем представляет собой довольно трудную задачу.

• Однако в качестве базиса в цифровой схемотехнике принято рассматривать классический набор микросхем малой и средней степени интеграции, в основе которого лежат ТТЛ серии семейства 74, выпускаемые уже несколько десятилетий рядом фирм, например, американской фирмой Texas Instruments (TII). Эти серии включают в себя функционально полный комплект микросхем, используя который, можно создавать самые разные цифровые устройства.

• Рис. 2.5. Система обозначений фирмы Texas Instruments

Каждая микросхема серий семейства 74 имеет свое обозначение, и система обозначений отечественных серий существенно отличается от принятой за рубежом.

• Обозначения отечественных микросхем

• Отечественная система обозначений микросхем отличается от рассмотренной довольно существенно (рис. 2.6). Основные элементы обозначения следующие:

• Буква К обозначает микросхемы широкого применения, для микросхем военного назначения буква отсутствует.

• Тип корпуса микросхемы (один символ) — может отсутствовать. Например, Р — пластмассовый корпус, М — керамический, Б — бескорпусная микросхема.

• Номер серии микросхем (от трех до четырех цифр).

• Функция микросхемы (две буквы).

• Номер микросхемы (от одной до трех цифр). Таблица функций и номеров микросхем, а также таблица их соответствия зарубежным аналогам приведены в приложении.

• Например, КР1533ЛА3, КМ531ИЕ17, КР1554ИР47.

• Главное достоинство отечественной системы обозначений состоит в том, что по обозначению микросхемы можно легко понять ее функцию. Зато в системе обозначений Texas Instruments виден тип серии с его особенностями.

ВОПРОС 6

Триггер - одно из наиболее распространенных импульсных устройств, относящихся к базовым элементам цифровой техники.

Триггером называют устройство, обладающее двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала.

Триггер может использоваться для хранения значения одной логической переменной (или значения одноразрядного двоичного числа; при хранении многоразрядных двоичных чисел для запоминания значения каждого разряда числа используется отдельный триггер). В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние логического 0, другое - состояние логической 1.

Воздействуя на входы триггера, его устанавливают в нужное состояние.

Триггер имеет два выхода: прямой Q и инверсный . Уровнями напряжения на этих выходах определяется состояние, в котором находится триггер, если напряжение на выходе Q соответствует уровню логического 0 (Q = 0), то принимается, что триггер находится в состоянии логического 0. Логический уровень на инверсном выходе представляет собой инверсию состояния триггера (в состоянии 0 = 1 и наоборот).

• Триггеры имеют различные типы входов. Приведем обозначение и назначение входов триггеров:

• R (от английского RESET) - раздельный вход установки в состояние 0;

• S (от английского SET) - раздельный вход установки в состояние 1;

• К - вход установки универсального триггера в состояние 0;

• J - вход установки универсального триггера в состояние 1;

• Т - счетный вход;

• D - информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

• С - управляющий (синхронизирующий) вход.

• Т - счетный вход;

• D - информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

• С - управляющий (синхронизирующий) вход.

Наименование триггера определяется типами его входов. Например, RS-триггер, имеющий входы типов R и S.

По характеру реакции на входные сигналы триггеры делятся на два типа: асинхронные и синхронные. Асинхронный триггер характеризуется тем, что входные сигналы действуют на состояние триггера непосредственно с момента их подачи на входы, в синхронных триггерах - только при подаче синхронизирующего сигнала на управляющий вход С.

В современной электронике триггеры выполняются, как правило, в виде микросхем, построенных на основе логических элементов. На рис. 1а; 2а приведены схемы триггеров на логических элементах ИЛИ-НЕ, И-НЕ, а на рис. 1б; 2б показаны их условные обозначения.

RS-триггер с прямыми входами построен на двух логических элементах ИЛИ-НЕ, связанных таким образом, что выход каждого элемента подключен к одному из входов другого. Такое соединение элементов в устройстве обеспечивает два устойчивых состояния. Допустим, что на входах R и S сигналы равны лог. 0 (R = 0, S = 0), а на прямом выходе Q сигнал равен 1 (Q = 1). Тогда на инверсном выходе сигнал равен 0, т.к. на одном из входов (соединенном с Q) логического элемента ИЛИ-НЕ сигнал равен 1. На обоих входах элемента А сигнал 0, поэтому Q = 1. Очевидно, при R = 0 и S = 0 возможно и второе устойчивое состояние, при котором Q = 0, = 1. Не трудно увидеть, что при S = 1, R = 0 триггер оказывается в первом устойчивом состоянии (Q = 1, = 0), а при S = 0, R = 1 - во втором устойчивом состоянии (Q = 0, = 1).

Когда на обоих информационных входах существуют логические нули (S = 0, R = 0), сигналы на выходе могут иметь одно из двух сочетаний: Q = 1; = 0 либо Q = 0; = 1. Комбинацию входных сигналов S = R = 0 называют нейтральной, или режимом хранения информации, или памятью: при ней триггер хранит состояние, в которое он был приведен в предыдущем такте. На этой способности триггера и основано его использование в качестве элемента памяти

Если на один из входов подать единичный сигнал, сохраняя нулевой на другом, триггер примет состояние, которое однозначно определяется входной информацией. При входных сигналах S=1 и R=0 триггер примет единичное состояние (Q = 1), а при R = 1 и S = 0 - нулевое. Поэтому вход S иногда называют единичным, а вход R - нулевым. При появлении управляющего сигнала на одном из входов происходит либо переключение триггера, либо подтверждение существующего состояния, если оно совпадает с требуемым.

Если одновременно подать переключающие сигналы S = 1 и R = 1 на оба входа, то на обоих выходах появятся логические нули (Q = = 0) и устройство утратит свойство триггера, а после снятия со входов активных уровней состояние триггера окажется неопределенным: в силу случайных причин триггер может установиться в состояние 0 или 1. Поэтому комбинацию S = R = 1 называют неопределенной (или запрещенной).

Триггер, который переключается сигналами логической единицы, называют триггером с прямым управлением. Таблица состояний триггера с прямым управлением имеет вид (таблица 1).

Аналогично работает RS-триггер на элементах И-НЕ (рис. 2) с той лишь разницей, что он должен иметь инверсные входы, т.е. устанавливаться в состояние 1 при S = 0 и сбрасываться в состояние 0 при R = 0. Запрещенная комбинация входных сигналов для этой схемы - S = R = 0.

Этот вариант триггера называют RS-триггером с инверсными входами ( -триггер). На условных графических обозначениях подобные триггеры для наглядности изображают в отрицательной логике. Таблица переходов триггеров этого типа имеет вид (таблица 2).

Qо - предыдущее состояние триггера. Рассмотренные RS-триггеры относятся к асинхронным, т. к. переход его из одного состояния в другое происходит в темпе поступления сигналов на информационные (R, S) входы и не связан с таковыми сигналами.

ВОПРОС 7

В синхронных триггерах помимо информационных имеется вход тактовых (синхронизирующих) сигналов и переключения триггера происходят только при наличии тактового сигнала. Синхронный режим работы является основным в ЭВМ, на нем основан принцип действия ряда узлов цифровой техники, например, D-, JК-триггеров, регистров и т. д.

Синхронный триггер может переключаться только при наличии импульса на тактовом входе (С = 1). При отсутствии импульса на тактовом входе (С = 0) переключение не происходит ни при каких сигналах на входах S и R.

Таким образом, при С = 0 на входы синхронного триггера не передаются активные уровни и триггер сохраняет ранее установленное в нем состояние Q0 . При С = 1 состояние триггера определяется действующими на входах уровнями так же, как и в рассмотренном выше асинхронном RS-триггере.

Нормальная работа синхронного RS-триггера требует, чтобы за время действия логической 1 на синхронизирующем входе С уровни на информационных входах R и S оставались неизменными. Смена уровней на входах допускается лишь в то время, когда С = 0 и триггер не реагирует на уровни, действующие на входах S и R.

ВОПРОС 8

Для приема информации по одному входу используется D-триггер. На рис. 4а,б приведены схема и условное обозначение D-триггера. D-триггер имеет лишь один информационный вход, называемый входом D. Вход С - управляющий и служит для подачи синхронизирующего сигнала.

Функционирование D- триггера определяется сигналом на синхронизирующем входе. При С = 1 триггер устанавливается в состояние, определяемое логическим уровнем на входе D (при С = 0 он сохраняет ранее установленное состояние Q0 ).

На рис. 4б представлена логическая структура D-триггера, состоящего из асинхронного RS-триггера с логическими элементами на входе. При С = 0 на выходах (И-НЕ) образуются пассивные для входов асинхронного RS-триггера уровни. При С = 1 уровень поданный на информационный вход D, создает активный уровень либо на входе R (при D = 0), либо на входе S (при D = 1) асинхронного RS- триггера, и триггер устанавливается в состояние, соответствующее логическому уровню на входе D. Таким образом, D-триггер воспринимает информацию со входа D при С = 1 и затем ее может хранить неопределенно длительное время, пока С = 0.

Т-триггер или счетный триггер, имеет один информационный вход и переходит в противоположное состояние в результате воздействия на его вход каждого очередного сигнала. Название “счетный” или “ со счетным запуском” связано с широким применением Т- триггеров в счетчиках импульсов. На рис. 5а, б приведены условное обозначение и временные диаграммы Т-триггера.

Т-триггеры выполняются на основе двух последовательно соединенных RS-триггеров (МS-схема), первый из которых называют ведущим, а другой - ведомым. На рис. 6 а, б приведены схема и условное обозначение двухступенчатого триггера, в котором триггер Т1 - ведущий, а триггер Т2 - ведомый. При поступлении сигналов на информационные входы R и S триггера Т1 он принимает соответствующее состояние (0 или 1) в момент, когда С1 = 1. Сигналы с выходов Q1 и ведущего триггера не проходят, поскольку С2 = 0. Информация пройдет в ведомый триггер только по окончании синхронизирующего сигнала (С1 = 0, С2 = 1) и будет отражена на выходах Q2 .

ВОПРОС 9

Универсальный триггер, или JК-триггер, имеет информационные входы J и К и синхронизирующий вход С (рис. 7а). JК-триггер получают из двухступенчатого Т-триггера путем использования трехвходовых элементов И-НЕ во входных цепях ведущего триггера подобно тому, как используют двухвходовые элементы И-НЕ в схеме рис. 3а. Использование третьих входов И-НЕ позволяет реализовать два дополнительных информационных входа J и К (рис. 7а). При J = К = 1 триггер изменяет свое состояние на противоположное в момент окончания каждого синхронизирующего сигнала. Таким образом, соединяя входы JК-триггера по схеме рис. 7б, получают Т-триггер.

Универсальный триггер, или JК-триггер, имеет информационные входы J и К и синхронизирующий вход С (рис. 7а). JК-триггер получают из двухступенчатого Т-триггера путем использования трехвходовых элементов И-НЕ во входных цепях ведущего триггера подобно тому, как используют двухвходовые элементы И-НЕ в схеме рис. 3а. Использование третьих входов И-НЕ позволяет реализовать два дополнительных информационных входа J и К (рис. 7а). При J = К = 1 триггер изменяет свое состояние на противоположное в момент окончания каждого синхронизирующего сигнала. Таким образом, соединяя входы JК-триггера по схеме рис. 7б, получают Т-триггер.

ВОПРОС 10

Операционный элемент, состоящий из триггеров, основным назначением которого является прием и хранение чисел с двоичным представлением цифр разрядов, называется регистром. Однако с помощью некоторых видов регистров можно выполнять и следующие элементарные операции: установку, сдвиг и преобразование. Основными типами регистров являются параллельные и последовательные (сдвигающие). В качестве основного элемента регистра используется D-триггер (рис. 1).

В параллельном регистре на тактируемых D-триггерах (рис. 2) код запоминаемого числа подается на информационные входы всех триггеров и записывается в регистр с приходом тактового импульса.

Выходная информация изменяется с подачей нового входного слова и приходом следующего импульса записи. Такие регистры используют в системах оперативной памяти. Число триггеров в них равно максимальной разрядности хранимых слов. На рисунке 3 приведены условные графические обозначения ИМС К155ТМ7 и К561ТМ3, которые можно использовать в качестве параллельных четырехразрядных регистров. Путем простого объединения входов нескольких микросхем можно получить параллельный регистр на 8 и более разрядов.

ВОПРОС 11

Операционный элемент, состоящий из триггеров, основным назначением которого является прием и хранение чисел с двоичным представлением цифр разрядов, называется регистром. Однако с помощью некоторых видов регистров можно выполнять и следующие элементарные операции: установку, сдвиг и преобразование. Основными типами регистров являются параллельные и последовательные (сдвигающие). В качестве основного элемента регистра используется D-триггер

Схема последовательного регистра на D-триггерах с динамическим управлением и временная диаграмма, иллюстрирующая его работу, приведены на рисунке 4. По приходу тактового импульса первый триггер записывает код X (0 или 1), находящийся в этот момент на его D-входе, а каждый следующий триггер переключается в состояние, в котором до этого находился предыдущий. Так происходит потому, что записываемый сигнал проходит с входа D-триггера к выходу Q с задержкой, большей длительности переднего фронта тактового импульса, в течение которого и происходит запись.

Каждый тактовый импульс последовательно сдвигает код числа на один разряд. Поэтому для записи n-разрядного кода требуется n тактовых импульсов. Из диаграммы следует, что четырехразрядное число 1011 было записано в соответствующие разряды регистра (1- Q4, 0- Q3, 1- Q2, 1- Q1) после прихода четвертого тактового импульса. До следующего тактового импульса это число хранится в регистре в виде параллельного кода на выходах Q4, Q3, Q2, Q1. Если необходимо получить хранимую информацию в последовательном коде, то ее снимают с выхода Q4 в моменты прихода следующих четырех импульсов (5-8). Такой режим называется режимом последовательного считывания.

ВОПРОС 12

Операционный элемент, состоящий из триггеров, основным назначением которого является прием и хранение чисел с двоичным представлением цифр разрядов, называется регистром. Однако с помощью некоторых видов регистров можно выполнять и следующие элементарные операции: установку, сдвиг и преобразование. Основными типами регистров являются параллельные и последовательные (сдвигающие). В качестве основного элемента регистра используется D-триггер

Очень удобны универсальные регистры, позволяющие производить как последовательную, так и параллельную запись и считывание. Такие регистры можно использовать в качестве преобразователей параллельного кода в последовательный и обратно. В серии К155 есть микросхема К155ИР1 - четырехразрядный универсальный сдвиговый регистр (рис. 5). Регистр работает в режиме сдвига по тактовым импульсам, поступающим на вход C1, при V=0. Если на управляющем входе V напряжение высокого уровня, то регистр производит параллельную запись информации с входов D1, D2, D3, D4 по импульсу синхронизации, поступающему на вход C2. На базе универсального регистра можно построить реверсивный сдвигающий регистр.

Для этого входы D1, D2 и D3 подключают соответственно к выходам Q2, Q3, Q4. Если информацию подавать на вход D0, а импульсы синхронизации - на C1, то при V=0 регистр производит сдвиг в сторону возрастания номеров выходов (сдвиг вправо). Если же информацию подавать на вход D4, а синхроимпульсы - на C2, то при V=1 регистр будет производить сдвиг в сторону уменьшения номеров выходов (сдвиг влево).

вопрос 13

Счетчик - цифровое устройство, осуществляющее счет числа появлений на входе определенного логического уровня. При импульсном представлении логических переменных уровню логической единицы соответствует импульс, и счетчик ведет счет поступающих на вход импульсов.

Обычно счетчик строят на основе триггеров. Триггер Т- типа может служить примером простейшего счетчика. Такой счетчик считает до двух. Счетчик, образованный цепочкой из m триггеров, сможет подсчитать в двоичном коде 2m импульсов. Каждый из триггеров такой цепочки называют разрядом счетчика. Число m определяет количество разрядов двоичного числа, которое может быть записано в счетчик. Число К сч =2 называют коэффициентом (модулем) счета.

Информация снимается с прямых и (или) инверсных выходов всех триггеров. В паузах между входными импульсами триггеры сохраняют свое состояние, т.е. счетчик запоминает число сосчитанных импульсов.

Нулевое состояние всех триггеров принимается за нулевое состояние счетчика в целом. Остальные состояния нумеруются по числу поступивших входных импульсов.

Когда число входных импульсов N вх > К сч , при N вх =К сч происходит переполнение, после чего счетчик возвращается в нулевое состояние и повторяет цикл работы. Коэффициент счета, таким образом, характеризует количество входных импульсов, необходимое для выполнения одного цикла и возвращения в исходное состояние.

Цифровые счетчики классифицируются следующим образом:

по коэффициенту (модулю) счета: двоичные, двоично-десятичные (декадные) или с другим основанием счета;

по направлению счета: суммирующие, вычитающие, реверсивные;

по способу организации внутренних связей: с последовательным переносом, с параллельным переносом, с комбинированным переносом, кольцевые.

Функциональная схема простейшего двоичного трехразрядного цифрового счетчика импульсов приведена на рис. 1а. Счетчик состоит из трех последовательно соединенных Т-триггеров, имеющих вход для установки в состояние 0. На рис. 1б показаны временные диаграммы счетчика. Таблица 1 иллюстрирует состояние триггеров. Если в исходном положении все триггеры были в состоянии 0, то по окончании первого входного импульса триггер Т1 перейдет в состояние 1 (х0 =1). По окончании второго входного импульса триггер Т1 переходит в состояние 0 (х0 =0). По окончании второго входного импульса триггер Т2 переходит в состояние 1 (х1 =1) и т. д. После восьмого входного импульса все триггеры переходят в состояние 0 и счет повторяется.

Из таблицы 1 видно, что состояние триггеров отражает число поступивших на вход счетчика импульсов в двоичной системе счисления (двоичном коде). Общее число возможных состояний N сч счетчика определяют числом триггеров m : N сч =2m . В нашем случае m =3, N сч = 23 =8.

Таблица 1. Таблица переходов двоичного счетчика.

| Номер входного импульса | Состояние триггеров | Номер входного импульса | Состояние триггеров | ||||

| Т3 | Т2 | Т1 | Т3 | Т2 | Т1 | ||

0 1 2 3 4 |

0 0 0 0 1 |

0 0 1 1 0 |

0 1 0 1 0 |

5 6 7 8 |

1 1 1 0 |

0 1 1 0 |

1 0 1 0 |

Условное обозначение счетчика по схеме рис. 1а приведено на рис. 1в. Символом счетчика на схемах служат буквы СТ (от англ. counter - счетчик). Если требуется, после символа проставляют число, характеризующее модуль счета (например, 2 или 10). На рис. 1в СТ2 означает двоичный счетчик, выводы 1, 2, 4 - обозначения двоичных разрядов 20 =1, 21 =2, 22 =4), соответствующих выходам х0 , х1 , х2 схемы рис. 1а, С1 - счетный вход; R - установка нуля.

Для получения счетчика, работающего в другом коде, применяют обратные связи. Введением дополнительных логических связей - обратных к прямым - двоичные счетчики могут быть обращены в недвоичные, для которых К сч ¹ 2. Наибольшее распространение получили десятичные (декадные) счетчики, работающие с привычными К сч = 10. Десятичный счет осуществляется в двоично-десятичном коде (двоичный по коду счета, десятичный по числу состояний).

Десятичные счетчики организуются из четырехразрядных двоичных счетчиков. Избыточные шесть состояний исключаются введением дополнительных связей.

вопрос 14

Рассмотренные счетчики выполняют операцию суммирования числа импульсов, поступающих на вход, поэтому их называют суммирующими. В суммирующем счетчике каждый входной импульс увеличивает число, записанное в счетчик, на единицу. Перенос информации из одного разряда в другой, более высокий, имеет место, когда происходит смена состояний с 1 на 0.

Вычитающий счетчик действует обратным образом: двоичное число, хранящееся в счетчике, с каждым поступающим импульсом уменьшается на единицу. Переполнение вычитающего счетчика происходит после достижения им нулевого состояния. Перенос из младшего разряда в старший здесь имеет место при смене состояния младшего разряда с 0 на 1. Реверсивный счетчик может работать в качестве суммирующего и вычитающего. Эти счетчики имеют дополнительные входы для задания направления счета. Режим работы определяется управляющими сигналами на этих входах.

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которых импульсы, подлежащие счету, поступают на вход первого триггера, а сигнал переноса передается последовательно от одного разряда к другому.

Счетчики с параллельным переносом состоят из синхронных триггеров. Счетные импульсы передаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующим только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, и задержка переключения всего счетчика равна задержке для одного триггера. Счетчики с параллельным переносом широко применяются в быстродействующих устройствах.

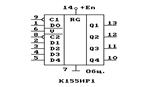

Цифровые счетчики импульсов выполняют в виде интегральных микросхем. В серии К155, например, это счетчики К155ИЕ2, К155ИЕ4, К155ИЕ5 и др. Суммирующие счетчики - делители с последовательным переносом типа К155ИЕ2, К155ИЕ4 и К155ИЕ5 близки по логическим структурам и принципу действия. Они состоят из четырех одинаковых JК-триггеров, используемых в зависимости от внутренней структуры микросхемы по прямому назначению либо как Т-триггеры.

Кроме суммирующих широко применяются реверсивные счетчики на микросхемах К155ИЕ6 и К155ИЕ7, у которых в зависимости от режима работы содержимое счетчика или увеличивается на единицу (режим сложения), или уменьшается на единицу (режим вычитания) после прихода очередного счетного импульса.

Интегральные микросхемы К155ИЕ6 и К155ИЕ7 (рис. 8а)- реверсивные счетчики с предварительной записью первый из них - двоично-десятичный, второй - четырехразрядный двоичный, оба они работают в коде 1-2-4-8.

ВОПРОС 19

Полусумматоры

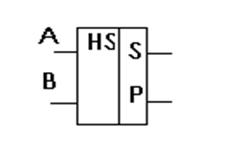

Простейшим суммирующим элементом является полусумматор. Он имеет два входа (рис. 1) X1 и X2 для двух слагаемых и два выхода : S (сумма) и Р (перенос).

Обозначением полусумматора служат буквы HS (half sum - полусумма), работу прибора отображает таблица истинности (табл. 1).

Таблица 1. Таблица истинности полусумматора.

| входы | выходы | ||

| A | B | P | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

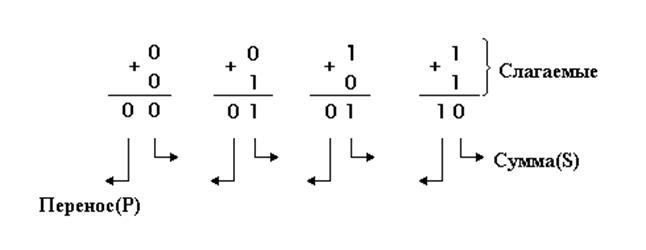

Два одноразрядных числа при сложении в двоичной системе счисления дают применительно к суммирующим устройствам такие результаты (рис. 2).

Полный сумматор

Процедуру сложения двух n-разрядных двоичных чисел можно представить следующим образом (рис. 3б).

Сложение цифр A1 и B2 младшего разряда дает бит суммы S1 и бит переноса Р1. В следующем (втором) разряде происходит сложение цифр Р1, А2, и В2, которое формирует сумму S2 и перенос Р2. Операция длится, пока не будет сложена каждая пара цифр во всех разрядах. Результатом сложения будет число S=PnSn...S1 , где Рn и Si отображают 1 или 0, полученные в результате поразрядного сложения.

Полусумматор имеет два входа и пригоден поэтому для использования только в младшем разряде. Устройство для суммирования двух многоразрядных чисел должно иметь, начиная со второго разряда, три входа: два для слагаемых X1 и X2 и один для сигнала переноса Рi-1 c предыдущего разряда. Этот узел - сумматор можно представить как объединение двух полусумматоров (рис. 3в).

Операция вычитания обратная операции сложения. Вычитание одного двоичного числа из другого в двоичной системе подобно вычитанию в десятичной системе (рис. 6).

Последний столбец характеризует вычитание с займом для вычитания 1 из 0 из соседнего старшего разряда занимается 1. Эта занимаемая 1 равна двум 1 данного разряда. Заем производится для тех разрядов, где вычитаемое больше уменьшаемого.

ВОПРОС 20

На рис. 5 показана схема, поясняющая принцип действия n-разрядного параллельного сумматора с последовательным переносом. Число сумматоров здесь равно числу разрядов. Выход переноса Р каждого сумматора соединен со входом переноса следующего, более старшего разряда. На входе переноса сумматора первого разряда установлен нулевой потенциал, поскольку сигнал переноса сюда не поступает. Слагаемые Ai и Bi складываются во всех разрядах одновременно, а перенос Р поступает с окончанием операции сложения в предыдущем разряде.

ВОПРОС 21

Запоминающие устройства (ЗУ) предназначены для записи, хранения и выдачи информации в ЭВМ. Они позволяют сохранять (фиксировать) данные, промежуточные вычисления, константы, коды команд. Фиксация предполагает запись информации в ЗУ, после чего она там хранится, а при необходимости по запросам извлекается или считывается, т.е. осуществляется чтение ЗУ. Сохраняемая в ЗУ информация кодируется в 2 СС одинарными, двойными, счетверенными словами или байтами. Каждый байт содержит 8 бит. Бит – наименьшая емкость двоичной памяти, способной хранить только «0» или «1». В слове можно разместить 2 байта, двойное слово содержит 4 байта, счетверенное – 8 байт. Все ЗУ разбивается на отдельные ячейки. Каждая ячейка имеет возможность (доступ) осуществлять запись, хранение и считывание информации величиной, равной ее разрядности, за одно обращение.

По способам поиска информации различают адресные и ассоциативные ЗУ. В адресных ЗУ каждая ячейка имеет свой номер – адрес, по которому осуществляется обращение к ней. В ассоциативных ЗУ поиск ячейки ведется по некоторым закодированным признакам – запросам, т.е. «по содержанию». Таким признаком может быть, например, содержание части разрядов любой ячейки, передаваемой в ЗУ как ключ для обнаружения тех ячеек, где он имеется Адресные ЗУ для поиска одной искомой ячейки используют дешифраторы. Ассоциативные осуществляют поиск по всему массиву ЗУ схемами сравнения.

Основными параметрами ЗУ является емкость, быстродействие и стоимость . Емкость ЗУ выражается в битах, байтах, килобайтах (Кб), мегабайтах (Мб), гигабайтах (Гб) и терабайтах (Тб). Быстродействие ЗУ определяется временем считывания данных в цикле чтения t ЦЧ и временем передачи в цикле записи t ЦЗ . В общем виде t ЦЧ , t ЦЗ можно вычислить по формулам:

t ЦЗ = t П + t С + t З ;

t ЦЧ = t П + t Ч + t Р ,

где t П – время, затрачиваемое в ЗУ на поиск ячейки;

t С – время стирания предыдущей информации, если она может исказить записываемую;

t З – время записи данных в ячейку;

t Ч – время извлечения информации на ШД;

t Р – время регенерации данных (подзарядка конденсаторов в DRAM).

Быстродействие ЗУ измеряется в наносекундах (1нс = 10-9 с), микросекундах (1мкс = 10-6 с) или миллисекундах (1мс = 10-3 с).

Стоимость ЗУ (С ) чаще всего оценивается приведенной стоимостью (С П ), которая определяется из выражения:

С п = С / V (руб/бит).

Оперативные запоминающие устройства

Для построения ОЗУ большой емкости используются элементы статической или динамической памяти, которые строятся на простейших элементах транзисторно-транзисторной логики (ТТЛ), инжекционной логики (И2 Л), эмиттерносвязной логики (ЭСЛ) и других технологий .

В основе динамических ОЗУ (DRAM) используется заряд межэлектродных конденсаторов Cij емкостью менее 0.1 пФ и током заряда менее 10-10 А.

Статическая оперативная память (SRAM) строится на быстродействующих биполярных транзисторах, например, двухэмиттерных транзисторах TTL

В основе динамических ОЗУ (DRAM) используется заряд межэлектродных конденсаторов Cij емкостью менее 0.1 пФи током заряда менее 10-10 А.

Преимуществом динамических ОЗУ является высокая степень интеграции элементов памяти и малая потребляемая мощность. Недостатком их является большое время доступа 50-70 нс по сравнению со статической памятью, где оно равно менее 15 нс.

ВОПРОС 22

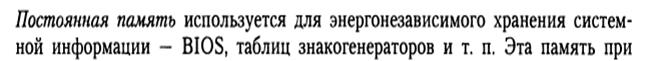

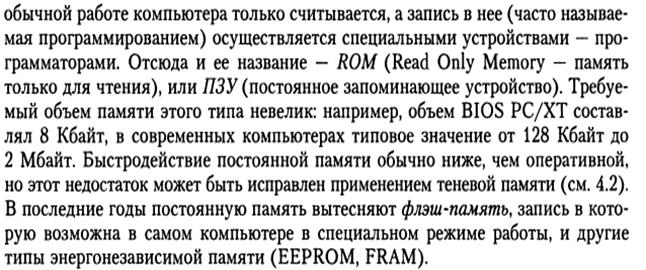

Постоянные и полупостоянные запоминающие устройства

Постоянные и полупостоянные ЗУ используются в ЭВМ как долговременная память для хранения констант, программ BIOS, POST, конфигурации ЭВМ и параметров устройств.

Среди главных достоинств можно назвать следующие:

- энергонезависимость, т.е. способность хранить информацию при выключенном питании (энергия расходуется только в момент записи данных);

- информация может храниться очень длительное время (десятки лет);

- сравнительно небольшие размеры;

- высокая надежность хранения данных, в том числе устойчивость к механическим нагрузкам;

- не содержит движущихся деталей (как в жестких дисках).

Основные недостатки флэш-памяти:

- невысокая скорость передачи данных (в сравнении с динамической оперативной памятью);

- незначительный объем (по сравнению с жесткими дисками);

- ограничение по количеству циклов перезаписи (хотя эта цифра в современных разработках очень высока – более миллиона циклов).

Флэш-память строится на однотранзисторных элементах памяти с "плавающим" затвором, что обеспечивает высокую плотность хранения информации. Существуют различные технологии построения базовых элементов флэш-памяти, разработанные ее основными производителями. Эти технологии отличаются количеством слоев, методами стирания и записи данных, а также структурной организацией, что отражается в их названии. Наиболее широко известны NOR и NAND типы флэш-памяти, запоминающие транзисторы в которых подключены к разрядным шинам, соответственно, параллельно и последовательно.

- Современные технологии производства флэш-памяти позволяют использовать ее для различных целей. Непосредственно в компьютере эту память применяют для хранения BIOS (базовой системы ввода-вывода), что позволяет, при необходимости, производить обновление последней, прямо на рабочей машине.

- Распространение получили, так называемые, USB-Flash накопители, эмулирующие работу внешних винчестеров. Эти устройства подключается, обычно, к шине USB и состоит из собственно флэш-памяти, эмулятора контроллера дисковода и контроллера шины USB. При включении его в систему (допускается "горячее" подключение и отключение) устройство с точки зрения пользователя ведет себя как обычный (съемный) жесткий диск. Конечно, производительность его меньше, чем у жесткого диска.

- Флэш-память нашла широкое применение в различных модификациях карт памяти, которые обычно используются в цифровых видео- и фотокамерах, плеерах, телефонах.

- Необходимо отметить, что надежность и быстродействие флэш-памяти постоянно увеличиваются. Теперь количество циклов записи/перезаписи выражается семизначной цифрой, что позволяет практически забыть о том, что когда-то на карту памяти можно было записывать информацию лишь ограниченное число раз. Современные USB-Flash накопители уже рассчитаны на шину USB 2.0 (и она им действительно необходима). На рынке появляется все больше пылевлагозащищенных устройств. При этом все большее и большее количество производителей встраивают кардридеры в настольные корпуса персональных компьютеров. Это безусловно свидетельствует о том, что данный тип памяти уже стал одним из популярнейших.

ВОПРОС 23

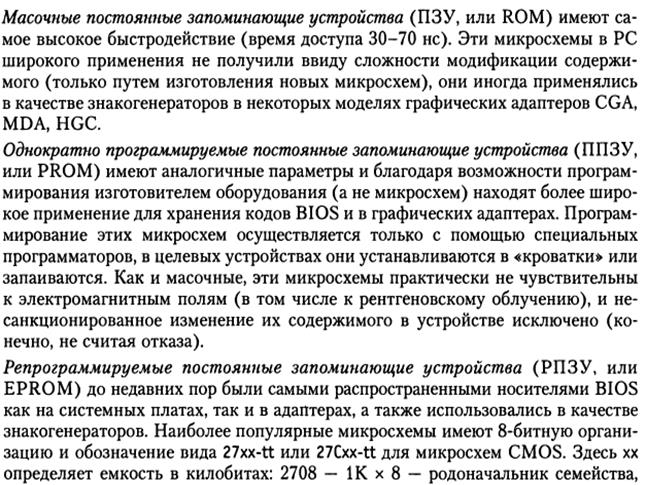

Гибкие диски используются как долговременная сменная память компьютера. Конструктивно диски представляют собой тонкие пластинки диаметром 5.25 и 3.5 дюйма, изготовленные из лавсана, покрытые оксидом железа или сплавом кобальта (высокая плотность). Некоторые пластинки по краю внутреннего отверстия имеют кольцо жесткости, повышающее устойчивость диска к деформации при зажиме их внутри дисковода. Для защиты от пыли и касаний предметов пластинки помещают в пластмассовый чехол. В чехле диска на 5.25 имеются отверстия (рис. 4.1) для зажима механизма вращения диска (1) с кольцом жесткости (5), для контакта с магнитными головками (2), для фиксации начала дорожки (маркер) (3), для запрещения/разрешения записи (4). В диске на 3.5 чехол твердый, отверстие доступа к диску закрывает металлическая задвижка, предохраняющая пластину от повреждений.

В рабочем режиме диск вращается электромотором с постоянной скоростью 300 или 360 (высокая плотность) оборотов в минуту. К отверстию в чехле (2) с двух сторон подводятся магнитные головки, которые последовательно осуществляют запись (считывание) информации на дорожки пластины.

При любом способе записи нумерация дорожек начинается с края и сверху пластины от нулевой до тридцать девятой или семьдесят девятой. Ширина дорожки зависит от радиальной плотности записи ТРI и составляет 0.33 мм при 360 Кб (ТРI=48 дорожек на дюйм и 40 дорожек на одну сторону) или 0.16 мм для дисков 1.2 Мб при TPI = 96 и высокой плотности записи. НГМД 3.5" емкостью 1.44 Мб имеют TPI = 135. Каждая дорожка разбивается на секторы. Секторы нумеруются по порядку 1, 2, 3... начиная с нулевой дорожки от маркера, в сторону противоположную вращению пластины (рис. 4.1). Программа FORMAT.COM размечает диск на необходимую плотность, число секторов и дорожек. Эта же программа контролирует исправность секторов и заносит характеристики форматирования диска в FAT в начальные секторы.

Накопители на магнитооптических дисках

Магнитооптические (МО) накопители являются одними из самых старейших представителей устройств со сменным носителем информации. Современные МО сочетают в себе большую емкость, высокую долговечность и надежность, возможность переносить данные, а также делать копии программ и операционных систем. Производителем и фактически монополистом на рынке МО накопителей является фирма Fujitsu.

Существуют 2 вида МО накопителей: 5.25 и 3.5 дюйма. МО диски 5.25 с двухсторонней записью изготавливаются емкостью 650 Мб, 1.3 Гб, 2.6 Гб и 4.6 Гб. МО диски односторонние 3.5 изготавливаются емкостью 128 Мб, 230 Мб, 540 Мб, 640 Мб и 1.3 Гб. Эти МО позволяют делать резервные копии не только с ПК, но и с небольших серверов. Наибольшее распространение получили современные МО накопители 3.5" емкостью 640 Мб и 1.3 Гб.

MO накопитель объединяет в себе магнитные и лазерные технологии. Во время процесса записи интенсивный лазерный луч фокусируется на диске, покрытом особым кристаллическим сплавом, который может сохранять магнитное поле. После нагревания сплава до критической температуры 145О С (точка Кюри) [14] кристаллы сплава становятся свободными и перемещаются под воздействием пишущей головки, которая изменяет намагниченность кристаллов сплава. Величина вертикальной намагниченности участка около 0.5 кв. микрона (участок намагничен – логическая "1") позволяет изменять направление поляризации (эффект Керра) или не изменять характеристики чтения отраженного маломощного лазерного луча (участок размагничен – логическая "0"). В процессе чтения/записи головки не соприкасаются с поверхностью носителя, что способствует надежности МО. К недостаткам МО накопителей следует отнести низкую скорость записи данных (из-за медленной скорости нагрева участков для записи), а также несовместимость с флоппи-дисководом.

Накопители на жестких магнитных дисках

Накопители на жестких магнитных дисках типа "винчестер" предназначены для долговременного хранения информации в составе компьютера. Название «винчестер» НЖМД получил в 1973 г., когда фирма IBM изготовила герметичный пакет из двух заменяемых дисков по 30 Мб каждый. Цифры 30 / 30 ассоциировались у пользователей с калибром популярной в США двустволки «Винчестер 30 / 30». В 1983 г. ЭВМ PC XT стали комплектоваться несъемными винчестерами емкостью 10 Мб со средним временем доступа 100 мс

Оптические накопители

В 1972 г. компания Phllips продемонстрировала систему Video Long Play. В ней был использован для записи данных принцип "засечек". Он стал началом развития CD-, а в дальнейшем и DVD-технологий. Первый стандарт оптических накопителей CD-ROM, включающий систему записи на компакт-диск произвольных цифровых данных, разработан в 1984 г. фирмами Philips и Sony.

Массово компакт-диск постоянной памяти СD-RОМ выпускается с 1988 г. как накопитель информации емкостью 650 Мб. Эта информация соответствует примерно 330 000 страницам текста или 74 минутам высококачественного звучания.

На данный момент существует несколько стандартов CD-ROM – это AAD, DDD, ADD. Буквы этой аббревиатуры отражают формы звукового сигнала, использованные при создании диска: первая – при исходной записи, вторая – при обработке и сведении, третья – конечный мастер-сигнал, с которого формируется диск. "A" обозначает аналоговую (Analog) форму, "D" – цифровую (Digital). Мастер-сигнал для CD всегда существует только в цифровой форме, поэтому третья буква аббревиатуры всегда "D". При записи и обработке сигнала в аналоговой форме сохраняются высшие гармоники, но возрастает уровень шума. При обработке в цифровой форме высшие гармоники принудительно обрезаются на половине частоты дискретизации.

Компакт - диски CD-ROM изготавливаются толщиной 1.2 мм с внешним диаметром 12 см, с внутренним отверстием 15 мм из полимерного материала, который покрыт с нижней стороны пленкой из сплава алюминия (рис. 4.7.).

Эта пленка является носителем информации, которая после записи защищается дополнительным слоем лака. Верхний слой является нерабочим, и на него наносятся этикетки и надписи.

. Перезаписываемые оптические накопители

Перезаписываемые диски CD-RW имеют семислойную структуру, отличающуюся от дисков CD-R, которые содержат пять слоев, как показано на рис. 4.9. В CD-RW используется промежуточный слой из металлопластика, изменяющий под воздействием луча свое фазовое состояние с аморфного на кристаллическое и обратно. В результате чего меняется прозрачность слоя. Фиксация изменений состояния происходит благодаря тому, что материал регистрирующего слоя при нагреве свыше критической температуры переходит в аморфное состояние и остается в нем после остывания, а при нагреве до температуры значительно ниже критической восстанавливает кристаллическое состояние. Такие диски выдерживают от тысяч до десятков тысяч циклов перезаписи. Однако их отражающая способность существенно ниже однократных CD, что затрудняет их считывание в обычных приводах. Для чтения CD-RW необходим привод с автоматической регулировкой усиления фотоприемника (Auto Gain Control), хотя некоторые обычные приводы CD-ROM и бытовые проигрыватели способны читать их наравне с обычными дисками. Способность привода читать CD-RW носит название Multiread.

ВОПРОС 25

Микропроцессор (МП) ‑ это программно-управляемое устройство обработки информации, выполненное в виде одной или нескольких БИС.

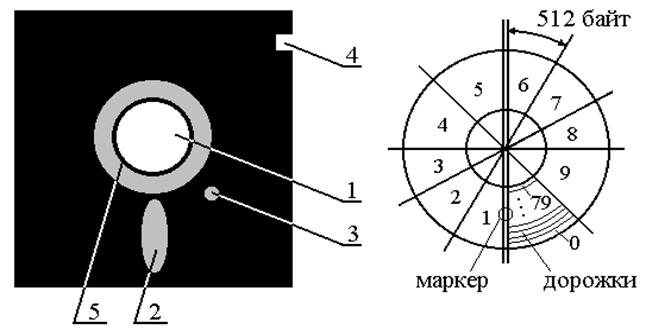

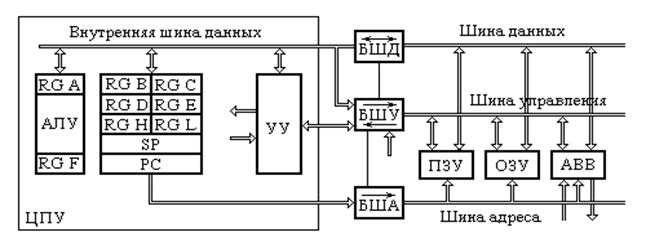

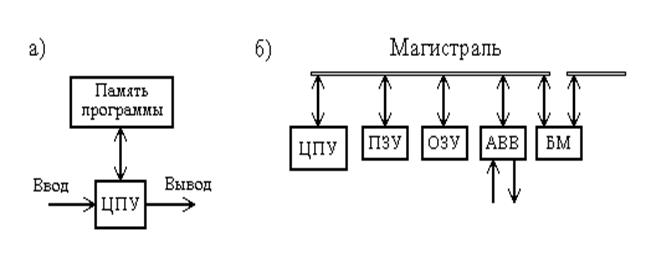

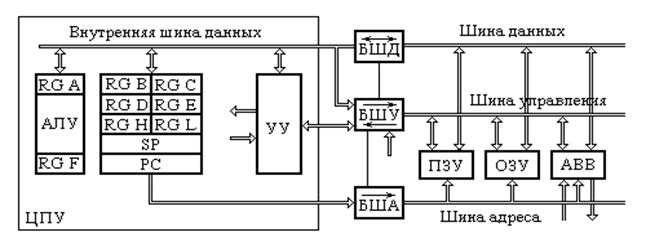

Запоминающее устройство, которое на рис. 1а было показано в виде одного блока, на рис. 1б представлено двумя блоками: постоянным запоминающим устройством (ПЗУ) и оперативным запоминающим устройством (ОЗУ). ПЗУ служит для хранения неизменяемой части программы и может работать только в режиме выдачи информации. ОЗУ используется для хранения промежуточных данных и может не только принимать на хранение, но и выдавать записанную ранее информацию. В микропроцессорной технике приняты термины “запись” и “чтение” информации. Процессы чтения и записи всегда сопровождают друг друга. Например, информация читается из ОЗУ и записывается в буферный регистр ЦПУ.

Шина данных в МП-системе ‑ двунаправленная. Информация по ней может передаваться как в ЦПУ, так и из ЦПУ. Направление передачи по ШД устанавливает ЦПУ.

Шина управления в рассматриваемой системе состоит из набора отдельных проводников, каждый из которых предназначен для передачи определенного сигнала в определенном направлении. МП 8080 выполнен в корпусе, имеющим 40 выводов. Это оказывается недостаточным для того, чтобы предоставить каждому сигналу управления отдельный вывод.

Поэтому часть сигналов управления передается по выводам шины данных в режиме разделения времени. Этим объясняется соединение на схеме рис. 2 буфера шины управления как с внутренним устройством управления (УУ), так и с шиной данных.

Разрядностью шины адреса (ША) определяется предельно возможный объем памяти, которой может быть укомплектована МП-система. Чем больше объем памяти, тем более сложные программы может реализовать система и тем мощнее ее вычислительные и управляющие возможности. МП типа 8080 имеют 16-разрядную адресную шину. Это означает, что ЦПУ может адресоваться к 216 = 65536 ячейкам памяти. Учитывая, что по каждому адресу может храниться 8-разрядное слово (1 байт), получаем, что предельный объем памяти составляет в данном случае 64 КБайт (1 Кбайт = 1024 байт). Шина адреса ‑ однонаправленная, код адреса из ЦПУ поступает на ПЗУ, ОЗУ и АВВ.

В состав МП входит арифметико-логическое устройство (АЛУ), способное выполнять простейшие арифметические и логические операции с одним или двумя кодовыми словами. Один из операндов (или единственный операнд), над которыми производится действие в АЛУ, как правило, хранится в регистре-аккумуляторе (RG A). В этот же регистр передается результат выполнения операции. В АЛУ имеются также регистры временного хранения операндов, которые на рис. 2 не показаны.

Непосредственно к АЛУ примыкает регистр флажков (RG F), в котором хранится информация (5 разрядов) о признаках, характеризующих результат, полученный в АЛУ после выполнения очередной операции. Эти признаки представлены следующими битами: битом переноса (С), битом дополнительного переноса (ас), битом знака (S), битом нулевого признака (Z), битом четности (P). Бит переноса устанавливается равным 1 при переносе из старшего разряда (переполнение разрядной сетки). Дополнительный перенос ‑ это перенос из младшего полубайта в старший. Информация об этом переносе нужна при переводе двоичных чисел в двоично-десятичные. Бит знака равен 1 тогда, когда в 7-м (старшем) разряде результата операции присутствует единица (отрицательные числа в ЦПУ представлены в дополнительном коде). Если Z = 1, то это означает, что получен нулевой результат. И, наконец, бит четности, равный единице, указывает на то, что в полученном результате содержится четное число кодовых единиц.

ВОПРОС 26

Микропроцессор (МП) ‑ это программно-управляемое устройство обработки информации, выполненное в виде одной или нескольких БИС.

Запоминающее устройство, которое на рис. 1а было показано в виде одного блока, на рис. 1б представлено двумя блоками: постоянным запоминающим устройством (ПЗУ) и оперативным запоминающим устройством (ОЗУ). ПЗУ служит для хранения неизменяемой части программы и может работать только в режиме выдачи информации. ОЗУ используется для хранения промежуточных данных и может не только принимать на хранение, но и выдавать записанную ранее информацию. В микропроцессорной технике приняты термины “запись” и “чтение” информации. Процессы чтения и записи всегда сопровождают друг друга. Например, информация читается из ОЗУ и записывается в буферный регистр ЦПУ.

Шина данных в МП-системе ‑ двунаправленная. Информация по ней может передаваться как в ЦПУ, так и из ЦПУ. Направление передачи по ШД устанавливает ЦПУ.

Шина управления в рассматриваемой системе состоит из набора отдельных проводников, каждый из которых предназначен для передачи определенного сигнала в определенном направлении. МП 8080 выполнен в корпусе, имеющим 40 выводов. Это оказывается недостаточным для того, чтобы предоставить каждому сигналу управления отдельный вывод.

Поэтому часть сигналов управления передается по выводам шины данных в режиме разделения времени. Этим объясняется соединение на схеме рис. 2 буфера шины управления как с внутренним устройством управления (УУ), так и с шиной данных.

Разрядностью шины адреса (ША) определяется предельно возможный объем памяти, которой может быть укомплектована МП-система. Чем больше объем памяти, тем более сложные программы может реализовать система и тем мощнее ее вычислительные и управляющие возможности. МП типа 8080 имеют 16-разрядную адресную шину. Это означает, что ЦПУ может адресоваться к 216 = 65536 ячейкам памяти. Учитывая, что по каждому адресу может храниться 8-разрядное слово (1 байт), получаем, что предельный объем памяти составляет в данном случае 64 КБайт (1 Кбайт = 1024 байт). Шина адреса ‑ однонаправленная, код адреса из ЦПУ поступает на ПЗУ, ОЗУ и АВВ.

Не все операции, выполняемые в АЛУ, воздействуют на содержание регистра флажков. Этот факт следует учитывать при программировании условных переходов по состоянию отдельных разрядов регистра F. Содержание регистра F дополняется до стандартного 8-разрядного размера тремя постоянными нулями.

Входящие в МП восьмиразрядные регистры общего назначения B, C, D, E, H, L играют роль сверхоперативного запоминающего устройства. Эти регистры могут использоваться отдельно и в виде 16-разрядных регистровых пар BC, DE, HL, называемых в командах по имени первых регистров B, D, H, содержащих старшие байты чисел.

Шестнадцатиразрядный регистр SP (stack pointer ) ‑это указатель стека, т.е. регистр, информация в котором указывает адрес очередной свободной ячейки стековой памяти. Стековая, или магазинная, память работает по принципу ”последний вошел, первый вышел”. Программист выделяет область ОЗУ, отводимую под стек, и помещает в регистр SP адрес последней ячейки этой области (в рассматриваемом МП стек заполняется с конца). Затем при необходимости по ходу выполнения программы на хранение в стек могут быть отправлены 16-разрядные кодовые слова из регистровых пар AF, BC, DE, HL . Каждое такое слово занимает две восьмиразрядные ячейки памяти с адресами (SP) и (SP) ‑ 1, где (SP) ‑ содержимое регистра SP.

Соответственно при помещении в стек очередного слова содержимое регистра SP автоматически уменьшается на 2. Затем при чтении каждого записанного в стек слова содержимое регистра SP увеличивается на 2. Операции со стеком удобны тем, что реализуются короткими однобайтными командами и программисту не нужно в командах указывать адреса ячеек памяти, куда записывается или откуда читается информация. Однако нужно учитывать, в каком порядке слова были направлены в стек, так как при чтении они будут выдаваться в обратном порядке.

Показанный на схеме рис. 2 16-разрядный регистр PC (programm counter ) ‑ это программный счетчик. Слово, записанное в регистре PC, выводится на 16-разрядную адресную шину и определяет, таким образом, адрес ячейки памяти, к которой в данный момент производится обращение. После выполнения каждой команды, за исключением команд переходов, число, записанное в PC, увеличивается на число единиц, равное числу байтов в коде этой команды. При выполнении команд переходов, содержимое PC может изменяться скачком.

Устройство управления УУ, входящее в состав МП (рис. 2), обеспечивает правильное функционирование всех внутренних узлов ЦПУ, выдает командные сигналы на внешнюю шину управления и воспринимает сигналы с этой шины.

Функциональные узлы ЦПУ соединены между собой внутренней шиной данных, с помощью которой они могут обмениваться информацией. Шины данных и адреса, выходящие из ЦПУ, могут быть переведены в высокоимпедансное состояние (внутренние буфера этих шин на рис. 2 не показаны).

ВОПРОС 37

LabVIEW — язык графического программирования, в котором для создания приложений используются графические образы (иконки) вместо традиционного текстового кода. От пользователя пакета не требуется знаний языков программирования, но понятие об алгоритме, цикле, выходе по условию ит.п. конечно иметь нужно. Все действия сводятся к простому построению структурной схемы приложения в интерактивной графической системе с набором всех необходимых библиотечных образов, из которых собираются объекты, называемые Виртуальными Инструментами (VI).

Процесс освоения LabVIEW существенно облегчается благодаря наличию интерактивной обучающей системы, разветвленной контекстнозависимой помощи и множества примеров использования приемов программирования (но все это на английском, немецком, .. и

LabVIEW Laboratory Virtual Instrument Engineering Workbench (Среда разработки лабораторных виртуальных приборов) представляет собой среду графического программирования, которая широко используется в промышленности, образовании

и научно-исследовательских лабораториях в качестве стандартного инструмента для сбора данных и управления приборами. LabVIEW - мощная и гибкая программная среда, применяемая для проведения измерений и анализа полученных данных.

С помощью графического языка программирования LabVIEW, именуемого G (Джей), вы можете программировать вашу задачу из графической блок-диаграммы, которая компилирует алгоритм в машинный код. Являясь превосходной программной средой для бесчисленных применений в области науки и техники, LabVIEW поможет вам решать задачи различного типа, затрачивая значительно меньше времени и усилий по сравнению с написанием традиционного программного кода.LabVIEW находит применение в самых разно образных сферах человеческой деятельности. В соответствии со своим названием он первоначально использовался в исследовательских лабораториях, да и в настоящее время является наиболее популярным программным пакетом как в лабораториях фундаментальной науки

Разработка приложений в среде LabVIEW отличается от работы в средах на основе С или Java одной очень важной особенностью. Если в традиционных алгоритмических языках программирование основано на вводе текстовых команд,

последовательно образующих программный код, в LabVIEW используется язык графического программирования, где алгоритм создается в графической иконной форме (pictorial form), образующей так называемую блок-диаграмму (blockdiagram),

что позволяет исключить множество синтаксических деталей. Применяя этот метод, вы можете сконцентрировать внимание лишь на программировании

потока данных; упрощенный синтаксис теперь не отвлекает вас от анализа самого алгоритма.

Программы LabVIEW называются виртуальными приборами (ВП, virtual instruments- VI), так как они функционально и внешне подобны реальным (традиционным) приборам. Однако они столь же подобны программам и функциям на

популярных языках программирования, таких как С или Basic. Здесь и далее мы

будем называть программы LabVIEW виртуальными приборами или ВП, причем

вне зависимости от того, соотносится их вид и поведение с реальными приборами или нет.

Виртуальный прибор состоит из трех основных частей:

• лицевая панель (Front Panel) представляет собой интерактивный пользовательский интерфейс виртуального прибора и названа так потому, что имитирует лицевую панель традиционного прибора. На ней могут находиться ручки управления, кнопки, графические индикаторы и другие элементы управления (controls), которые являются средствами ввода данных со стороны пользователя, и элементы индикации (indicators) -выходные данные из программы. Пользователь вводит данные, используя мышь и клавиатуру, а затем видит результаты действия программы на экране монитора;

• блок-диаграмма (Block Diagram) является исходным программным кодомВП, созданным на языке графического программирования LabVIEW, G (Джей). Блок-диаграмма представляет собой реально исполняемое

приложение. Компонентами блок-диаграммы являются: виртуальныеприборы более низкого уровня, встроенные функции LabVIEW, константы и структуры управления выполнением программы. Для того чтобызадать поток данных между определенными объектами или, что то же

самое, создать связь между ними, вы должны нарисовать соответствующие проводники (wires). Объекты на лицевой панели представлены на блок-диаграмме в виде соответствующих терминалов (terminals), через

которые данные могут поступать от пользователя в программу и обратно;

• для того чтобы использовать некоторый ВП в качестве подпрограммы (подприбора) в блок-диаграмме другого ВП, необходимо определить его иконку (icon) и соединительную панель (connector). Виртуальный прибор, который применяется внутри другого ВП, называется виртуальным

подприбором (ВИИ, SubVI), который аналогичен подпрограмме в традиционных алгоритмических языках. Иконка является однозначным графическим представлением ВП и может использоваться в качестве объекта на блок-диаграмме другого ВП. Соединительная панель представляет собой механизм передачи данных в ВП из другой блок-диаграммы, когда он применяется в качестве подприбора - ВПП. Подобно аргументам и параметрам подпрограммы, соединительная панель определяет входные и выходные данные виртуального прибора.

При помощи LabVIEW мы строим виртуальный инструмент вместо написания программы. При создании виртуального инструмента равное внимание уделяется внешней форме и внутреннему содержанию прибора. Соответственно, отдельно разрабатываются лицевая панель и функциональная схема ВП.

Лицевая панель - интерфейс, через который мы взаимодействуем с функциональной схемой (содержанием) прибора. Графические возможности LabVIEW позволяют создать на экране компьютера полную имитацию лицевой панели реального прибора с действующими переключателями, кнопками, индикаторами и т. д.

Построение функциональной схемы виртуального прибора идет путем рисования интуитивной блок-диаграммы, что является естественной формой записи для инженеров и научных работников. В среде LabVIEW эта блок-диаграмма становится настоящей действующей программой, так что вы избегаете сложной и длительной процедуры преобразования своих идей в программный код.

ВОПРОС 33

В связи с широким внедрением цифровых вычислительных средств, в первую очередь микропроцессоров и микро-ЭВМ, во все отрасли науки и техники стала актуальной задача связи ЭВМ с различными техническими устройствами. Как правило, информация первичных преобразователей (сигналов датчиков) представляется в аналоговой форме, в виде уровней напряжения. Большая часть исполнительных устройств (электродвигатели, электромагниты и т. д.), предназначенных для автоматического управления технологическими процессами, реагирует также на уровни напряжения (или тока). С другой стороны, цифровые ЭВМ принимают и выдают информацию в цифровом виде. Для преобразования информации из цифровой формы в аналоговую применяют цифро-аналоговые преобразователи (ЦАП), а для обратного преобразования аналого - цифровые преобразователи (АЦП).

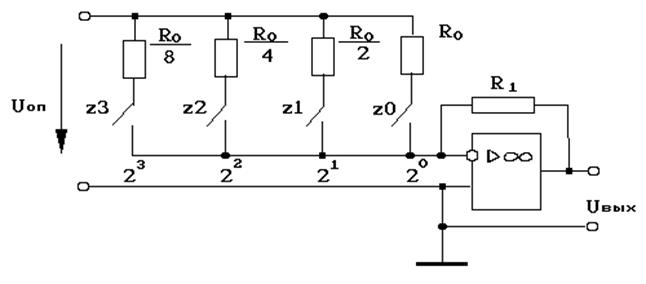

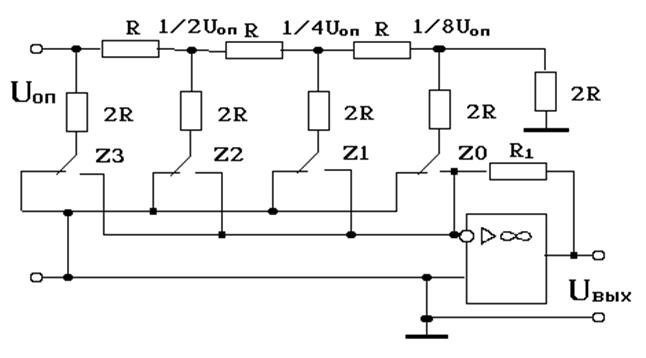

Цифро - аналоговые преобразователи вырабатывают напряжение или ток, функционально связанные с управляющим кодом. Причём функциональная связь в большинстве случаев линейна. Применяются ЦАПы в качестве узлов обратной связи АЦП и для формирования выходных аналоговых сигналов цифровых измерительных и вычислительных устройств. Для преобразования двоичного кода в аналоговый сигнал обычно формируют токи, пропорциональные весам разрядов кода, и затем суммируют те из токов, которые соответствуют не нулевым (единичным) разрядам входного кода. Принцип действия простейшего ЦАПа поясняет схема рис. 1.

Основу ЦАПа составляет матрица резисторов, подключаемых ко входу операционного усилителя ключами, которые управляются двоичным кодом (например, параллельным кодом регистра или счётчика). Коэффициенты передачи:

по входам 20 , 21 , 22 , 23 равны соответственно: , где - числа, принимающие значения 0 или 1 в зависимости от положения соответствующих ключей. Выходное напряжение ЦАПа определяется суммой. Таким образом, четырёхразрядный двоичный код преобразуется в уровень Uвых в диапазоне от 0 до , где - шаг квантования. Для уменьшения погрешности квантования необходимо увеличивать число двоичных разрядов ЦАПа. На рис. 2 приведено условное обозначение ЦАПа.

ЦАПы и АЦПы характеризуются погрешностью, быстродействием и динамическим диапазоном. Погрешность состоит из методической и инструментальной составляющих. Методическая составляющая определяется абсолютной погрешностью q квантования аналоговой величины по уровню: q = X–NDX, где N-числовое выражение величины X; DX-шаг квантования; Очевидно, |h| <=0,5DX. Таким образом, шаг квантования определяет методическую погрешность преобразования по уровню. Инструментальная погрешность определяется нестабильностью параметров элементов схемы преобразователя и неточностью его настройки. Быстродействие ЦАПа и АЦПа определяется временем преобразования: для ЦАПа интервалом между моментами поступления входного кода и установления выходного сигнала (с заданной точностью), для АЦПа интервалом от момента пуска преобразователя до момента получения кода на выходе. Динамический диапазон - допустимый диапазон изменения входного напряжения для АЦПа и выходного напряжения для ЦАПа.

ВОПРОС 34

В ней используют трёхпозиционные ключи, которые подсоединяют резисторы 2R либо ко входу суммирования операционного усилителя, либо к нулевой точке. При этом токи через резистор 2R не изменяются. Резисторы соединенные в матрицу типа R-2R, имеющую постоянное входное сопротивление со стороны источника Uоп, равное R независимо от положения ключей.

Коэффициент передачи напряжения между соседними узловыми точками матрицы равен 0,5. Для схемы рис. 3 входное напряжение ЦАПа определяется выражением .

Матрицы резисторов типа R-2R выпускаются в виде интегральных микросхем, например серии 301. Так матрицы 301НР5, 301НР6 имеют коэффициент деления от 1/2048 до 2047/2048 через 1/2048 с относительной погрешностью деления не более +0,01%

Помимо своего прямого назначения - преобразования цифрового кода в соответствующий ему уровень напряжения -ЦАП широко используется как генератор произвольных периодических функций. При этом простыми средствами удаётся сформировать достаточно сложные функции с высокой точностью. В качестве примера рассмотрим формирователь треугольного напряжения, схема которого приведена на рис. 5.

Этот генератор состоит из десятичного счётчика с дешифратором типа К176ИЕ8, резисторной матрицы и операционного усилителя. В каждый момент времени включен только один резистор матрицы; поэтому, задавая различные весовые коэффициенты, можно сформировать разнообразные функции. При изменении частоты входных тактов меняется частота выходных сигналов: . Таким же образом можно создать, например, и цифровой генератор синусоидальных колебаний. Для повышения точности аппроксимации желательно использовать четырёхразрядный счётчик с К=16. Входное напряжение должно изменяться в соответствии с выражением: , где x-число на выходе счётчика. Исходя из этого рассчитывают весовые коэффициенты резисторной матрицы.

ВОПРОС 35

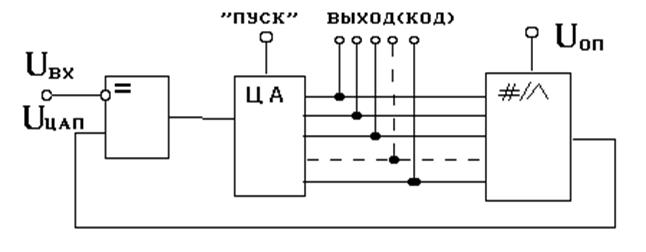

Аналого-цифровые преобразователи применяются в измерительных системах, измерительно-вычислительных комплексах для согласования аналоговых источников измерительных сигналов с цифровыми устройствами обработки и представления результатов измерения. Различным методам построения АЦПа соответствуют устройства, различающиеся по точности, быстродействию, помехозащищенности, сложности реализации. Аналого-цифровые преобразователи по способу преобразования подразделяют на последовательные, параллельные и последовательно-параллельные. В последовательных АЦПах преобразование аналоговой величины в цифровой код идёт ступеньками (шагами), последовательно приближаясь к измеряемому значению.

Если максимальное напряжение преобразуется в число X, то для его преобразования необходимо X шагов. Поэтому последовательные АЦПы являются самыми медленными, но и наиболее простыми по реализации. В параллельных АЦПах входное напряжение одновременно сравнивают с X опорными напряжениями. При этом результат получают за один шаг, но для этого необходимы большие аппаратные затраты (X компараторов).

Здесь цифровой автомат выполнен в виде: двоичного регистра Рг последовательного приближения, суммирующего импульсы тактового генератора ТГ; выходных буферных устройств 1, 2, 4, ..., 256, соответствующих двоичным разрядам счётчика; схемы готовности данных ГД, управляющей счётчиком и выдающей команду на считывание выходного кода. Термостабилизированный источник опорного напряжения ИОН вырабатывает напряжение Uоп для ЦАПа. Компаратор выполнен синхронизируемыми импульсами тактового генератора. Поступающие на вход регистра импульсы тактового генератора последовательно переводят разряды регистра в состояние 1 начиная со старшего, при этом остальные разряды находятся в состоянии 0. Если старший разряд находится в состоянии 1, ЦАП вырабатывает соответствующее напряжение, которое сравнивается в компараторе со входным. Если Uцап>Uвх, то по команде компаратора старший разряд регистра сбрасывается в нуль, если Uцап<Uвх, то в старшем разряде остаётся единица. Затем единица появляется в следующем по старшинству разряде регистра и снова происходит сравнение. Цикл повторяется пока не произойдет сравнение в младшем разряде (рис. 8).

ВОПРОС 29

Параллельный адаптер КР580ВВ55. Микросхема КР580ВВ55 программируемого периферийного параллельного адаптера (ППА) предназначена для применения в МП-системе в качестве универсального элемента ввода-вывода, обеспечивающего обмен данными в параллельном формате между МП и системными, в частности периферийными, устройствами. Аналогичное назначение, функции и структуру имеют микросхема К580ИК55 и зарубежный аналог ППА Intel 8255 [1, 2, 3].

Условное обозначение ППА и его программная модель показаны на рис. 1.Микросхема КР580ВВ55 размещена в 40-контактном корпусе и подключается к МП системе посредством двунаправленной трехстабильной 8-разрядной шины данных ШД(8), двухразрядной шины адреса ША(2) и 4-разрядной шины управления ШУ(4) с сигналами: ‑ запись, ‑ чтение, ‑ выборка микросхемы и СБР(RES) ‑ сброс.

Адаптер включает три программно-доступных 8-разрядных порта ввода-вывода (ПА, ПВ, ПС) и 8-разрядный регистр управляющего слова РУС, содержимое которого определяет направление передачи и функционального назначение 24 двунаправленных трехстабильных линий ввода-вывода, т. е. конфигурацию и режимы работы портов. Порты ПА и ПВ предназначены для обмена байтами данных с системными устройствами, а порт ПС, как правило, ‑ для обмена интерфейсными сигналами управления. Порт ПС в отличие от портов ПА и ПВ программно доступен при операциях записи данных не только как элементов в целом, но и поразрядно, т.е. с независимой адресацией каждого отдельного разряда ПСi (i = 0, 1,...,7), а в операциях выбора режима ‑ как два полупорта: старший ‑ ПСС, младший ‑ ПСМ или их части. Обмен данными между элементами ППА и МП происходит через внутреннюю шину, связанную с ШД и через устройство управления (УУ) с шинами ША(2) и ШУ(4).

Программирование ППА, или его настройка, осуществляется с помощью операции записи управляющего слова (УС) в регистр РУС. Возможны два типа настройки ППА.

1. Настройка разрядов ‑ поразрядное программирование состояний порта ПС: сброс в нуль или установка в единицу каждого адресуемого разряда ПСi , независимо от состояний других разрядов ПС. УС для этого типа программирования имеет вид (Д7 ...Д0 ) = (0---++++), где (Д7 ) = 0 определяет именно указанный тип настройки, значения разрядов (Д6 Д5 Д4 ) произвольны и могут быть доопределены любой двоичной комбинацией; разряды (Д3 Д2 Д1 ) задают двоичный адрес i разряда ПСi , а разряд Д0 ‑ вид операции: сброс разряда ПС, если (Д0 ) = 0, и его установку, если (Д0 ) = 1. В графе 19 табл. 1 приведены шестнадцатеричные значения УС, используемые в командах обращения к ППА. Так как значение старшей шестнадцатеричной цифры кода УС зависит от доопределения разрядов (Д6 Д5 Д4 ) {0,1,...,7}, то значение УС лежит в диапазоне чисел {00, 01,...,7F}. Заметим, что, хотя для настройки разрядов используется операция записи УС, содержимое регистра РУС при этом не изменяется (фиктивная запись). Для изменения состояния нескольких разрядов или формирования временной диаграммы на выходе определенного разряда ПС необходимо загружать в ППА соответствующую временную последовательность УС. Данный тип настройки позволяет использовать порт ПС в качестве регистра состояния периферийного устройства при организации программно - управляемого обмена данными.

2. Настройка режимов ‑ программирование портов ПА, ПВ и ПС на один из трех возможных режимов или их комбинацию: 0 ‑ режим простого однонаправленного обмена; 1 ‑ режим стробируемого однонаправленного обмена; 2 ‑ режим стробируемого двунаправленного обмена. Для настройки режимов используются УС, в которых разряд (Д7 ) = 1 (в этом случае УС действительно записывается в регистр РУС). Пара разрядов УС (Д6 Д5 ) определяет выбор режима для порта ПА: (00) ‑ режим 0; (01) ‑ режим 1 и (1-) ‑ режим 2; разряды Д4 и Д3 определяют соответственно для портов ПА и ПСС направления линий: если бит равен 1, линии имеют направление на ввод; если бит равен 0, ‑ на вывод. Аналогично для порта ПВ разряд Д2 задает режим 0, если (Д2 ) = 0, и режим 1, если (Д2 ) = 1, а разряды Д1 и Д0 определяют соответственно для портов ПВ и ПСМ направления линий. В режиме 0 порты ПА, ПВ и полупорты ПСС, ПСМ могут быть настроены на любую из 16 возможных конфигураций однонаправленного ввода или вывода (табл. 1) [1].

Обмен данными организуется по командам ввода-вывода МП синхронным или асинхронным способами.

Режим 0 (простой ввод/вывод)

Работа в этом режиме позволяет организовать простой ввод или вывод для каждого из трех каналов. Данные просто записываются или считываются из выбранного канала. Таким образом, основные особенности функционирования микросхемы в режиме 0 следующие:

два 8-битовых канала (каналы A и B) и два 4-битовых канала (старшая и младшая половинки канала C);

каждый канал может быть независимо от других запрограммирован на ввод или вывод; таким образом, всего может быть 16 различных комбинаций ввода/вывода;

выходы имеют память, входы работают без буферной памяти.

Режим 1 (тактируемый ввод/вывод)

Этот режим служит для однонаправленного обмена данными по выбранному каналу с периферийным устройством. Для управления передачей или приемом по каналу A используется младшая тетрада канала C, канал B управляется старшей тетрадой канала C.

Основные особенности работы в данном режиме:

два канала (каналы A и B);

каждый канал может быть запрограммирован на вход или выход;

одна тетрада канала C используется для управления одного канала передачи данных

Режим 2 (двунаправленный тактируемый ввод/вывод)

В этом режиме возможен обмен данными по 8-битовой двунаправленной шине данных. Управление обменом данными, а также направление передачи задается с помощью управляющих сигналов аналогичным режиму 1 способом. Возможно также генерирование сигналов прерываний и запрета разрешения.

Основные особенности работы в данном режиме:

возможно использование только канала A;

управление обменом обеспечивается 5 битами канала C;

входы и выходы обладают буферной памятью.

ВОПРОС 30

Параллельный интерфейс

В PC используется интерфейс Centronics.

Первоначальное применение –для

подключения «построчных принтеров»

LinePrinTer(LPT).

Базовый вариант –стандартный порт

принтера (SPP)

IEEE 1284–стандарт параллельного интерфейса (1994 г.)

•SPP–стандартный режим

•Полубайтный режим (Nibble Mode) –ввод байта в 2 цикла с использованием линий состояния (доступен на любом адаптере)

•Байтовый режим –с использованием для приема линий данных (адаптер должен допускать двунаправленный обмен по этим линиям)

•EPP (Enhanced Parallel Port)–двунаправленный обмен с аппаратной генерацией управляющих сигналов (внешняя память, локальные сети)

•ECP (ExtendedCapabilityPort) –двунаправленный обмен с аппаратным сжатием по RLE, поддержкой FIFO и DMA(принтеры, сканеры)