| Скачать .docx |

Курсовая работа: Разработка однофазного мостового выпрямителя

СОДЕРЖАНИЕ

1. Введение

2. Составление логической модели диагностирования управляемого однофазного мостового выпрямителя

2. Структурный синтез контроллера

3. Разработка электрической принципиальной схемы контроллера

3.1 Разработка блока сбора информации

3.2 Разработка блока связи с исполнительными устройствами

3.3 Разработка блока контроля исправности состояния процессора и управляющей программы (watchdog timer - WDT)

3.4 Разработка блока индикации входных и выходных сигналов

4. Разработка программного обеспечения

5. Список литературы

1. Введение

В рамках настоящего курсового проекта была рассчитана математическая модель диагностирования силовой части однофазного мостового тиристорного преобразователя, а так же разработана схема защиты этого ТП от нестандартных ситуаций и отлажено сопутствующее программное обеспечение.

Программируемая логика реализована на микропроцессоре МК-51 фирмы ATMEL, который, благодаря встроенной FLASH памяти, обладает возможностью электрического перепрограммирования ПЗУ и быстрой смены управляющей программы.

В связи с применением в схеме защиты микропроцессора достигнута большая гибкость и модернизируемость данной системы. С минимальными переделками она может быть применена к любому силовому ТП, настроена на любые критические ситуации, а так же позволяет добавлять в себя различные сервисные функции.

2. Составление логической модели диагностирования управляемого однофазного мостового выпрямителя

Рассмотрим построение математической модели тиристора, как дискретного элемента с памятью. Сформулируем общие условия работы тиристора:

1) Включение тиристора происходит только при наличии положительного по отношению к катоду потенциала на аноде тиристора и отпирающего импульса (необходимого уровня и длительности).

2) Выключение тиристора происходит при уменьшении тока через тиристор до значения меньше тока удержания.

Представим функциональную модель тиристора, как дискретного элемента с памятью. Имеющей два внешних входа Х1 ,Х2 , внешний выход Z1 , вход памяти w1 и внутреннюю переменную Y1 .

Этим переменным соответствуют:

Х1 =1 напряжение на аноде тиристора положительное по отношению к катоду.

Х1 =0 напряжение на аноде тиристора отрицательное по отношению к катоду.

Х2 =1 на управляющем электроде есть отпирающий импульс заданного уровня и длительности.

Х2 =0 на управляющем электроде нет отпирающего импульса.

Z1 =1 ток протекающий через тиристор больше тока удержания.

Z1 =0 ток протекающий через тиристор меньше тока удержания.

W1 -функция возбуждения принятая равной току тиристора.

Y1 =1 проводимость перехода анод-катод равна ¥.

Y1 =0 проводимость перехода анод-катод равна нулю.

Пользуясь моделью тиристора и общими условиями его работы составим таблицу истинности тиристора:

| X1 |

X2 |

Y1, n |

Y1, n +1 |

Z1 |

| 0 |

0 |

0 |

0 |

0 |

| 0 |

0 |

1 |

0 |

0 |

| 0 |

1 |

0 |

0 |

0 |

| 0 |

1 |

1 |

0 |

0 |

| 1 |

0 |

0 |

0 |

0 |

| 1 |

0 |

1 |

1 |

1 |

| 1 |

1 |

0 |

1 |

1 |

| 1 |

1 |

1 |

1 |

1 |

От таблицы истинности тиристора перейдем к математической формуле в виде булевых функций. Выходная функция Z1 будет иметь следующую дизъюнктивную нормальную форму:

![]()

![]() Z1

=X1

X2

Y1,

n

Ú X1

X2

Y1,

n

Ú X1

X2

Y1,

n

= X1

(X2

ÚY1,

n

)

Z1

=X1

X2

Y1,

n

Ú X1

X2

Y1,

n

Ú X1

X2

Y1,

n

= X1

(X2

ÚY1,

n

)

В соответствии с этим выражением составим диаграмму перехода тиристора:

Рассмотрим силовую часть управляемого выпрямителя со средней точкой при работе на последовательно включенные активно-индуктивную и противо-ЭДС двигателя М нагрузки:

Х1 =1 – характеризует положительный потенциал на аноде тиристора в течение интервалов времени на которых U2m sinwt>∆UV

Х1 =0 – характеризует отрицательный потенциал на аноде тиристора в течение интервалов времени на которых U2m sinwt<∆UV

Х2 =1 – характеризует ток Iу амплитудой и длительностью, обеспечивающих к моменту окончания Iу достижение прямого анодного тока тиристора IV >Iуд .

Х2 =0 – характеризует отсутствие тока Iу .

Z1 =1 – характеризует прямой ток IV >Iуд , протекающий через тиристор.

![]()

Z1 =0 – характеризует ток IV <Iуд , протекающий через тиристор.

Z2 =1 – характеризует падение напряжения UR на активном сопротивлении Rн нагрузки ТП при протекании тока IV .

Z2 =0 – соответствует отсутствию падения напряжения UR на активном сопротивлении Rн нагрузки ТП.

Z3 =1 –характеризует ЭДС самоиндукции в индуктивности Lн при изменении тока Iн в нагрузке ТП в интервалах времени когда

EL = -Lн dIv /dt <0.

Z3 =0 –характеризует ЭДС самоиндукции в индуктивности Lн при изменении тока Iн в нагрузке ТП в интервалах времени когда

EL = -Lн dIv /dt >0.

Z4 =1 – характеризует противо-ЭДС двигателя при условии Ед ≠0.

Z4 =0 – характеризует отсутствие противо-ЭДС двигателя т.е. Ед =0.

Z5 =1 – характеризует результирующее напряжение Uн на выходе ТП при условии:

Uн = Iн Rн + Lн dIv /dt +Eд ≠0.

Z5 =0 – характеризует отсутствие напряжения Uн на выходе ТП т.е. при Uн =0.

Х3 =1 – характеризует активное сопротивление Rн нагрузки если соблюдается условие:

![]()

Х3 =0 – характеризует активное сопротивление Rн нагрузки если это условие не соблюдается.

Х4 =1 – характеризует индуктивность цепи нагрузки ТП при Lн ≠0.

Х4 =0 – характеризует индуктивность цепи нагрузки ТП при Lн =0.

Х5 =1 – характеризует изменение тока нагрузки Iн во времени если dIн /dt<0.

Х5 =1 – характеризует изменение тока нагрузки Iн во времени если dIн /dt> 0.

Х6 =1 – характеризует положительный потенциал на анодах тиристоров при условии:

U2m sin(wt+ν) - Eд >∆UV

Х6 =0 – характеризует отрицательный потенциал на анодах тиристоров при условии:

U2m sin(wt+ν) - Eд <∆UV

Хк =1 – характеризует коммутационный процесс токов в тиристорах ТП если имеет место коммутация с одного тиристора на другой.

Хк =0 – характеризует коммутационный процесс токов в тиристорах ТП если отсутствует коммутация тока в тиристорах.

Поскольку ток нагрузки ТП равен сумме токов Iv1 = Iv2 и Iv3 = Iv4 тиристоров V1, V2, V3, V4, указанное событие отражено в логической сети введением логического суммирования сигналов Z01, Z02, равных:

Z01 = z11/\Z12; Z02 = Z13/\z14

и характеризующих токи, последовательно протекающие через соответствующие тиристоры V1, V2 и V3, V4. Так как тиристоры могут открываться лишь при одновременной подаче управляющих импульсов тока Iy1, Iy2 для тиристоров V1, V2 и импульсов тока Iy3, Iy4 для тиристоров V3, V4 это событие отражено в логической сети введением логического произведения сигналов X21, X22 и X23, X24. Коммутационный процесс в ТП характеризуется введением в логическую сеть сигнала Xк=1.

Математические выражения алгебры логики, характеризующие режим работы однофазной мостовой схемы ТП, могут быть представлены как:

Z5 ={[(Z11 ÙZ12 ) Ú (Z13 ÙZ14 )] Ù X3 Ú (X4 ÙX5 ) ÚZ4 }ÙXк

Z11, n +1 =[(X21 ÙX22 ) Ú Z11 n ] Ù [(X1 ÙX6 ) Ú (X4 ÙX5 )Ú ( Z11, n Ù Z13, n ÙXK )]

Z12, n +1 =[(X21 ÙX22 ) Ú Z12 n ] Ù [(X1 ÙX6 ) Ú (X4 ÙX5 )Ú ( Z12, n Ù Z14, n ÙXK )]

Z13 n +1 =[(X23 ÙX24 ) Ú Z13 n ] Ù [(X1 ÙX6 ) Ú (X4 ÙX5 )Ú ( Z11, n Ù Z13, n ÙXK )]

Z14 n +1 =[(X23 ÙX24 ) Ú Z14 n ] Ù [(X1 ÙX6 ) Ú (X4 ÙX5 )Ú ( Z12, n Ù Z14, n ÙXK )]

Построение алгоритма диагностирования

Задача построения алгоритма диагностирования дискретного последовательного объекта заключается в том, чтобы, не прибегая к разрыву обратных связей в объекте, построить такую последовательность входных наборов, при которых ответные последовательности выходных наборов объекта позволяют выделить возможные в нем дефекты. При этом предполагается, что, хотя исходные состояния элементов памяти объекта и неизвестны, всегда найдется последовательность входных наборов фиксированной длины, позволяющая перевести исправный объект в любое достижимое состояние. Для реальных объектов указанное требование вполне естественно и реализуемо.

В связи с тем, что диагностирование сразу всей логической схемы однофазного мостового ТП представляет определенную сложность, из-за большого количества элементов, то было принято решение о диагностировании системы по частям, диагностируя каждый тиристор отдельно, для чего в схему диагностирования введены переключатели, позволяющие переводить ее в режим тестирования, аналогичный схеме однофазного однополупериодного преобразователя.

Построим алгоритм диагностирования силовой части ТП при работе на двигатель постоянного тока. В соответствии с логической моделью рассматриваемого объекта и логическими соотношениями для нее выходные сигналы Z1, n и Z5, n в текущем такте времени

Z1, n =(Z1, n -1 ÚX2 ) Ù[(X1 ÙX6 ) Ú (X4 ÙX5 )];

Z5, n =(Z1, n -1 ÚX2 ) Ù[(X1 ÙX6 ) Ú (X4 ÙX5 )] Ù X3 Ú [(X4 ÙX5 ) Ú Z4 ]

где Z1, n-1 – выходной сигнал объекта в предыдущем такте времени.

Для определения входных наборов, различающих исправное и неисправное состояние объекта, представим вышестоящее выражение в эквивалентной нормальной форме, т.е. как логическую сумму логических произведений букв.

Z5, n =(X1 Ù X2 Ù X3 Ù X6 ) Ú (X1 Ù X3 Ù X6 Ù Z1, n -1 ) Ú (X4 Ù X5 ) Ú Z4

В общем случае для логических схем с разветвлениями каждая буква терма (произведения букв) соответствует входному сигналу или его инверсии с индексом, который обычно составляется из номеров логических элементов схемы, встречающихся на пути, соединяющем данную переменную с выходом схемы.

Задача поиска какого-либо неисправного элемента здесь не ставится. Логичнее дефекты в силовой части ТП отражать в форме допустимости или недопустимости входных или выходных сигналов модели.

В общем виде букву ЭНФ обозначают символом qi и придают ему значения qi=0 или qi=1 в зависимости от того, какого типа дефект проверяется (0 или 1). При этом:

-для проверки qi на дефект типа достаточно принять все буквы хотя бы одного терма в ЭНФ, содержащего qi равным 1 и в каждый из остальных термов – хотя бы одну букву принять равной 0.

-для проверки qi на дефект 1 достаточно хотя бы в одном терме, содержащем qi принять qi равной 0, а значение остальных букв этого терма – равным 1, при этом в каждом из остальных термов принять хотя бы одну букву равной 0.

Проведем проверку букв на qi=0.

| Z5, n = (X1 Ù X2 Ù X3 Ù X6 ) Ú (X1 Ù X3 Ù X6 Ù Z1, n -1 )Ú(X4 Ù X5 ) Ú Z4 |

|||||||||||

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

| 2 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

| 3 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

| 4 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Выполним проверку букв на qi=1

| Z5, n = (X1 Ù X2 Ù X3 Ù X6 ) Ú (X1 Ù X3 Ù X6 Ù Z1, n -1 )Ú(X4 Ù X5 ) Ú Z4 |

|||||||||||

| 5 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

| 6 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

| 7 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

| 8 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

После проведенных выше проверок получена нижеследующая таблица, где ни одна из букв ЭНФ не осталась не проверенной. В таблице отмечены наборы возможных сигналов и проверяемые сигналы для каждого из наборов. Очевидно, что изменение значения проверяемого сигнала с 1(0) на 0(1) должно вызвать изменение Z5, n

Таблица входных наборов и проверяемых сигналов силовой части однофазного ТП.

| № |

Входные сигналы |

Z5, n |

Проверяемые сигналы |

qi |

||||||||||||||

| x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

z4 |

x1,v-1 |

x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

z4 |

x1,v-1 |

|||

| 1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

| 2 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

| 3 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

| 4 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

| 5 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

| 6 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

| 7 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

| 8 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

Полученные в этой таблице совокупности наборов различают исправное и неисправное технические состояния рассматриваемого объекта диагностирования и являются основой для построения таблиц покрытий и функций неисправности.

При составлении таблицы покрытий должно соблюдаться условие, при котором предыдущее значение выходного сигнала объекта или элемента памяти, входящее в рассматриваемый набор, должно совпадать с текущим значением выходного сигнала объекта или элемента памяти при предыдущем наборе. Для обеспечения этого условия из имеющейся в таблице совокупности наборов первым устанавливающим набором можно принять набор под номером 5, при котором выход элемента памяти объекта (тиристора) устанавливается равным нулю (Z5, n = 0).

Для силовой части ТП данный набор соответствует отрицательной по отношению к аноду тиристора полярности напряжения, при котором тиристор запирается.

Порядок отдельных наборов зависит от значения выходных сигналов объекта и элемента памяти. В нижеследующей таблице представлены последовательности наборов входных сигналов ТП, для которых предыдущие и текущие значения выходных сигналов элемента памяти и объекта диагностирования соответствуют приведенному выше условию.

Последовательность входных наборов и покрытий силовой части ТП

| № |

Входные сигналы |

Z5, n |

|||||||

| x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

z4 |

Z1, n -1 |

||

| 5 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

| 6 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

| 1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

| 2 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

| 8 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

| 3 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

| 1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

| 7 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

| 5 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

| 4 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

| № |

Неисправности |

||||||||

| е1 |

е2 |

е3 |

е4 |

е5 |

е6 |

е7 |

|||

| 5 |

|||||||||

| 6 |

|||||||||

| 1 |

+ |

+ |

|||||||

| 2 |

+ |

+ |

+ |

+ |

|||||

| 8 |

+ |

+ |

|||||||

| 3 |

|||||||||

| 1 |

+ |

||||||||

| 7 |

+ |

+ |

|||||||

| 5 |

|||||||||

| 4 |

|||||||||

е1 – соответствует разрыву цепи управляющего перехода тиристора, т.е. х2=0;

е2 – соответствует постоянному поступлению управляющего импульса тиристора, т.е. х2=1;

е3 – соответствует исчезновению питающего силового напряжения трансформатора ТП, т.е. х1=0;

е4 – соответствует разрыву силовой цепи ТП на стороне его нагрузки, т.е. х3=0;

е5 – соответствует замене индуктивной нагрузки на ТП на активную, т.е. х4=0;

е6 – соответствует изменению нагрузки на активно-индуктивную нагрузку, т.е. z4=0;

е7 – соответствует короткому замыканию тиристора ТП, т.е. Z1, n-1 = 1;

В приведенной таблице можно заметить неразличимые неисправности е3 и е4. Ряд входных наборов, не выделяющих заданный класс неисправностей можно исключить из рассмотрения. Например наборы 5, 7, 8. Исходя из этого таблица будет иметь следующий вид.

Таблица функций неисправностей силовой части ТП.

| № |

Входные сигналы |

Z5, n |

|||||||

| x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

z4 |

|||

| 6 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

| 1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

|

| 2 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

| 3 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

| 4 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

| № |

Неисправности |

||||||||

| е1 |

е2 |

е3,e4 |

е5 |

е6 |

е7 |

||||

| 6 |

0 |

1 |

0 |

0 |

0 |

1 |

|||

| 1 |

0 |

1 |

0 |

1 |

1 |

0 |

|||

| 2 |

1 |

1 |

0 |

1 |

1 |

1 |

|||

| 3 |

1 |

1 |

1 |

0 |

1 |

1 |

|||

| 4 |

1 |

1 |

1 |

1 |

0 |

1 |

|||

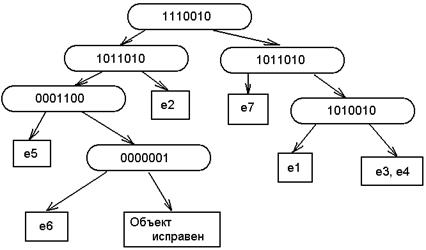

По данной таблице представляем алгоритм диагностирования ТП. Первым имитируется на входе ТП набор сигналов управления, соответствующий набору №1. При положительном результате проверки, когда при подаче данного набора происходит изменение выходного сигнала Z5, n ТП, неисправности ТП следует искать среди технических состояний е2, е5, е6. При отрицательном результате – среди технических состояний е1, е3, е4, е7.

Второй проверкой технического состояния ТП вне зависимости от результатов первой проверки целесообразно выбрать входной набор сигналов под номером 6. При положительных результатах первой и второй проверок будет однозначно выделена неисправность, соответствующая техническому состоянию е2. При положительном результате второй проверки и отрицательном результате первой выделяется неисправность для технического состояния е7. Следующие этапы проверок включают в себя наборы входных сигналов под номерами 2 и 3 (в соответствии с предыдущими результатами проверок). Итогом применения перечисленных в алгоритме диагностирования наборов входных сигналов ТП является выделение принятых неисправностей (за исключением неисправностей для технических состояний е3, е4).

2. Структурный синтез контроллера

Проанализировав задание курсового проекта, я пришел к выводу, о целесообразности его изготовления на базе микропроцессора.

Контроллер должен опрашивать состояние датчика тока, температуры и др. и, обработав полученную информацию, выдавать сигналы для системы управления, выполнять аварийную остановку привода, а так же выводить на индикаторы информацию о текущем состоянии системы защиты.

Таким образом, в структуру контроллера входят:

1) Управляющий блок (микропроцессор).

2) Блок сбора информации и преобразования ее в вид, пригодный для обработки микропроцессором.

3) Блок связи с исполнительными устройствами, для преобразования выходных сигналов микропроцессора в сигналы управления.

4) Блок контроля исправности состояния процессора и управляющей программы (watchdog timer).

5) Блок индикации входных и выходных сигналов.

В связи с микропроцессорной реализацией контроллера было принято решение использовать современную электронную элементную базу таких известных фирм, как Atmel, Burr-Brown, National Semiconductor, Analog Devices, Bournc и др.

Вся применяемая оптоэлектроника российского производства.

В качестве основы для нашего контроллера был выбран микропроцессор семейства MK-51 от фирмы Atmel – AT89C2051.

Его некоторые особенности — Features:

• Compatible with MCS-51™ Products (Совместимость с семейством МК-51)

• 2K Bytes of In-System Reprogrammable Flash Memory (2 кб встроенной перепрограммируемой Flash памяти)

– Endurance: 1,000 Write/Erase Cycles — (гарантируется 1000 циклов перезаписи)

• Fully Static Operation: 0 Hz to 24 MHz (возможность работы на частотах от 0 до 24 МГц)

• 128 x 8-Bit Internal RAM (128 б ОЗУ)

• 15 Programmable I/O Lines (15 программируемых портов ввода/вывода)

• Two 16-Bit Timer/Counters (Два 16-битных таймера счетчика)

• Six Interrupt Sources (Шесть источников прерываний)

• Programmable Serial Channel (Программируемый последовательный канал)

3. Разработка электрической принципиальной схемы контроллера

3.1 Разработка блока сбора информации

Контроллер должен принимать информацию от термодатчика(терморезистор), датчика скорости(тахогенератор), а также получать информацию о величине тока в нагрузке ТП от датчика тока.

В качестве датчика тока выберем датчик LTS25NP

Uп =5В

IPN =8A

Uout =2.5B

Из передаточной характеристики

определим напряжение на выходе датчика тока при котором будет срабатывать защита:

Исходя из нагрузочной способности тиристоров в ТП выберем максимально допустимый ток в цепи нагрузки Iн =2A

Напряжение на выходе датчика тока будет равно:

U=2.5+(3.125-2.5)·2/8=2.66B

Т.к. в выбранном микропроцессоре нет встроенного АЦП, то для преобразования аналогового сигнала в дискретные величины был применен счетверенный компаратор LM2900.

В связи с конструктивной особенностью датчика тока не требуется дополнительная гальваническая развязка его выходного информационного тока.

На неинвертирующий вход компаратора подается измеряемая величина напряжения, а на инвертирующий – расчетная величина опорного напряжения, при достижении которой значение логического сигнала на выходе компаратора меняется на противоположное.

Для организации высокостабильного опорного напряжения выбрана специализированная микросхема LM4130 фирмы National Semiconductor.

Ее основные характеристики:

Features

- Small SOT23-5 package

- High output voltage accuracy 0.05%

- Low Temperature Coefficient 10 ppm/°C

- Stable with capacitive loads to 100µF

- Full accuracy 40°C to 85°C

- Excellent load and line regulation

- Output current 30 - 60 mA

- Output impedance < 1

- Voltage options: 4.096V

По рекомендации производителя Сin=47 мкФ; Сout=0.1 мкФ.

С выхода данной микросхемы напряжение делится до требуемых значений высокоточными резисторами фирмы Bournc.

Для заданного значения тока:

2А – 2.66В – R1=402 Ом R2=100 Ом;

Для контроля температуры выберем датчик, представляющий из себя терморезистор с понижением сопротивления при нагреве.

При достижении температуры двигателя выше допустимой, сопротивление терморезистора уменьшается настолько, что компаратор переключается и на вход микропроцессора подается сигнал логической "1".

Защита от превышения максимальной скорости выполнена на базе датчика скорости – тахогенератора. С увеличением частоты вращения двигателя постоянное напряжение на тахогенераторе пропорционально растет, пропорционально уменьшаясь на делителе перед компаратором. При достижения заданной пороговой величины происходит переключение выхода компаратора.

3.2 Разработка блока связи с исполнительными устройствами

Для организации возможности аварийного отключения напряжения, подаваемого на вход ТП необходимы специальные развязывающие элементы.

В связи с этим было выбрано твердотельные реле постоянного тока, подходящее по мощности.

Выберем оптореле 5П19А1

Реле средней мощности общего назначения.

Iком =-3…+3А

Iком и =-8…+8А

Uком =400В

Р=1Вт

Т= -45…+85С

Определим величину сопротивления резистора R7:

Зададимся током через опто-реле, для нормального токового согласования с портом микропроцессора Iвх =10мА

R7=(5- Uкэнас )/10·10-3 =(5- 0.4)/10·10-3 =410Ом

Примем сопротивление резистора R7 (C2-11) равным:

R=430Ом

3.3 Разработка блока контроля исправности состояния процессора и управляющей программы (watchdog timer - WDT)

Системы, построенные на базе микропроцессоров, могут иметь специфические отказы или сбои в работе.

Например, из-за близкой сильной электромагнитной помехи может исказиться часть информации, обрабатываемой микропроцессором в данный момент, что чревато сбоем в алгоритме управляющей программы, а так же зацикливанием работы процессора или его "зависанием". Все это приводит к отказу в работе контроллера.

Как правило, такие сильные и фатальные помехи случаются очень редко, но если контроллер выполняет часть операций в отлаженном техническом процессе, то такой его отказ приводит к возникновению незапланированного простоя в работе и большими экономическими убытками.

Работоспособность контроллера можно восстановить, подав на процессор команду сброса (reset).

Но так как в реальном производственном процессе таких управляющих контроллеров может быть очень много, а по теории надежности известно, что чем больше элементов в системе, тем меньше общая надежность системы, то вероятность проявления таких отказов в целом на производстве достаточно высока. Каждый раз искать место очередного сбоя и вручную подавать команду сброса получается экономически невыгодно.

Поэтому для таких случаев и придумали схему watchdog ("сторожевая собака" досл.) таймера (WDT).

Эта схема автоматически посылает на процессор команду сброса при его зависании.

При работе этот таймер отсчитывает определенный промежуток времени, после которого выдается команда на сброс микропроцессора. Но и у самого таймера есть вход, для подачи сигнала сброса, на который поступают сигналы от микропроцессора.

Таким образом микропроцессор и watchdog таймер "соревнуются", кто кого раньше сбросит. Команды на сброс WDT расставлены в разных частях алгоритма управляющей программы таким образом, что сбрасывают таймер всегда раньше, чем таймер сбросит процессор, и при возникновении нештатной ситуации (зависание процессора) команда на сброс таймера не успевает прийти вовремя и WDT сбрасывает процессор.

По такому алгоритму работают все современные WDT. Техническая реализация WDT может быть разной, начиная от простейшей схемы на конденсаторе и транзисторе и заканчивая специализированными микросхемами со множеством дополнительных функций.

В данном курсовом проекте применяется одна из таких специализированных микросхем — ADM 705 фирмы Analog Devices.

FEATURES

Guaranteed RESET Valid with VCC = 1 V

190 mA Quiescent Current

Precision Supply-Voltage Monitor

+4.65 V (ADM705/ADM707)

+4.40 V (ADM706/ADM708)

200 ms Reset Pulse Width

Debounced TTL/CMOS Manual Reset Input (MR)

Independent Watchdog Timer—1.6 sec Timeout (ADM705/ADM706)

Active High Reset Output (ADM707/ADM708)

Voltage Monitor for Power-Fail or Low Battery

Also Available in MicroSOIC Packages

Функциональная схема ADM705

ПРЕДЕЛЬНО ДОПУСТИМЫЕ ПАРАМЕТРЫ

ТИПОВАЯ СХЕМА ВКЛЮЧЕНИЯ WDT ADM705

На вход WDI подаются импульсы с порта P3.7 микропроцессора, которые сбрасывают таймер. Если в течении 1.5 сек. сигнал не поступит на WDI, то на выход WDO подается сигнал логич. "0". Он предназначен для запуска внешнего события или устройства перед посылкой сигнала сброса на микропроцессор. Но так как в нашей схеме такой реакции не предусмотрено, то этот вывод напрямую соединен с непосредственно входом MR – сброс.

Сброс осуществляется выдачей лог. "0" на выход RESET в течении 200 мс. Но процессор МК51 сбрасывается не "0", а "1". Поэтому выход WDT подается на инвертирующую схему, собранную на компараторе LM2900. В блоке сбора информации уже применялся такой компаратор. И в его счетверенной схеме остался один незадействованный прибор. Он и будет использован в качестве инвертора.

Питание на делитель подается с микросхемы опорного напряжения LM4130.

Это напряжение подобрано таким образом, чтобы обеспечить надежное инвертирование сигнала и исключить возможные ложные срабатывания от помех. Сигнал на выходе появляется только при Uвх= 0.5 В.

R1 = 511 Ом;

R2 = 100 Ом.

3.4 Разработка блока индикации входных и выходных сигналов

Для обеспечения визуального наблюдения за функционированием контроллера введен блок индикации сигналов. Его реализация является программной.

Подпрограмма анализирует состояние защиты и при необходимости выводит в требуемый порт Р1.1 – Р1.3 сигнал загорания светодиода красного цвета. Если все в порядке, то будет гореть сигнал готовности на Р1.0

Для того, чтобы светодиоды можно было подключить напрямую к порту, они должны потреблять как можно меньше тока, но при этом обеспечивать достаточную яркость свечения.

Этим запросам полностью удовлетворяют выбранные светодиоды КИПД02Б-1К. Ниже в таблице приведены их основные параметры.

| Тип прибора |

Цвет свечения |

Значения параметров при Т=25° С |

Iпр.мах. mA |

Uобр (Uобр.и ), B |

Тк.мах (Тп. ), ° С |

|||

| Iv. мккд (L, кд/м2 ) |

Uпр. B |

Iпр.ном. mA |

lмах. mkM |

|||||

| КИПД02Б-1К |

Красный |

900 |

1,8 |

5 |

0,7 |

20 |

3.0 |

70 |

При напряжении питания и токе светодиода 5 мА токоограничивающий резистор принимаем равным R=1кОм

Так же, при возникновении аварийной ситуации, одновременно со светодиодной индикацией предусмотрена звуковая сигнализация – "сирена". Она получается программным смешением сигналов, частотой 100 и 200 Гц.

Кроме сигнализации в схеме предусмотрена так же принудительное отключение любой из защит при замыкании соответствующих переключателей.

При срабатывании защиты отключается подача напряжения на вход ТП и выдается сигнал на внешнюю систему управления, для блокировки управляющих импульсов тиристоров.

После срабатывания защиты повторный запуск ТП возможен только после устранения неисправности и нажатия кнопки Reset.

Проанализировав всю схему контроллера было принято решение о том, что процессор должен работать на частоте 12 мГц, в связи с этим был выбран кварц РК171-14БС-12000к

4. Разработка программного обеспечения

Для обеспечения заданного алгоритма логического управления была разработана следующая программа.

5. Список литературы

1. Высоцкий Б.Ф., Назаров А.С. Радиоэлектронная аппаратура//Энциклопедия "Электроника".— М.: Советская энциклопедия, 1991.

2. Осипов О.И., Ю.С. Усынин. Техническая диагностика автоматизированных электроприводов.// Энергоатомиздат.-М. 1991.

3. Конструирование электронных средств/Под ред. А.С.Назарова.— М.:МАИ, 1996.

4. Однокристалльные МикроЭВМ. Справочник/Под ред. Боборыкина, Липовецкого и др. – М.: Советская энциклопеди, 1996.

5. Коледов Л.А., Заводян А.В., Королькевич В.А. Поверхностный монтаж компонентов — новое направление в конструировании и производстве МЭА//Зарубежная электронная техника. 1988. Вып.3 (322), 4 (323).

6. Ушкар М.Н. Микропроцессорные устройства в радиоэлектронной аппаратуре/Под ред. Б.Ф.Высоцкого.—М.:Радио и связь, 1988.

7. Никулин Н.В., Назаров А.С. Радиоматериалы и радиокомпоненты. — М.: Высшая школа, 1986.

8. Основы проектирования микроэлектронной аппаратуры/А.Г.Алексеенко, С.С.Бадулин, Л.Г.Барулин и др.; Под ред. Б.Ф.Высоцкого. — М.:Сов.радио, 1977.