| Скачать .docx |

Реферат: Микропроцессоры и основные понятия

1.

2. Исторические развития М.П. Основные понятия М.Г.

В 1959 г. инженеры фирмы “Texas Instruments” разработали способ, как разместить внутри одного полупроводникового кристалла несколько транзисторов и соединить их между собой – родилась первая интегральная микросхема (ИМС). По сравнению с функционально теми же устройствами, собранными из отдельных транзисторов, резисторов и т.п., ИМС обладает значительными преимуществами: меньшими габаритами, более высокой надежностью и т.д. Неудивительно, что количество выпускаемых микросхем стало быстро возрастать, а их ассортимент неуклонно расширяться. Последнее обстоятельство создавало ряд трудностей для потребителей. Важно даже не столько то, что стремительно возраставшее количество типов ИМС затрудняло ориентацию в море наименований. Значительно большим недостатком была узкая специализация ИМС, из-за которой объем их выпуска не мог быть большим, а значит стоимость одной микросхемы оставалась высокой. Улучшить ситуацию позволило бы создание универсальной логической ИМС, специализация которой определялась бы не заложенной на заводе внутренней структурой, а заданной непосредственно самим потребителем программой работы.

Таким образом, оказывается, что первые микропроцессоры (МП) появились совсем не для миниатюризации ЭВМ, а в целях создания более дешевой логической микросхемы, легко адаптируемой к потребностям пользователя.

Основные понятия

Микропроцессор - это программно управляемое устройство предназначенное для

обработки цифровой информации и управления процессами этой обработки,

выполненной в виде одной или нескольких интегральных схем с высокой степенью

интеграции электронных компонентов.

Микропроцессорный комплект - это набор микросхем необходимых для реализации

одного функционально завершённого вычислительного устройства.

Архитектура МП - это совокупность аппаратных, микропрограммных и программных

средств, определяющая технические, эксплутационные характеристики.

Микропроцессорная система - это управляемая и контрольно - измерительная

система, обрабатывающим элементом в которой является микропроцессор.*

В состав микропроцессорной системы входит микропроцессор (центральный

элемент), который может быть реализован в виде одной СБИС либо в виде одной

платы на которой микропроцессор будет собран из БИС, входящих в единый

микропроцессорный комплект. Микропроцессор МПС выполняет две функции:

1 - служит центральным устройством управления

2 - выполняет арифметико - логическое преобразование данных.

Память МПС имеет иерархическую структуру. Она делится на внутреннюю (ОЗУ, ПЗУ

и КЭШ-память) и внешнюю (накопители на магнитных носителях, на магнитных

лентах, жёсткие диски, флоппи диски).

Устройство ввода - для передачи информации из вне в регистры МП или память

(клавиатура, различные датчики)

Устройство вывода - принимающее информацию из регистра МП или памяти МПС.

Все устройства, входящие в состав МПС имеют стандартный интерфейс, через

который они подключаются к магистрали. Стандартный интерфейс во всех узлах

представлен следующими магистралями: МУ - магисталь управления, МА -

магистраль адреса, МД - магистраль данных.

2.Электрические сигналы. Свойства информации. Обработка цифровых сигналов.

1. Аналоговый сигнал — сигнал, принимающий бесконечное число сколь угодно близких значений из непрерывного множества значений. В отличие от дискретных сигналов, аналоговые сигналы описываются непрерывными функциями времени. Поэтому аналоговый сигнал иногда называют непрерывным сигналом

2. Цифровой сигнал — представляет собой последовательность нулей и единиц. Цифровой сигнал легче передавать на большие расстояния, чем аналоговый сигнал, так как нет проблем с усилением и в несколько раз легче бороться с помехами.

3. Релейный сигнал или элемент, минимальная совокупность деталей и связей между ними, имеющая релейную характеристику , т. е. скачкообразно изменяющая воздействие на выходе (выходах) при поступлении фиксированных воздействий на вход (входы). При построении дискретных управляющих устройств (например, релейных, см. Реле ) Релейный элемент рассматривается как их наиболее простая составная часть.

4. Импульсный сигнал представляет собой сигнал с кратковременным изменением установившегося состояния, характеризующийся малым интервалом времени по сравнению с временными характеристиками установившегося процесса.

Информация — совокупность данных, зафиксированных на материальном носителе, сохранённых и распространённых во времени и пространстве.

Основные виды информации по ее форме представления, способам ее кодирования и хранения, что имеет наибольшее значение для информатики, это:

- графическая или изобразительная — первый вид, для которого был реализован способ хранения информации об окружающем мире в виде наскальных рисунков, а позднее в виде картин, фотографий, схем, чертежей на бумаге, холсте, мраморе и др. материалах, изображающих картины реального мира;

- звуковая — мир вокруг нас полон звуков и задача их хранения и тиражирования была решена с изобретение звукозаписывающих устройств в 1877 г. (см., например, историю звукозаписи на сайте — ее разновидностью является музыкальная информация — для этого вида был изобретен способ кодирования с использованием специальных символов, что делает возможным хранение ее аналогично графической информации;

- текстовая — способ кодирования речи человека специальными символами — буквами, причем разные народы имеют разные языки и используют различные наборы букв для отображения речи; особенно большое значение этот способ приобрел после изобретения бумаги и книгопечатания;

- числовая — количественная мера объектов и их свойств в окружающем мире; особенно большое значение приобрела с развитием торговли, экономики и денежного обмена; аналогично текстовой информации для ее отображения используется метод кодирования специальными символами — цифрами, причем системы кодирования (счисления) могут быть разными;

- видеоинформация — способ сохранения «живых» картин окружающего мира, появившийся с изобретением кино.

- Объективность информации

. Объективный – существующий вне и независимо от человеческого сознания. Информация – это отражение внешнего объективного мира. Информация объективна, если она не зависит от методов ее фиксации, чьего-либо мнения, суждения.

Пример. Сообщение «На улице тепло» несет субъективную информацию, а сообщение «На улице 22°С» – объективную, но с точностью, зависящей от погрешности средства измерения.

Объективную информацию можно получить с помощью исправных датчиков, измерительных приборов. Отражаясь в сознании конкретного человека, информация перестает быть объективной, так как, преобразовывается (в большей или меньшей степени) в зависимости от мнения, суждения, опыта, знаний конкретного субъекта. - Достоверность информации . Информация достоверна, если она отражает истинное положение дел. Объективная информация всегда достоверна, но достоверная информация может быть как объективной, так и субъективной. Достоверная информация помогает принять нам правильное решение. Недостоверной информация может быть по следующим причинам:

- преднамеренное искажение (дезинформация) или непреднамеренное искажение субъективного свойства;

- искажение в результате воздействия помех («испорченный телефон») и недостаточно точных средств ее фиксации.

- Полнота информации . Информацию можно назвать полной, если ее достаточно для понимания и принятия решений. Неполная информация может привести к ошибочному выводу или решению.

- Точность информации определяется степенью ее близости к реальному состоянию объекта, процесса, явления и т. п.

- Актуальность информации – важность для настоящего времени, злободневность, насущность. Только вовремя полученная информация может быть полезна.

- Полезность (ценность) информации . Полезность может быть оценена применительно к нуждам конкретных ее потребителей и оценивается по тем задачам, которые можно решить с ее помощью.

Цифрова́я обрабо́тка сигна́лов — преобразование сигналов, представленных в цифровой форме.

Обработка сигналов во временной области широко используется в современной электронной осциллографии и в цифровых осциллографах. А для представления сигналов в частотной области используются цифровые анализаторы спектра. Для изучния математических аспектов обработки сигналов импользуются пакеты расширения (чаще всего под именем Signal Processing) систем компьютерной математики MATLAB, Mathcad, Mathematica, Maple и др.

3. Арифметические основы микропроцессорной техники. Логические основы микропроцессорной техники.

- Одноразрядное двоичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до

двоичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

двоичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом. - Одноразрядное троичное бинарное (двухоперандное) АЛУ с унарным (одноразрядным) выходом (полуАЛУ) может выполнять до

троичных бинарных (двухоперандных) функций (операций) с унарным (одноразрядным) выходом.

троичных бинарных (двухоперандных) функций (операций) с унарным (одноразрядным) выходом. - Одноразрядное троичное бинарное (двухоперандное) АЛУ с бинарным (двухразрядным) выходом может выполнять до

троичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

троичных бинарных (двухоперандных) функций (операций) с бинарным (двухразрядным) выходом.

3.Арифметические и логические основы МП.

Арифметическо-логическое устройство в зависимости от выполнения функций можно разделить на две части:

- микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

- операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

В состав арифметическо-логического устройства, условно, для примера на картинке, включается регистры Рг1 — Рг7, которые служат для обработки информации, поступающей из оперативной или пассивной памяти N1, N2, …NS и логические схемы, которые используются для обработки слов по микрокомандам, поступающим из устройства управления. Различают два вида микрокоманд: внешние — такие микрокоманды, которые поступают в АЛУ от внешних источников и вызывают в нём преобразование информации (на рисунке 2 это микрокоманды А1,А2,…,Аn) и внутренние — те, которые генерируются в АЛУ и оказывают влияние на микропрограммное устройство, изменяя таким образом нормальный порядок следования команд. р1, p2,…, pm на рисунке 2 — это и есть микрокоманды. А результаты вычислений из АЛУ передаются в ОЗУ по кодовым шинам записи у1, у2, …, ys.

Функции регистров, входящих в арифметическо-логическое устройство

- Рг1 — сумматор (или сумматоры) — главный регистр АЛУ, в котором образуется результат вычислений;

- Рг2,Рг3 — регистры операндов (слагаемого/сомножителя/делителя/делимого и др.) в зависимости от выполняемой операции;

- Рг4 — регистр адреса (или адресные регистры), предназначенные для запоминания (бывает что формирования) адреса операндов результата;

- Рг6 — k индексных регистров, содержимое которых используется для формирования адресов;

- Рг7 — l вспомогательных регистров, которые по желанию программиста могут быть аккумуляторами, индексными регистрами или использоваться для запоминания промежуточных результатов.

Часть операционных регистров могут быть адресованы в команде для выполнения операций с их содержимым и их называют программно-доступными. К таким регистрам относятся: сумматор, индексные регистры и некоторые вспомогательные регистры. Остальные регистры нельзя адресовать в программе, то есть они являются программно-недоступными.

4.Элементы памяти. Элементы преобразования логической информации.

Памятью компьютера называется совокупность устройств для хранения программ, вводимой информации, промежуточных результатов и выходных данных. Классификация памяти представлен на рисунке:

Внутренняя память предназначена для хранения относительно небольших объемов информации при ее обработке микропроцессором.

Внешняя память предназначена для длительного хранения больших объемов информации независимо от того включен или выключен компьютер.

Логические элементы — устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого — «1» и низкого — «0» уровней в двоичной логике, последовательность "0", "1" и "2" в троичной логике, последовательности "0", "1", "2", "3", "4", "5", "6", "7", "8"и "9" в десятичной логике). Физически логические элементы могут быть выполнены механическими, электромеханическими (на электромагнитных реле), электронными (на диодах и транзисторах), пневматическими, гидравлическими, оптическими и др.

Логические операции (булева функция) своё теоретическое обоснование получили в алгебре логики.

Логические операции с одним операндом называются унарными , с двумя — бинарными , с тремя — тернарными (триарными , тринарными ) и т. д.

Из ![]() возможных унарных операций с унарным выходом интерес для реализации представляют операции отрицания и повторения, причём, операция отрицания имеет большую значимость, чем операция повторения, так как повторитель может быть собран из двух инверторов, а инвертор из повторителей не собрать.

возможных унарных операций с унарным выходом интерес для реализации представляют операции отрицания и повторения, причём, операция отрицания имеет большую значимость, чем операция повторения, так как повторитель может быть собран из двух инверторов, а инвертор из повторителей не собрать.

Отрицание, НЕТ, НЕ

![]()

Инвертор

| A |

|

| 0 |

1 |

| 1 |

0 |

Повторение, ДА

![]()

Повторитель (буфер)

| A |

B = A |

| 0 |

0 |

| 1 |

1 |

Преобразование информации требует выполнения операций с группами знаков, простейшей из которых является группа из двух знаков. Оперирование с большими группами всегда можно разбить на последовательные операции с двумя знаками.

Из ![]() возможных бинарных логических операций с двумя знаками c унарным выходом интерес для реализации представляют 10 операций, приведённых ниже.

возможных бинарных логических операций с двумя знаками c унарным выходом интерес для реализации представляют 10 операций, приведённых ниже.

Конъюнкция (логическое умножение). Операция 2И

![]()

2И

| A |

B |

f (AB ) |

| 0 |

0 |

0 |

| 1 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

1 |

1 |

Мнемоническое правило для конъюнкции с любым количеством входов звучит так: На выходе будет:

· "1" тогда и только тогда, когда на всех входах действуют «1»,

· "0" тогда и только тогда, когда хотя бы на одном входе действует «0»

Дизъюнкция (логическое сложение). Операция 2 ИЛИ

![]()

2ИЛИ

| A |

B |

f (AB ) |

| 0 |

0 |

0 |

| 1 |

0 |

1 |

| 0 |

1 |

1 |

| 1 |

1 |

1 |

Мнемоническое правило для дизъюнкции с любым количеством входов звучит так: На выходе будет:

· "1" тогда и только тогда, когда хотя бы на одном входе действует «1»,

· "0" тогда и только тогда, когда на всех входах действуют «0»

Инверсия функции конъюнкции. Операция 2 И-НЕ (штрих Шеффера)

![]()

2И-НЕ

| A |

B |

f (AB ) |

| 0 |

0 |

1 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Мнемоническое правило для И-НЕ с любым количеством входов звучит так: На выходе будет:

· "1" тогда и только тогда, когда хотя бы на одном входе действует «0»,

· "0" тогда и только тогда, когда на всех входах действуют «1»

Инверсия функции дизъюнкции. Операция 2 ИЛИ-НЕ (стрелка Пирса)

![]()

2ИЛИ-НЕ

| A |

B |

f (AB ) |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 1 |

0 |

0 |

| 1 |

1 |

0 |

Мнемоническое правило для ИЛИ-НЕ с любым количеством входов звучит так: На выходе будет:

· "1" тогда и только тогда, когда на всех входах действуют «0»,

· "0" тогда и только тогда, когда хотя бы на одном входе действует «1»

Эквивалентность (равнозначность), 2 ИСКЛЮЧАЮЩЕЕ_ИЛИ-НЕ

| A |

B |

f (AB ) |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 1 |

0 |

0 |

| 1 |

1 |

1 |

Мнемоническое правило эквивалентности с любым количеством входов звучит так: На выходе будет:

· "1" тогда и только тогда, когда на входа действует четное количество «1»,

· "0" тогда и только тогда, когда на входа действует нечетное количество «1»,

Сложение по модулю 2 (2 Исключающее_ИЛИ, неравнозначность). Инверсия равнозначности.

![]()

В англоязычной литературе 2XOR.

| A |

B |

f (AB ) |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Мнемоническое правило для суммы по модулю 2 с любым количеством входов звучит так: На выходе будет:

· "1" тогда и только тогда, когда на входа действует нечётное количество «1»,

· "0" тогда и только тогда, когда на входа действует чётное количество «1»,

Импликация от A к B (инверсия декремента)

| A |

B |

f (AB ) |

| 0 |

0 |

1 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

| 1 |

1 |

1 |

Импликация от B к A (инверсия инкремента)

| A |

B |

f (AB ) |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

1 |

Декремент. Запрет импликации по B. Инверсия импликации от A к B

| A |

B |

f (AB ) |

| 0 |

0 |

0 |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Инкремент. Запрет импликации по A. Инверсия импликации от B к A

| A |

B |

f (AB ) |

| 0 |

0 |

0 |

| 0 |

1 |

1 |

| 1 |

0 |

0 |

| 1 |

1 |

0 |

Примечание 1

. Элементы импликаций не имеют промышленных аналогов для функций с количеством входов, не равным 2.

Примечание 2

. Элементы импликаций не имеют промышленных аналогов.

Этими простейшими логическими операциями (функциями), и даже некоторыми их подмножествами, можно выразить любые другие логические операции. Такой набор простейших функций называется функционально полным логическим базисом . Таких базисов 4:

· И, НЕ (2 элемента)

· ИЛИ, НЕ (2 элемента)

· И-НЕ (1 элемент)

· ИЛИ-НЕ (1 элемент).

Для преобразования логических функций в один из названых базисов необходимо применять Закон (правило) де-Моргана

5.Структура микропроцессорной системы. Принцип программного управления Неймана.

Гарвардская архитектура.

Базовая структура микропроцессорной системы имеем вид

Задача управления системой возлагается на центральный процессор (ЦП), который связан с памятью и системой ввода-вывода через каналы памяти и ввода-вывода соответственно. ЦП считывает из памяти команды, которые образуют программу и декодирует их. В соответствии с результатом декодирования команд он осуществляет выборку данных из памяти м портов ввода, обрабатывает их и пересылает обратно в память или порты вывода. Существует также возможность ввода-вывода данных из памяти на внешние устройства и обратно, минуя ЦП. Этот механизм называется прямым доступом к памяти (ПДП). Каждая составная часть микропроцессорной системы имеет достаточно сложную внутреннюю структуру.

С точки зрения пользователя при выборе микропроцессора целесообразно располагать некоторыми обобщенными комплексными характеристиками возможностей микропроцессора. Разработчик нуждается в уяснении и понимании лишь тех компонентов микропроцессора, которые явно отражаются в программах и должны быть учтены при разработке схем и программ функционирования системы. Такие характеристики определяются понятием архитектуры микропроцессора.

Архитектура микропроцессора - это его логическая организация, рассматриваемая с точки зрения пользователя; она определяет возможности микропроцессора по аппаратной и программной реализации функций, необходимых для построения микропроцессорной системы. Понятие архитектуры микропроцессора отражает:

- его структуру, т.е. совокупность компонентов, составляющих микропроцессор, и связей между ними; для пользователя достаточно ограничиться регистровой моделью микропроцессора;

- способы представления и форматы данных;

- способы обращения ко всем программно-доступным для пользователя элементам структуры ( адресация к регистрам, ячейкам постоянной и оперативной памяти, внешним устройствам);

- набор операций, выполняемых микропроцессором;

- характеристики управляющих слов и сигналов, вырабатываемых микропроцессором и поступающих в него извне;

- реакцию на внешние сигналы ( система обработки прерываний и т.п.).

По способу организации пространства памяти микропроцессорной системы различают два основных типа архитектур.

Организация, при которой для хранения программ и данных используется одно пространство памяти, называется фон Неймановской архитектурой (по имени математика, предложившего кодирование программ в формате, соответствующем формату данных). Программы и данные хранятся в едином пространстве, и нет никаких признаков, указывающих на тип информации в ячейке памяти. Преимуществами такой архитектуры являются более простая внутренняя структура микропроцессора и меньшее количество управляющих сигналов.

Организация, при которой память программ CSEG (Code Segment) и память данных DSEG (Data Segment) разделены и имеют свои собственные адресные пространства и способы доступа к ним, называется Гарвардской архитектурой ( по имени лаборатории Гарвардского Университета, предложившей ее). Такая архитектура является более сложной и требует дополнительных управляющих сигналов. Однако, она позволяет осуществлять более гибкие манипуляции информации, реализовывать компактно кодируемый набор машинных команд и, в ряде случаев, ускорять работу микропроцессора. Представителями такой архитектуры являются микроконтроллеры семейства MCS-51 фирмы Intel.

6.Представление числовой информации. Представление текстовой информации.

Обработка информации.

В ЭВМ используются три вида чисел: с фиксированной точкой (запятой), с плавающей точкой (запятой) и двоично-десятичное представление. Точка (запятая) - это подразумеваемая граница целой и дробной частей числа.

У чисел с фиксированной точкой в двоичном формате предполагается строго определенное место точки (запятой). Обычно это место определяется или перед первой значащей цифрой числа, или после последней значащей цифрой числа. Если точка фиксируется перед первой значащей цифрой, то это означает, что число по модулю меньше единицы. Диапазон изменения значений чисел определяется неравенством

![]() .

.

Если точка фиксируется после последней значащей цифры, то это означает, что п- разрядные двоичные числа являются целыми. Диапазон изменения их значений составляет:

![]()

Перед самым старшим из возможных разрядов двоичного числа фиксируется его знак. Положительные числа имеют нулевое значение знакового разряда, отрицательные - единичные.

Другой формой представления чисел является представление их в виде чисел с плавающей точкой (запятой). Числа с плавающей точкой представляются в виде мантиссы т a и порядка р a , иногда это представление называют полулогарифмической формой числа. Например, число A10 = 373 можно представить в виде 0.373 • 103, при этом т = 0.373, р = 3, основание системы счисления подразумевается фиксированным и равным десяти. Для двоичных чисел А 2 в этом представлении также формируется т a и порядок р a при основании системы счисления равным двум.

![]()

что соответствует записи

![]()

Порядок числа р a определяет положение точки (запятой) в двоичном числе. Значение порядка лежит в диапазоне -р a max <=р a <=р a max , где величина pa mах определяется числом разрядов к, отведенных для представления порядка

![]()

Положительные и отрицательные значения порядка значительно усложняют обработку вещественных чисел. Поэтому во многих современных ЭВМ используют не прямое значение р a , а модифицированное р 'a приведенное к интервалу

![]()

Значение р 'a носит название “характеристика числа”. Обычно под порядок (модифицированный порядок - характеристику) выделяют один байт. Старший разряд характеристики отводится под знак числа, а семь оставшихся разрядов обеспечивают изменение порядка в диапазоне

![]()

Модифицированный порядок р ' a вычисляется по зависимости

![]()

Этим самым значения р' a формируются в диапазоне положительных чисел

![]()

Мантисса числа ma представляется двоичным числом, у которого точка фиксируется перед старшим разрядом, т. е.

![]()

где k - число разрядов, отведенных для представления мантиссы.

Если

![]()

то старший значащий разряд мантиссы в системе счисления с основанием N отличен от нуля. Такое число называется нормализованным. Например, A2 =(100;0.101101)2 -нормализованное число А 2 = 1011.01 или А 10 = 11.25, а то же самое число А 2 = (101 ;0.0101101) - число ненормализованное, так как старший разряд мантиссы равен нулю.

Диапазон представления нормализованных чисел с плавающей точкой определяется

![]()

где r и k - соответственно количество разрядов, используемых для представления порядка и мантиссы.

Третья форма представления двоичных чисел - двоично-десятичная. Ее появление объясняется следующим. При обработке больших массивов десятичных чисел (например, больших экономических документов) приходится тратить существенное время на перевод этих чисел из десятичной системы счисления в двоичную для последующей обработки и обратно -для вывода результатов. Каждый такой перевод требует выполнения двух - четырех десятков машинных команд. С включением в состав отдельных ЭВМ специальных функциональных блоков или спецпроцессоров десятичной арифметики появляется возможность обрабатывать десятичные числа напрямую, без их преобразования, что сокращает время вычислений. При этом каждая цифра десятичного числа представляется двоичной тетрадой. Например, A10 =3759, A2-10 = 0011 0111 0101 1001. Положение десятичной точки (запятой), отделяющей целую часть от дробной, обычно заранее фиксируется. Значение знака числа отмечается кодом, отличным от кодов цифр. Например, “+” имеет значение тетрады “1100”, а “-” - “1101”.

ЭВМ первых двух поколений могли обрабатывать только числовую информацию, полностью оправдывая свое название вычислительных машин. Лишь переход к третьему поколению принес изменения: к этому времени уже назрела настоятельная необходимость использования текстов.

С точки зрения ЭВМ текст состоит из отдельных символов. К числу символов принадлежат не только буквы (заглавные или строчные, латинские или русские), но и цифры, знаки препинания, спецсимволы типа "=", "(", "&" и т.п. и даже (обратите особое внимание!) пробелы между словами. Да, не удивляйтесь: пустое место в тексте тоже должно иметь свое обозначение.

Каждый символ хранится в виде двоичного кода, который является номером символа. Можно сказать, что компьютер имеет собственный алфавит, где весь набор символов строго упорядочен. Количество символов в алфавите также тесно связано с двоичным представлением и у всех ЭВМ равняется 256 . Иными словами, каждый символ всегда кодируется 8 битами , т.е. занимает ровно один байт .

Как видите, хранится не начертание буквы, а ее номер. Именно по этому номеру воспроизводится вид символа на экране дисплея или на бумаге. Поскольку алфавиты в различных типах ЭВМ не полностью совпадают, при переносе с одной модели на другую может произойти превращение разумного текста в "абракадабру". Такой эффект иногда получается даже на одной машине в различных программных средах: например, русский текст, набранный в MS DOS, нельзя без специального преобразования прочитать в Windows. Остается утешать себя тем, что задача перекодировки текста из одной кодовой таблицы в другую довольно проста и при наличии программ машина сама великолепно с ней справляется.

Наиболее стабильное положение в алфавитах всех ЭВМ занимают латинские буквы, цифры и некоторые специальные знаки. Это связано с существованием международного стандарта ASCII (American Standard Code for Information Interchange - Американский стандартный код для обмена информацией). Русские же буквы не стандартизированы и могут иметь различную кодировку.

Желающие могут в качестве примера ознакомится с таблицей стандартной части алфавита ЭВМ - символы с шестнадцатиричными кодами с 20 до 7F.

7. Структурная схема микропроцессора.

Главным устройством любой ЭВМ является центральный процессор. Он выбирает из памяти команды программы и выполняет их. Обычный цикл работы центрального процессора выглядит так: он читает первую команду из памяти, декодирует ее для определения ее типа и операндов, выполняет команду, затем считывает, декодирует и выполняет последующие команды. Таким образом, осуществляется выполнение программ. Пример выполнения команд процессором можно посмотреть здесь .

Ранее было отмечено, что каждый процессор характеризуется набор команд , который он в состоянии выполнить. Например, процессор Pentium фирмы не может обработать программы, написанные для процессора SPARC фирмы Sun, а SPARC не может выполнить программы, написанные для Pentium.

Укрупненную структурную схему типичного процессора можно представить в виде трех основных блоков: управляющего блока УБ, операционного блока ОБ и интерфейсного блока ИБ. Управляющий блок выполняет функции выборки, декодирования и вычисления адресов операндов, а так же генерирует последовательности микрокоманд, реализующих команды процессора. Он содержит устройство управления, прерывания, синхронизации. Операционный блок служит для обработки данных. Он объединяет арифметико-логическое устройство АЛУ, регистры общего назначения РОН и специальные регистры. АЛУ выполняет арифметические (сложение, вычитание и т.п.) и логические (логическое И, ИЛИ и т.п.) операции. Регистры являются своего рода памятью ОБ, предназначенной для хранения промежуточных результатов и некоторых команд управления, информацию о состоянии процессора. Информация из них считываются и записываются очень быстро, поскольку они находятся внутри процессора. Регистров может быть от несколько десятков до нескольких сотен штук в зависимости от типа процессора. Большим количеством регистров характеризуются RISC - процессоры , а небольшим - CISC - процессоры

Интерфейсный блок ИБ позволяет подключить память и периферийные устройства к процессору. ИБ выполняет также функции канала прямого доступа к памяти. Интерфейс процессора содержит информационные шины данных ШД, адресов ША и управления ШУ. Надо заметить, что такое распределение аппаратных блоков процессора между функциональными частями весьма условно и приводится для примера.

Процессор выполняет каждую команду за несколько шагов:

1. вызывает следующую команду из памяти и переносит ее в регистр команд;

2. меняет положение счетчика команд, который теперь должен указывать на следующую команду;

3. определяет тип вызванной команды;

4. если команда использует данные из памяти, определяет место нахождение данных;

5. переносит данные в регистр процессора;

6. выполняет команду;

7. переходит к 1 шагу, что бы начать выполнение следующей команды.

Эта последовательность шагов (выборка – декодирование – исполнение) является основой работы для всех процессоров.

Упрощенная структурная схема типичного процессора изображена на следующем рисунке.

Кроме регистров общего назначения РОН, используемых для хранения переменных и временных результатов, большинство процессоров имеют несколько специальных регистров, также доступных для программиста. Один из них называется счетчиком команд СчК, в котором содержится адрес следующей, стоящей в очереди на выполнение команды. После того как команда выбрана из памяти, регистр команд корректируется и указатель переходит к следующей команде. Регистр процессора, служащий для организации стековой памяти, называется указателем стека УС. Он содержит адрес вершины стека в памяти. Стек содержит по одному фрейму (области данных) для каждой процедуры, которая уже начала выполняться, но еще не закончена. В стековом фрейме процедуры хранятся ее входные параметры, а также локальные и временные переменные, не хранящиеся в регистрах.

Первый байт любой команды поступает из ОЗУ по шине данных на регистр команд РК. Этот первый байт подается в управляющий блок УБ, который определяет вид операции. В частности, он определяет, является ли команда однобайтовой, или она состоит из большего числа байтов. В последнем случае дополнительные байты передаются по шинам данных из ОЗУ и принимаются или в регистр адреса РА данных, или в один из регистров РОН

Регистр адреса данных РА содержит адрес операнда для команд, обращающихся к памяти, адрес порта для команд ввода/вывода или адрес следующей команды для команд перехода. Регистры РОН могут содержать операнды для всех команд, работающих с данными. Среди РОН есть специальный регистр результата РР или аккумулятор, участвующий во всех арифметических и логических операциях. В частности, он содержит один из операндов перед выполнением операции и получает результат после ее завершения. Все арифметические и логические операции выполняются в арифметико – логическом устройстве АЛУ. Результаты из АЛУ передаются либо в РР, либо в какой-то из регистров РОН.

Процессор имеет регистр признаков РП , содержащий в своих разрядах значения, которые отражают результаты выполнения некоторых команд процессора, приоритет текущей программы, режим работы процессора (пользовательский или режим ядра). Также РП содержит другую служебную информацию. Обычно пользовательские программы могут читать весь регистр РП целиком, но изменять могут только некоторые из его полей. Регистр РП играет важную роль в системных вызовах и операциях ввода-вывода.

В управляющем блоке УБ дешифрируется и анализируется код команды, поступающий из РК. В УБ из АЛУ и от триггера переноса поступают сигналы, по которым определяются условия для передачи управления. Все остальные компоненты процессора получают от УБ управляющие и синхронизирующие сигналы, необходимые для выполнения команды.

Операционная система должна знать все обо всех регистрах. При временном мультиплексировании центрального процессора операционная система часто останавливает работающую программу для запуска (или перезапуска) другой программы, например, обслуживающей периферийное устройство. Каждый раз при таком процессе, называемом прерыванием , операционная система должна сохранять значения тех регистров процессора, которые будут востановленны позже, для того чтобы прерванная программа продолжила свою работу без потери данных, с того места, где она была прервана.

В целях улучшения характеристик центральных процессоров их разработчики давно отказались от простой модели, в которой за один такт может быть считана, декодирована и выполнена только одна команда. Многие современные процессоры обладают возможностями выполнения нескольких команд одновременно. Например, у процессора могут быть раздельные модули, занимающиеся выборкой, декодированием и выполнением команд, и во время выполнения команды с номером n он может декодировать команду с номером n + 1 и считывать команду с номером n + 2. Подобная организация процесса называется конвейером. Более передовым по сравнению с конвейерной конструкцией является суперскалярный процессор. В этой структуре присутствует множество выполняющих узлов: один для целочисленных арифметических операций, второй - для операций с плавающей точкой и еще один - для логических операций. За один такт считывается две или более команды, которые декодируются и сбрасываются в буфер хранения, где они ждут своей очереди на выполнение. Когда выполняющее устройство освобождается, оно заглядывает в буфер хранения, интересуясь, есть ли там команда, которую оно может обработать, и если да, то забирает ее и выполняет. В результате команды часто исполняются не в порядке их следования. В большинстве случаев аппаратура должна гарантировать, что результат совпадет с тем, который выдала бы последовательная конструкция

Большинство процессоров, используемых в современных ЭВМ, имеют два режима работы: режим ядра и пользовательский режим. Обычно режим задается битом РП или слова состояния процессора. Если процессор запущен в режиме ядра, он может выполнять все команды из набора инструкций и использовать все возможности аппаратуры. Операционная система работает в режиме ядра, предоставляя доступ ко всему оборудованию.

В противоположность этому программы пользователей работают в пользовательском режиме, разрешающем выполнение подмножества команд и делающем доступным лишь часть аппаратных средств. Как правило, все команды, включая ввод-вывод данных и защиту памяти, запрещены в пользовательском режиме. Установка бита режима ядра в регистре признаков РП пользовательском режиме естественно, недоступна.

Для связи с операционной системой пользовательская программа должна сформировать системный вызов, который обеспечивает переход в режим ядра и активизирует функции операционной системы. После завершения работы управление возвращается к пользовательской программе, к команде, следующей за системным вызовом.

Стоит отметить, что в компьютерах, помимо инструкций для выполнения системных вызовов, есть и другие прерывания . Большинство этих прерываний вызываются аппаратно для предупреждения об исключительных ситуациях, таких как попытка деления на ноль или переполнение при операциях с плавающей точкой. Во всех подобных случаях управление переходит к операционной системе, которая должна решать, что делать дальше. Иногда нужно завершить программу с сообщением об ошибке. В других случаях ошибку можно проигнорировать (например, при потере значимости числа его можно принять равным нулю). Наконец, если программа объявила заранее, что требуется обработать некоторые виды условий, управление может вернуться назад к программе, позволяя ей самой разрешить появившуюся проблему.

8. Основные параметры и классификация МП.

Микропроцессор как функциональное устройство ЭВМ обеспечивает эффективное автоматическое выполнение операций обработки цифровой информации в соответствии с заданным ал-горитмом. Для решения широкого круга задач в различных облас-тях применений микропроцессор должен обладать алгоритмически полной системой команд (операций).

Теоретически показано, что минимальная алгоритмически полная система команд процессора состоит из одной или несколь-ких универсальных команд. Однако использование процессоров с минимальными по числу операций системами команд ведет к не-экономичному использованию информационных емкостей памяти и значительным затратам времени на выполнение «длинных» про-грамм. Поэтому обычно в МП встраиваются аппаратурные средст-ва, позволяющие реализовать многие десятки и сотни команд. Та-кие развитые системы команд дают возможность обеспечить ком-пактную запись алгоритмов и соответственно эффективные про-граммы.

При проектировании МП решаются задачи определения на-боров команд, выполняемых программным или аппаратурным способом на основе заданной системы микрокоманд. Аппаратур-ная реализация сложных команд дает возможность увеличить бы-стродействие микропроцессора, но требует значительных аппара-турных ресурсов кристалла интегральной схемы МП. Программ-ная реализация сложных команд позволяет обеспечивать програм-мирование сложных задач, изменять количество и особенности исполнения сложных команд. Однако скорость исполнения программных команд ниже скорости исполнения аппаратурно-реализованных команд.

Практически во всех современных МПС используются сложные развитые системы команд. Их ядро, состоящее из набора универсальных команд, реализуется аппаратурным способом в центральном МП. Кроме того, специализированные части наборов системы команд реализуются вспомогательными или периферий-ными микропроцессорами. Эти расширяющие возможности обра-ботки данных специальные арифметические или логические МП позволяют ускорить выполнение определенных команд и тем са-мым сократить время исполнения программ.

Для описания МП как функциональных устройств необхо-димо охарактеризовать формат обрабатываемых данных и команд, количество, тип и гибкость команд, методы адресации данных, число внутренних регистров общего назначения и регистров ре-зультата, возможности организации и адресации стека, параметры виртуальной памяти и информационную емкость прямо адресуе-мой памяти. Большое значение имеют средства построения систе-мы прерываний программ, построения эффективных систем ввода — вывода данных и развитого интерфейса.

МП могут быть реализованы на различной физической ос-нове: на электронной, оптоэлектронной, оптической, биологиче-ской и даже на пневматической или гидравлической.

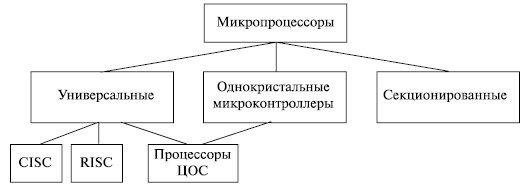

По назначению различают универсальные и специализиро-ванные микропроцессоры.

Универсальные МП предназначены для решения широкого круга задач. При этом их эффективная производительность слабо зависит от проблемной специфики решаемых задач В системе ко-манд МП заложена алгоритмическая универсальность, означаю-щая, что выполняемый машиной состав команд позволяет полу-чить преобразование информации в соответствии с любым задан-ным алгоритмом.

К универсальным МП относятся и секционные микропро-цессоры, поскольку для них система команд может быть оптими-зирована в каждом частном проекте создания секционного микро-процессора.

Эта группа МП наиболее многочисленна, в нее входят та-кие комплекты как К580, Z80, Intel 80?86, К582, К587, К1804, К1810 и др.

Специализированные МП предназначены для решения оп-ределенного класса задач, а иногда только для решения одной конкретной задачи. Их существенными особенностями являются простота управления, компактность аппаратурных средств, низкая стоимость и малая мощность потребления.

Специализированные МП имеют ориентацию на ускорен-ное выполнение определенных функций, что позволяет резко уве-личить эффективную производительность при решении только оп-ределенных задач.

Среди специализированных микропроцессоров можно вы-делить различные микроконтроллеры, ориентированные на вы-полнение сложных последовательностей логических операций; математические МП, предназначенные для повышения производи-тельности при выполнении арифметических операций за счет, на-пример матричных методов их выполнения; МП для обработки данных в различных областях применений и т. д.

С помощью специализированных МП можно эффективно решать новые сложные задачи параллельной обработки данных. Например, они позволяют осуществить более сложную математи-ческую обработку сигналов, чем широко используемые методы корреляции, дают возможность в реальном масштабе времени на-ходить соответствие для сигналов изменяющейся формы путем сравнения их с различными эталонными сигналами для эффектив-ного выделения полезного сигнала на фоне шума и т.д.

По виду обрабатываемых входных сигналов различают цифровые и аналоговые микропроцессоры.

Сами МП являются цифровыми устройствами обработки информации. Однако в ряде случаев они могут иметь встроенные аналого-цифровые и цифро-аналоговые преобразователи. Поэтому входные аналоговые сигналы передаются в МП через преобразова-тель в цифровой форме, обрабатываются и после обратного преоб-разования в аналоговую форму поступают на выход.

С архитектурной точки зрения такие микропроцессоры представляют собой аналоговые функциональные преобразователи сигналов. Они выполняют функции любой аналоговой схемы (например, производят генерацию колебаний, модуляцию, смеще-ние, фильтрацию, кодирование и декодирование сигналов в реаль-ном масштабе времени и т. д., заменяя сложные схемы, состоящие из операционных усилителей, катушек индуктивности, конденса-торов и т.д.). При этом применение аналогового МП значительно повышает точность обработки аналоговых сигналов и их воспро-изводимость, а также расширяет функциональные возможности за счет программной “настройки” цифровой части микропроцессора на различные алгоритмы обработки сигналов.

Обычно в составе однокристальных аналоговых МП имеет-ся несколько каналов аналого-цифрового и цифро-аналогового преобразования. В аналоговом микропроцессоре разрядность об-рабатываемых данных достигает 24 бит и более. Большое значение уделяется увеличению скорости выполнения арифметических опе-раций.

Отличительная черта аналоговых МП - это способность к переработке большого объема числовых данных, т. е. к выполне-нию операций сложения и умножения с большой скоростью, при необходимости даже за счет отказа от операций прерываний и пе-реходов. Аналоговый сигнал, преобразованный в цифровую фор-му, обрабатывается в реальном масштабе времени и передается на выход обычно в аналоговой форме через цифро-аналоговый пре-образователь. При этом согласно теореме Котельникова частота квантования аналогового сигнала должна вдвое превышать верх-нюю частоту сигнала.

Одним из направлений дальнейшего совершенствования аналоговых МП является повышение их универсальности и гибко-сти. Поэтому вместе с повышением скорости обработки большого объема цифровых данных будут развиваться средства обеспечения развитых вычислительных процессов обработки цифровой инфор-мации за счет реализации аппаратурных блоков прерывания про-грамм и программных переходов.

По количеству выполняемых программ различают одно- и многопрограммные микропроцессоры.

В однопрограммных МП выполняется только одна про-грамма. Переход к выполнению другой программы происходит после завершения текущей программы.

В много- или мультипрограммных МП одновременно вы-полняется несколько (обычно несколько десятков) программ. Ор-ганизация мультипрограммной работы микропроцессорных управ-ляющих систем, например, позволяет осуществить контроль за со-стоянием и управлением большим числом источников или прием-ников информации.

9.Запоминающие устройства. Основные параметры и классификация.

Запоминающее устройство — носитель информации, предназначенный для записи и хранения данных. В основе работы запоминающего устройства может лежать любой физический эффект, обеспечивающий приведение системы к двум или более устойчивым состояниям.

По устойчивости записи и возможности перезаписи ЗУ делятся на:

- Постоянные ЗУ (ПЗУ), содержание которых не может быть изменено конечным пользователем (например, BIOS). ПЗУ в рабочем режиме допускает только считывание информации.

- Записываемые ЗУ (ППЗУ), в которые конечный пользователь может записать информацию только один раз (например, CD-R).

- Многократно перезаписываемые ЗУ (ПППЗУ) (например, CD-RW).

- Оперативные ЗУ (ОЗУ) обеспечивает режим записи, хранения и считывания информации в процессе её обработки. Быстрые, но дорогие ОЗУ (SRAM) строят на триггерах, более медленные, но дешёвые разновидности ОЗУ — динамические ЗУ (DRAM) строят на конденсаторах. В обоих видах ЗУ информация исчезает после отключения от источника тока.

По типу доступа ЗУ делятся на:

- Устройства с последовательным доступом (например, магнитные ленты).

- Устройства с произвольным доступом (RAM) (например, оперативная память).

- Устройства с прямым доступом (например, жесткие магнитные диски).

- Устройства с ассоциативным доступом (специальные устройства, для повышения производительности БД)

По геометрическому исполнению :

- дисковые (магнитные диски, оптические, магнитооптические);

- ленточные (магнитные ленты, перфоленты);

- барабанные (магнитные барабаны);

- карточные (магнитные карты, перфокарты, флэш-карты, и др.)

- печатные платы (карты DRAM, картриджи).

По физическому принципу :

- перфорационные (с отверстиями или вырезами)

- перфокарта

- перфолента

- с магнитной записью

- ферритовые сердечники

- магнитные диски

- Жёсткий магнитный диск

- Гибкий магнитный диск

- магнитные ленты

- магнитные карты

- оптические

- CD

- DVD

- HD-DVD

- Blu-ray Disc

- магнитооптические:

- CD-MO

- использующие накопление электростатического заряда в диэлектриках (конденсаторные ЗУ, запоминающие электроннолучевые трубки);

- использующие эффекты в полупроводниках (EEPROM, флэш-память)

- звуковые и ультразвуковые (линии задержки);

- использующие сверхпроводимость (криогенные элементы);

- другие.

По форме записанной информации выделяют аналоговые и цифровые запоминающие устройства.

Цифровые запоминающие устройства — устройства, предназначенные для записи, хранения и считывания информации, представленной в цифровом коде.

К основным параметрам ЗУ относятся информационная ёмкость (бит), потребляемая мощность, время хранения информации, быстродействие.

Самое большое распространение запоминающие устройства приобрели в компьютерах (компьютерная память). Кроме того, они применяются в устройствах автоматики и телемеханики, в приборах для проведения экспериментов, в бытовых устройствах (телефонах, фотоаппаратах, холодильниках, стиральных машинах и т. д.), в пластиковых карточках, замках

- Магнитные ЗУ в пластиковых картах

- Флеш-память: USB-накопители, карты памяти в телефонах и фотоаппаратах, SSD

- Оптические диски: CD, DVD, Blu-Ray и др.

- Жёсткие диски (НЖМД)

- Микросхемы SDRAM (DDR и XDR)

Некоторые типы запоминающих устройств оформлены как компактные, носимые человеком устройства, приспособленные для переноса информации. В частности:

- Флеш-память

- Переносной жёсткий диск:

- Mobile Rack

- Контейнеры для жёстких дисков

- ZIV

10. Адресная, стековая и ассоциативная память. Стековая память. Полупроводниковая память.

Память - совокупность отдельных устройств, которые запоминают, хранят, выдают информацию. Отдельные устройства памяти называют запоминающими устройствами. Производительность вычислительных систем в значительной мере определяется составом и характеристиками отдельных запоминающих устройств, которые различают по принципу действия, техническим характеристикам, назначениям. Основные операции с памятью - процедура записи, процедура чтения (выборки). Процедуры записи и чтения также называют обращением к памяти. За одно обращение к памяти "обрабатывается" для различных устройств различные единицы данных (байт, слово, двойное слово, блок).

Основные технические характеристики памяти

Одними из основных характеристик памяти является емкость и быстродействие (время обращения к запоминающему устройству).

Время обращения к устройству зависит от типа памяти.

В некоторых запоминающих устройствах считывание данных сопровождается их разрушением. В этом случае цикл обращения к памяти всегда должен содержать регенерацию данных (ЗУ динамического типа). Этот цикл состоит из трех шагов:

- время от начала операции обращения до того момента, как данные станут доступны (время доступа);

- считывание;

- регенерация.

Основные технические характеристики процедуры записи:

- время доступа;

- время подготовки (приведение в исходное состояние поверхности магнитного диска при записи);

- запись.

Максимальная длительность чтения-записи называется временем обращения к памяти.

По физическим основам все запоминающие устройства разделяются: полупроводниковые, магнитно-оптические и т.д.

Организация полупроводниковой памяти

С точки зрения функционального построения, любое запоминающее устройство такого типа представляет собой некоторый массив элементов памяти. Структурные элементы памяти образуют ячейки памяти. Ширина ячеек - ширина выборки из памяти. Структура модуля памяти определяется способом организации памяти (способ адресации).

Существует 3 разновидности организации памяти:

- адресная память

- память со стековой организацией

- ассоциативная память

Random Access Memory - запоминающие устройства с произвольной выборкой

В адресной памяти, размещение и поиск информации в массиве запоминания, базируется на основе номера (адреса). Массив запоминания элементов содержит N n-разрядных слов, которые пронумерованы (0...N-1). Электронное обрамление включает в себя регистры для хранения адреса памяти, регистр информации (само слово), схемы адресной выборки (адресации), разрядные усилители для чтения и записи.

Рис. 8.1.

Цикл обращения таких устройств не зависит от того, в каком физическом месте ЗУ находятся требуемые данные. Такой способ доступа характерен для полупроводниковых ЗУ. Число записанных одновременно битов данных за одно обращение называют шириной выборки (доступа).

Рис. 8.2.

Основная память современных компьютеров реализуется на микросхемах статических и динамических RAM.

Статическая память

Память на основе микросхем, которые могут сохранять свое состояние лишь тех пор, пока к ним подключено питание, называется статической (Static RAM, SRAM). Может быть реализована на триггерах. Микросхемы статических SRAM имеют малое время доступа и не требуют циклов регенерации.

Статическая RAM работает быстро, но стоит очень дорого, поскольку каждая ее ячейка содержит несколько транзисторов. Вот почему выпускается еще и более дешевая память с более простой конструкцией ячеек. Однако эти ячейки не способны бесконечно долго сохранять свое состояние, поэтому такая память называется динамической (Dynamic RAM, DRAM).

Динамическая память

В ячейке динамической памяти информация хранится в форме заряда на конденсаторе, и этот заряд может сохраняться всего несколько десятков миллисекунд. Поскольку ячейка памяти должна хранить информацию гораздо дольше, ее содержимое должно периодически обновляться путем восстановления заряда на конденсаторе.

Рис. 8.3.

Ячейка динамической памяти, состоим из конденсатора С и транзистора Т. Для записи информации в эту ячейку включается транзистор Т и на линию бита подается соответствующее напряжение. В результате на конденсаторе образуется определенный заряд.

После выключения транзистора конденсатор начинает разряжаться. Это происходит из-за его собственного тока утечки, а также из-за того, что после выключения сопротивление транзистора велико, но все же конечно, поэтому он продолжает проводить ток. Полученная информация не содержит ошибок лишь в том случае, если она считывается из ячеек до того, как заряд конденсатора падает ниже определенного порогового значения. Операция чтения производится, когда транзистор выбранной ячейки включен. Соединенный с линией бита усилитель считывания определяет, превышает ли заряд конденсатора пороговое значение. Если да, он подает на линию бита напряжение, соответствующее значению 1. В результате конденсатор заряжается до напряжения, также соответствующего 1. Если заряд на конденсаторе ниже порогового значения, усилитель считывания снижает напряжение на линии бита до уровня "земли", обеспечивая тем самым отсутствие заряда (логическое значение 0) на конденсаторе. Таким образом, в процессе считывания содержимое ячейки автоматически обновляется (регенерируется). Все ячейки выбранной строки считываются одновременно, в результате чего обновляется содержимое всей строки.

Ко всем строкам всех микросхем DRAM основной памяти компьютера должны производиться периодические обращения в пределах определенного временного интервала порядка 10:60 наносекунд. Это требование кроме всего прочего означает, что система основной памяти компьютера оказывается иногда недоступной процессору, так как она вынуждена рассылать сигналы регенерации каждой микросхеме. Разработчики DRAM стараются поддерживать время, затрачиваемое на регенерацию, на уровне менее 5% общего времени. Обычно контроллеры памяти включают в свой состав аппаратуру для периодической регенерации DRAM.

В процессе развития DRAM с ростом их емкости основным вопросом стоимости таких микросхем был вопрос о количестве адресных линий и стоимости соответствующего корпуса. Было принято решение о необходимости мультиплексирования адресных линий, позволившее сократить наполовину количество контактов корпуса, необходимых для передачи адреса. Поэтому обращение к DRAM обычно происходит в два этапа: первый этап начинается с выдачи сигнала RAS - row-access strobe (строб адреса строки), который фиксирует в микросхеме поступивший адрес строки, второй этап включает переключение адреса для указания адреса столбца и подачу сигнала CAS - column-access stobe (строб адреса столбца), который фиксирует этот адрес и разрешает работу выходных буферов микросхемы. Названия этих сигналов связаны с внутренней организацией микросхемы, которая как правило представляет собой прямоугольную матрицу, к элементам которой можно адресоваться с помощью указания адреса строки и адреса столбца.

Емкость DRAM по грубым оценкам в 4 - 8 раз превышает емкость SRAM, но SRAM имеют в 8 - 16 раз меньшую длительность цикла и большую стоимость. По этим причинам в основной памяти практически любого компьютера используется полупроводниковые микросхемы DRAM (для построения кэш-памяти при этом применяются SRAM). Естественно были и исключения, например, в оперативной памяти суперкомпьютеров компании Cray Research использовались микросхемы SRAM.

Стековая память

Стековая память является безадресной. Все ячейки памяти организованы по принципу "первым вошел - последним вышел" (LIFO). Реализовано это таким образом, что для операций с памятью доступна только 0-я ячейка.

Каждая операция записи, инициируемая сигналом обращения к памяти, приводит к тому, что записанные данные помещаются в 0 ячейку памяти. При этом все ранние записи в памяти слова автоматически сдвигаются на 1 адрес ниже. Операция чтения, инициируемая сигналом обращения, приводит к тому, что на выходе памяти формируется значение слова, находящиеся в 0 ячейке памяти. При этом все имеющиеся слова сдвигаются на одно слово вверх. Счетчик стека нужен только для контроля заполнения и очищения стека. Техническая реализация стековой памяти оказывается сложнее адресной памяти. Стековая память используется достаточно широко. Чаще всего применяется не стековая память, а адресное поле, которое функционирует по принципу стека.

Ассоциативная память.

Исторически последняя. Является представителем многофункциональных запоминающих устройств (возможна обработка данных без процессора в памяти). Отличительная особенность - поиск любой информации в ЗМ производится не по адресу, а по ассоциативным признакам (признакам опроса). Поиск производится одновременно по всем ячейкам ЗМ.

С точки зрения структуры, любая основная память компьютера может быть построена, как одноблочная, либо как многоблочная (сейчас одноблочная память практически не используется). Многоблочную память строят из однотипных блоков.

Иерархия памяти

В основе реализации иерархии памяти современных компьютеров лежат два принципа: принцип локальности обращений и соотношение стоимость/производительность. Принцип локальности обращений говорит о том, что большинство программ к счастью не выполняют обращений ко всем своим командам и данным равновероятно, а оказывают предпочтение некоторой части своего адресного пространства.

Иерархия памяти современных компьютеров строится на нескольких уровнях, причем более высокий уровень меньше по объему, быстрее и имеет большую стоимость в пересчете на байт, чем более низкий уровень. Уровни иерархии взаимосвязаны: все данные на одном уровне могут быть также найдены на более низком уровне, и все данные на этом более низком уровне могут быть найдены на следующем нижележащем уровне и так далее, пока мы не достигнем основания иерархии.

Иерархия памяти обычно состоит из многих уровней, но в каждый момент времени мы имеем дело только с двумя близлежащими уровнями. Минимальная единица информации, которая может либо присутствовать, либо отсутствовать в двухуровневой иерархии, называется блоком. Размер блока может быть либо фиксированным, либо переменным. Если этот размер зафиксирован, то объем памяти является кратным размеру блока.

Успешное или неуспешное обращение к более высокому уровню называются соответственно попаданием (hit) или промахом (miss). Попадание - есть обращение к объекту в памяти, который найден на более высоком уровне, в то время как промах означает, что он не найден на этом уровне. Доля попаданий (hit rate) или коэффициент попаданий (hit ratio) есть доля обращений, найденных на более высоком уровне. Иногда она представляется процентами. Доля промахов (miss rate) есть доля обращений, которые не найдены на более высоком уровне.

Поскольку повышение производительности является главной причиной появления иерархии памяти, частота попаданий и промахов является важной характеристикой. Время обращения при попадании (hit time) есть время обращения к более высокому уровню иерархии, которое включает в себя, в частности, и время, необходимое для определения того, является ли обращение попаданием или промахом. Потери на промах (miss penalty) есть время для замещения блока в более высоком уровне на блок из более низкого уровня плюс время для пересылки этого блока в требуемое устройство (обычно в процессор). Потери на промах далее включают в себя две компоненты: время доступа (access time) - время обращения к первому слову блока при промахе, и время пересылки (transfer time) - дополнительное время для пересылки оставшихся слов блока. Время доступа связано с задержкой памяти более низкого уровня, в то время как время пересылки связано с полосой пропускания канала между устройствами памяти двух смежных уровней.

Чтобы описать некоторый уровень иерархии памяти надо ответить на следующие четыре вопроса:

- Где может размещаться блок на верхнем уровне иерархии? (размещение блока).

- Как найти блок, когда он находится на верхнем уровне? (идентификация блока).

- Какой блок должен быть замещен в случае промаха? (замещение блоков).

- Что происходит во время записи? (стратегия записи).

Организация кэш-памяти

Сегодня кэш-память имеется практически в любом классе компьютеров, а в некоторых компьютерах - во множественном числе.

Рис. 8.4.

Принципы размещения блоков в кэш-памяти определяют три основных типа их организации:

- Если каждый блок основной памяти имеет только одно фиксированное место, на котором он может появиться в кэш-памяти, то такая кэш-память называется кэшем с прямым отображением (direct mapped). Это наиболее простая организация кэш-памяти, при которой для отображение адресов блоков основной памяти на адреса кэш-памяти просто используются младшие разряды адреса блока.

- Если некоторый блок основной памяти может располагаться на любом месте кэш-памяти, то кэш называется полностью ассоциативным (fully associative).

- Если некоторый блок основной памяти может располагаться на ограниченном множестве мест в кэш-памяти, то кэш называется множественно-ассоциативным (set associative). Обычно множество представляет собой группу из двух или большего числа блоков в кэше.

- Если множество состоит из n блоков, то такое размещение называется множественно-ассоциативным с n каналами (n-way set associative).

Диапазон возможных организаций кэш-памяти очень широк: кэш-память с прямым отображением есть просто одноканальная множественно-ассоциативная кэш-память, а полностью ассоциативная кэш-память с m блоками может быть названа m-канальной множественно-ассоциативной. В современных процессорах как правило используется либо кэш-память с прямым отображением, либо двух- (четырех-) канальная множественно-ассоциативная кэш-память.

У каждого блока в кэш-памяти имеется адресный тег, указывающий, какой блок в основной памяти данный блок кэш-памяти представляет. Эти теги обычно одновременно сравниваются с выработанным процессором адресом блока памяти.

Если общий размер кэш-памяти зафиксировать, то увеличение степени ассоциативности приводит к увеличению количества блоков в множестве, при этом уменьшается размер индекса и увеличивается размер тега.

При возникновении промаха, контроллер кэш-памяти должен выбрать подлежащий замещению блок. Польза от использования организации с прямым отображением заключается в том, что аппаратные решения здесь наиболее простые. На попадание проверяется только один блок и только этот блок может быть замещен. При полностью ассоциативной или множественно-ассоциативной организации кэш-памяти имеются несколько блоков, из которых надо выбрать кандидата в случае промаха.

При обращениях к кэш-памяти на реальных программах преобладают обращения по чтению. Все обращения за командами являются обращениями по чтению и большинство команд не пишут в память. Обычно операции записи составляют менее 10% общего трафика памяти. Желание сделать общий случай более быстрым означает оптимизацию кэш-памяти для выполнения операций чтения, однако при реализации высокопроизводительной обработки данных нельзя пренебрегать и скоростью операций записи.

Общий случай является и более простым. Блок из кэш-памяти может быть прочитан в то же самое время, когда читается и сравнивается его тег. Таким образом, чтение блока начинается сразу как только становится доступным адрес блока. Если чтение происходит с попаданием, то блок немедленно направляется в процессор. Если же происходит промах, то от заранее считанного блока нет никакой пользы, правда нет и никакого вреда.

Однако при выполнении операции записи ситуация коренным образом меняется. Именно процессор определяет размер записи (обычно от 1 до 8 байтов) и только эта часть блока может быть изменена. В общем случае это подразумевает выполнение над блоком последовательности операций чтение-модификация-запись: чтение оригинала блока, модификацию его части и запись нового значения блока. Более того, модификация блока не может начинаться до тех пор, пока проверяется тег, чтобы убедиться в том, что обращение является попаданием. Поскольку проверка тегов не может выполняться параллельно с другой работой, то операции записи отнимают больше времени, чем операции чтения.

Очень часто организация кэш-памяти в разных машинах отличается именно стратегией выполнения записи. Когда выполняется запись в кэш-память имеются две базовые возможности:

- сквозная запись (write through, store through) - информация записывается в два места: в блок кэш-памяти и в блок более низкого уровня памяти.

- запись с обратным копированием (write back, copy back, store in) - информация записывается только в блок кэш-памяти. Модифицированный блок кэш-памяти записывается в основную память только когда он замещается. Для сокращения частоты копирования блоков при замещении обычно с каждым блоком кэш-памяти связывается так называемый бит модификации (dirty bit). Этот бит состояния показывает был ли модифицирован блок, находящийся в кэш-памяти. Если он не модифицировался, то обратное копирование отменяется, поскольку более низкий уровень содержит ту же самую информацию, что и кэш-память.

Оба подхода к организации записи имеют свои преимущества и недостатки. При записи с обратным копированием операции записи выполняются со скоростью кэш-памяти, и несколько записей в один и тот же блок требуют только одной записи в память более низкого уровня. Поскольку в этом случае обращения к основной памяти происходят реже, вообще говоря требуется меньшая полоса пропускания памяти, что очень привлекательно для мультипроцессорных систем. При сквозной записи промахи по чтению не влияют на записи в более высокий уровень, и, кроме того, сквозная запись проще для реализации, чем запись с обратным копированием. Сквозная запись имеет также преимущество в том, что основная память имеет наиболее свежую копию данных. Это важно в мультипроцессорных системах, а также для организации ввода/вывода.

При промахе во время записи имеются две дополнительные возможности:

- разместить запись в кэш-памяти (write allocate) (называется также выборкой при записи (fetch on write)). Блок загружается в кэш-память, вслед за чем выполняются действия аналогичные выполняющимся при выполнении записи с попаданием. Это похоже на промах при чтении.

- не размещать запись в кэш-памяти (называется также записью в окружение (write around)). Блок модифицируется на более низком уровне и не загружается в кэш-память.

Обычно в кэш-памяти, реализующей запись с обратным копированием, используется размещение записи в кэш-памяти (в надежде, что последующая запись в этот блок будет перехвачена), а в кэш-памяти со сквозной записью размещение записи в кэш-памяти часто не используется (поскольку последующая запись в этот блок все равно пойдет в память).

Принципы организации основной памяти в современных ЭВМ

Основная память представляет собой уровень иерархии памяти. Основная память удовлетворяет запросы кэш-памяти и служит в качестве интерфейса ввода/вывода, поскольку является местом назначения для ввода и источником для вывода. Для оценки производительности основной памяти используются два основных параметра: задержка и полоса пропускания.

Задержка памяти традиционно оценивается двумя параметрами: временем доступа (access time) и длительностью цикла памяти (cycle time). Время доступа представляет собой промежуток времени между выдачей запроса на чтение и моментом поступления запрошенного слова из памяти. Длительность цикла памяти определяется минимальным временем между двумя последовательными обращениями к памяти.

Согласование производительности современных процессоров со скоростью основной памяти вычислительных систем остается на сегодняшний день одной из важнейших проблем. Методы повышения производительности за счет увеличения размеров кэш-памяти и введения многоуровневой организации кэш-памяти могут оказаться не достаточно эффективными с точки зрения стоимости систем. Поэтому важным направлением современных разработок являются методы повышения полосы пропускания или пропускной способности памяти за счет ее организации, включая специальные методы организации DRAM. При увеличении полосы пропускания памяти возможно увеличение размера блоков кэш-памяти без заметного увеличения потерь при промахах.

Основными методами увеличения полосы пропускания памяти являются:

- увеличение разрядности или "ширины" памяти,

- использование расслоения памяти,

- использование независимых банков памяти,

- обеспечение режима бесконфликтного обращения к банкам памяти,

- использование специальных режимов работы динамических микросхем памяти.

Виртуальная память и организация защиты памяти

Общепринятая в настоящее время концепция виртуальной памяти появилась достаточно давно. Она позволила решить целый ряд актуальных вопросов организации вычислений. Прежде всего, к числу таких вопросов относится обеспечение надежного функционирования мультипрограммных систем.

В любой момент времени компьютер выполняет множество процессов или задач, каждая из которых располагает своим адресным пространством. Было бы слишком накладно отдавать всю физическую память какой-то одной задаче, тем более, что многие задачи реально используют только небольшую часть своего адресного пространства. Поэтому необходим механизм разделения небольшой физической памяти между различными задачами. Виртуальная память является одним из способов реализации такой возможности. Она делит физическую память на блоки и распределяет их между различными задачами. При этом она предусматривает также некоторую схему защиты, которая ограничивает задачу теми блоками, которые ей принадлежат. Большинство типов виртуальной памяти сокращают также время начального запуска программы на процессоре, поскольку не весь программный код и данные требуются ей в физической памяти, чтобы начать выполнение.

Другой вопрос, тесно связанный с реализацией концепции виртуальной памяти, касается организации вычислений на компьютере задач очень большого объема. Если программа становилась слишком большой для физической памяти, часть ее необходимо было хранить во внешней памяти (на диске) и задача приспособить ее для решения на компьютере ложилась на программиста. Программисты делили программы на части и затем определяли те из них, которые можно было бы выполнять независимо, организуя оверлейные структуры, которые загружались в основную память и выгружались из нее под управлением программы пользователя. Программист должен был следить за тем, чтобы программа не обращалась вне отведенного ей пространства физической памяти. Виртуальная память освободила программистов от этого бремени. Она автоматически управляет двумя уровнями иерархии памяти: основной памятью и внешней (дисковой) памятью.

Кроме того, виртуальная память упрощает также загрузку программ, обеспечивая механизм автоматического перемещения программ, позволяющий выполнять одну и ту же программу в произвольном месте физической памяти.

Системы виртуальной памяти можно разделить на два класса: системы с фиксированным размером блоков, называемых страницами, и системы с переменным размером блоков, называемых сегментами.

Страничная организация памяти

В системах со страничной организацией основная и внешняя память (главным образом дисковое пространство) делятся на блоки или страницы фиксированной длины. Каждому пользователю предоставляется некоторая часть адресного пространства, которая может превышать основную память компьютера, и которая ограничена только возможностями адресации, заложенными в системе команд. Эта часть адресного пространства называется виртуальной памятью пользователя. Каждое слово в виртуальной памяти пользователя определяется виртуальным адресом, состоящим из двух частей: старшие разряды адреса рассматриваются как номер страницы, а младшие - как номер слова (или байта) внутри страницы.

Управление различными уровнями памяти осуществляется программами ядра операционной системы, которые следят за распределением страниц и оптимизируют обмены между этими уровнями. При страничной организации памяти смежные виртуальные страницы не обязательно должны размещаться на смежных страницах основной физической памяти. Для указания соответствия между виртуальными страницами и страницами основной памяти операционная система должна сформировать таблицу страниц для каждой программы и разместить ее в основной памяти машины. При этом каждой странице программы, независимо от того находится ли она в основной памяти или нет, ставится в соответствие некоторый элемент таблицы страниц. Каждый элемент таблицы страниц содержит номер физической страницы основной памяти и специальный индикатор. Единичное состояние этого индикатора свидетельствует о наличии этой страницы в основной памяти. Нулевое состояние индикатора означает отсутствие страницы в оперативной памяти.

Для увеличения эффективности такого типа схем в процессорах используется специальная полностью ассоциативная кэш-память, которая также называется буфером преобразования адресов (TLB translation-lookaside buffer). Хотя наличие TLB не меняет принципа построения схемы страничной организации, с точки зрения защиты памяти, необходимо предусмотреть возможность очистки его при переключении с одной программы на другую.

Поиск в таблицах страниц, расположенных в основной памяти, и загрузка TLB может осуществляться либо программным способом, либо специальными аппаратными средствами. В последнем случае для того, чтобы предотвратить возможность обращения пользовательской программы к таблицам страниц, с которыми она не связана, предусмотрены специальные меры. С этой целью в процессоре предусматривается дополнительный регистр защиты, содержащий описатель (дескриптор) таблицы страниц или базово-граничную пару. База определяет адрес начала таблицы страниц в основной памяти, а граница - длину таблицы страниц соответствующей программы. Загрузка этого регистра защиты разрешена только в привилегированном режиме. Для каждой программы операционная система хранит дескриптор таблицы страниц и устанавливает его в регистр защиты процессора перед запуском соответствующей программы.

Отметим некоторые особенности, присущие простым схемам со страничной организацией памяти. Наиболее важной из них является то, что все программы, которые должны непосредственно связываться друг с другом без вмешательства операционной системы, должны использовать общее пространство виртуальных адресов. Это относится и к самой операционной системе, которая, вообще говоря, должна работать в режиме динамического распределения памяти. Поэтому в некоторых системах пространство виртуальных адресов пользователя укорачивается на размер общих процедур, к которым программы пользователей желают иметь доступ. Общим процедурам должен быть отведен определенный объем пространства виртуальных адресов всех пользователей, чтобы они имели постоянное место в таблицах страниц всех пользователей. В этом случае для обеспечения целостности, секретности и взаимной изоляции выполняющихся программ должны быть предусмотрены различные режимы доступа к страницам, которые реализуются с помощью специальных индикаторов доступа в элементах таблиц страниц.

Следствием такого использования является значительный рост таблиц страниц каждого пользователя. Одно из решений проблемы сокращения длины таблиц основано на введении многоуровневой организации таблиц. Частным случаем многоуровневой организации таблиц является сегментация при страничной организации памяти. Необходимость увеличения адресного пространства пользователя объясняется желанием избежать необходимости перемещения частей программ и данных в пределах адресного пространства, которые обычно приводят к проблемам переименования и серьезным затруднениям в разделении общей информации между многими задачами.

Сегментация памяти

Другой подход к организации памяти опирается на тот факт, что программы обычно разделяются на отдельные области-сегменты. Каждый сегмент представляет собой отдельную логическую единицу информации, содержащую совокупность данных или программ и расположенную в адресном пространстве пользователя. Сегменты создаются пользователями, которые могут обращаться к ним по символическому имени. В каждом сегменте устанавливается своя собственная нумерация слов, начиная с нуля.

Обычно в подобных системах обмен информацией между пользователями строится на базе сегментов. Поэтому сегменты являются отдельными логическими единицами информации, которые необходимо защищать, и именно на этом уровне вводятся различные режимы доступа к сегментам. Можно выделить два основных типа сегментов: программные сегменты и сегменты данных (сегменты стека являются частным случаем сегментов данных). Из программных сегментов допускается только выборка команд и чтение констант. Запись в программные сегменты может рассматриваться как незаконная и запрещаться системой. Выборка команд из сегментов данных также может считаться незаконной, и любой сегмент данных может быть защищен от обращений по записи или по чтению.

Для реализации сегментации было предложено несколько схем, которые отличаются деталями реализации, но основаны на одних и тех же принципах.