| Скачать .docx |

Реферат: Присвоение блока памяти оперативного запоминающего устройства

Федеральное агентство образования Российской Федерации

Государственное образовательное учреждение

среднего профессионального образования

Краснотурьинский индустриальный колледж

Специальность:

Вычислительные машины, комплексы, системы и сети

Курсовой проект по предмету конструкция, производство на тему:

Присвоение блока памяти оперативного запоминающего устройства

Введение

Основной целью курсового проекта является формирование навыков и умение проектировать устройства вычислительной техники.

Курсовой проект предоставляет основные возможности:

-научиться анализировать техническое задание на проектирование устройств ЭВТ.

усвоить основные понятия и термины, относящиеся к проектированию схемы управления ОЗУ.

-познакомиться с основными проектными процедурами разработки схем.

-закрепить и углубить знания по схемотехники ОЗУ.

Курсовая работа должна способствовать расширению и углублению знаний о тактовых элементах цифровых устройств, основных ИМС памяти, логических основах ЭВМ.

1. Описание используемых элементов

1.1 Микросхема памяти КР537РУ3

Рисунок 1. Условное графическое обозначение КР573РУ3

SRAM 4K x 4 бит. Запись и чтение асинхронные ((СE) ̅= 0. (WE) ̅= 0 — запись с переводом выхода DO в Z-состояние. Что позволяет объединить вход DI и выход DO для организации двунаправленной шины данных: (СE) ̅= 0, (WE) ̅= 1 — чтение данных; (СE) ̅=1 — Z-состояние выхода DO)

1.2 Микросхема дешифратора К155ИДЗ

К155ИДЗ- дешифратор, позволяющий преобразовать четырехразрядный код, поступающий на входы АО-АЗ в напряжение низкого логического уровня, появляющееся на одном из шестнадцати выходов 0-15. Дешифратор имеет два входа разрешения дешифрации СЕ1 и СЕ2. Эти входы можно использовать как логические, когда дешифратор ИДЗ служит демультиплексором данных. Тогда входы АО-A3, используются как адресные, чтобы направить поток данных, принимаемых входами СЕ1 или СЕ2, на один из выходов 0-15. На второй, не используемый в этом включении вход Е, следует подать напряжение низкого уровня.

По входам СЕ1 и СЕ2 даются сигналы разрешения выходов, чтобы устранять текущие выбросы, которыми сопровождается дешифрация кодов, появляющихся не строго синхронно. Чтобы разрешить прохождение данных на выходы, на входы СЕ1 и СЕ2 следует дать напряжение низкого уровня. Эти входы необходимы также при наращивании числа разрядов дешифрируемого кода. Когда на входах СЕ1 и СЕ2 присутствуют напряжения высокого уровня, на выходах 0-15 появляются высокие уровни.

Выбор контроллера по конкретному адресу осуществляется с помощью дешифратора К155ИДЗ (рис. 2). Назначение его выводов показано в таблице 2.

Рисунок 2. Условное графическое обозначение К155ИДЗ.

Таблица 1. Назначение выводов К155ИДЗ

| № вывода | Назначение | № вывода | Назначение |

| 1 | Выход 0 | 13 | Выход 11 |

| 2 | Выход 1 | 14 | Выход 12 |

| 3 | Выход 2 | 15 | Выход 13 |

| 4 | Выход 3 | 16 | Выход 14 |

| 5 | Выход 4 | 17 | Выход 15 |

| 6 | Выход 5 | 18 | Вход стробирующий |

| 7 | Выход 6 | 19 | Вход стробирующий |

| 8 | Выход 7 | 20 | Вход информационный |

| 9 | Выход 8 | 21 | Вход информационный |

| 10 | Выход 9 | 22 | Вход информационный |

| 11 | Выход 10 | 23 | Вход информационный |

| 12 | Общий | 24 | Ucc |

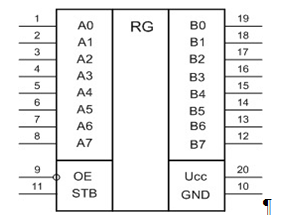

1.3 Буферный регистр КР580ИР82

КР580ИР82 представляет собой 8-разрядный буферный регистр, предназначенный для ввода и вывода информации со стробированием. Микросхема имеет восемь триггеров D-типа и восемь выходных буферов, имеющих на выходе состояние "выключено". Управление передачей информации осуществляется с помощью сигнала STB "строб".

При поступлении на вход STB сигнала высокого уровня осуществляется нетактируемая передача информации от входа DI до выхода DO. При подаче на вход STB сигнала низкого уровня микросхема хранит информацию предыдущего такта; при подаче на вход STB положительного перепада импульса происходит "защелкивание" входной информации. Выходные буферы управляются сигналом ОЕ "разрешение выхода". При поступлении на вход ОЕ сигнала высокого уровня выходные буферы переводятся в состояние "выключено".

Рисунок 3. Условное графическое обозначение КР580ИР82.

Таблица 2. Назначение выводов КР580ИР82.

| Номер вывода | Обозначение | Назначение |

| 1-8 | A0-A7 | Вход регистра |

| 9 | OE | Разрешение выхода |

| 10 | GND | Общий |

| 11 | STB | Строб |

| 12-19 | D00-D07 | Выходы регитра |

| 20 | Ucc | Питание |

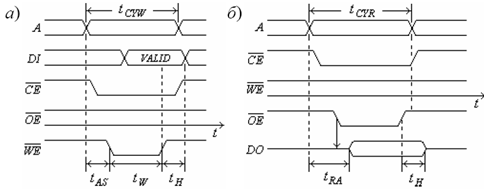

Рис. а и б - Временные диаграммы записи и чтения данных

На рис а приведены временные диаграммы для режима записи информации, а на рис. 6 — для режима чтения. На дешифрацию адреса требуется время ![]() (Address Sen/p Time — время установки адреса), только после истечения которого можно подавать

(Address Sen/p Time — время установки адреса), только после истечения которого можно подавать

активный уровень сигнала разрешения записи ![]() (иначе данные могут быть записаны по неправильному адресу).

(иначе данные могут быть записаны по неправильному адресу).

Минимальная длительность ![]() активного уровня сигнала

активного уровня сигнала ![]() определяется быстродействием ячеек памяти. Часто требуется сохранение значений входных данных DI некоторое время

определяется быстродействием ячеек памяти. Часто требуется сохранение значений входных данных DI некоторое время ![]() (Data Hold Time — время удержания данных) после окончания активного уровня сигнала записи

(Data Hold Time — время удержания данных) после окончания активного уровня сигнала записи ![]() = 0. В современных SRAM обеспечиваются минимальные значения

= 0. В современных SRAM обеспечиваются минимальные значения ![]() = 0 и

= 0 и ![]() = 0. Длительность цикла записи

= 0. Длительность цикла записи ![]() (Write Cycle Time) примерно равна сумме значений

(Write Cycle Time) примерно равна сумме значений ![]() ,

, ![]() и

и ![]() .

.

При чтении время ![]() (Read Access Time — время доступа при чтении) характеризует задержку выходных данных DO относительно изменения адресных сигналов при отсутствии сигнала управления

(Read Access Time — время доступа при чтении) характеризует задержку выходных данных DO относительно изменения адресных сигналов при отсутствии сигнала управления ![]() или

или ![]() ≡ 0. Время

≡ 0. Время ![]() характеризует удержание значений выходных данных DO по окончании активного уровня сигнала управления

характеризует удержание значений выходных данных DO по окончании активного уровня сигнала управления ![]() = 0 (или адресного сигнала

= 0 (или адресного сигнала ![]() при отсутствии сигнала

при отсутствии сигнала ![]() ). Если сигнал управления

). Если сигнал управления ![]() имеется, то выходные данные DO могут появиться только при значении

имеется, то выходные данные DO могут появиться только при значении ![]() = 0. Время задержки выходных данных DO относительно изменения сигнала управления

= 0. Время задержки выходных данных DO относительно изменения сигнала управления ![]() с 1 на 0 значительно меньше значения

с 1 на 0 значительно меньше значения ![]() .Время цикла чтения

.Время цикла чтения![]() примерно равно времени цикла записи

примерно равно времени цикла записи ![]() При равенстве этих циклов основной динамической характеристикой SRAM является время цикла

При равенстве этих циклов основной динамической характеристикой SRAM является время цикла ![]() .

.

2. Расчётная часть

2.1 Определение числа микросхем

1)Расчёт ОЗУ в битах

Nбис = Nr * Nc

Где Nr – число ячеек памяти БИС ОЗУ,

Nc – Разрядность БИС ОЗУ.

NБИС =4·1024·4=16384

2) Рассчитаем всего блока ОЗУ заданного по курсовому проекту 65536 байт в битах.

Nозу = 8кБ * 1024 * 8 = 65536 Бит.

3) Определим количество микросхем памяти для построения всего блока ОЗУ по формуле:

Qram = Nозу/Nбис

Где Nозу – объём всего блока ОЗУ,

Nбис – объём ОЗУ.

Qram = 524288/16384=32

4)Рассчитаем количество микросхем памяти для одного банка для хранении:

N1 = Nшд / Nc

Где Nщд – разрядность ШД,

N1 – разрядность микросхемы памяти.

N1 = 8 / 4 = 2.

5)Рассчитаем количество банков требуемых для блока ОЗУ по формуле:

N2 = Qram / N1

Где N1 – количество микросхем в банке,

Qram – количество микросхем памяти.

N2 = 32/2=16

2.2 Расчет адресного пространства

64·1024=65536

65536-1=65535=>FFFF=>1111111111111111- 16 линий адреса для построения ОЗУ.

Таблица 3. Адреса блоков памяти

| Номер блока | Адресный диапазон | |

| Шестнадцатеричный | десятичный | |

| Банк 0 | 0-FFF | 0-4095 |

| Банк 1 | 1000-1FFF | 4096-8191 |

| Банк 2 | 2000-2FFF | 8192-12287 |

| Банк 3 | 3000-16383 | 12288-16383 |

| Банк 4 | 4000-4FFF | 16384-20479 |

| Банк 5 | 5000-5FFF | 20480-24575 |

| Банк 6 | 6000-6FFF | 24576-28671 |

| Банк 7 | 7000-7FFF | 28672-32767 |

| Банк 8 | 8000-8FFF | 32768-36863 |

| Банк 9 | 9000-9FFF | 36864-40959 |

| Банк 10 | A000-AFFF | 40960-45055 |

| Банк 11 | B000-BFFF | 45056-49151 |

| Банк 12 | C000-CFFF | 49152-53247 |

| Банк 13 | D000-DFFF | 53248-57343 |

| Банк 14 | E000-EFFF | 57344-61439 |

| Банк 15 | F000-FFFF | 61440-65535 |

3.Структурная схема

Рисунок 4. Структурная схема

Шина адреса (ША) подключается к регистру (РГ) для мультиплексирования, затем подключается ко входам дешифратора (ДШ) для реализации выбора микросхем памяти. Так же ША подключается к СОЗУ для адресации.

Шина данных (ШД) подключается к микросхемам памяти статических оперативно запоминающих устройств (СОЗУ). Сигнал ALE подключается к регистру.

4. Принципиальная схем.

Таблица 4. Перечень элементов.

| № | Обозначение на схеме | Тип элемента |

| 1 | XC | Разъём |

| 2 | DD1,DD2 | Регистры (микросхемы КР580ИР 82) |

| 3 | DD3 | Дешифраторы (микросхема К555ИД3) |

| 4 | DD4, DD5 | СОЗУ (микросхема КР573РУ3) |

Разъем XC имеет 21 контакт, содержащих линии адреса А8 , линии данных D7, сигнал записи W/R. Все линии адреса разъема XC подключены к линиям адресов регистров и СОЗУ, так же подключены линии данных. Сигнал записи W/R подключен к микросхемам СОЗУ для записи данных. Входной сигнал СЕ0подключается к инверсным сигналам СЕ0 СОЗУ. А СЕ1 и СЕ2 к дешифратору. Выходы дешифратора подключены к СОЗУ.

Заключение

В данном курсовом проекте построен блок статического ОЗУ .

Содержанием курсового проекта является расчёт количества микросхем памяти, распределение Адресного пространства, построение структурной и принципиальной электрической схемы управления ОЗУ.

Курсовой проект является заключительным этапом в изучении общепрофессиональных и специальных дисциплин:

“Математические и логические основы ЭВТ”,

“Типовые элементы и устройства цифровой техники”.

Список используемой литературы

1. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Справочник – М.: Радио и связь, 1990-304 с.

2. Лебедев О.Н. Применение микросхем памяти в электронных устройствах: Справочное пособие. – М.: Радио и связь, 1994-216 с.