| Скачать .docx |

Курсовая работа: Расчет буквенно-цифрового дисплея

Содержание

Введение

1. Выбор и обоснование структурной схемы устройства.

2. Расчет числа знаков на экране системы.

3. Расчет буферного запоминающего устройства

4. Выбор мультиплексора.

5. Расчет ПЗУ знакогенератора.

6. Выбор регистра знакогенератора.

7. Выбор компаратора.

8. Расчет блока формирования маркера.

9. Расчет устройства синхронизации.

10. Разработка схемы формирования КГИ и КСИ.

Заключение.

Список литературы.

Введение

В настоящее время цифровые технологии развиваются с очень большой скоростью. Поэтому компьютерные системы с каждым днем обрабатывают все больше и больше информации. Но для правильной обработки необходимо активное взаимодействие с человеком (оператором) компьютерной системы.

Так как человек максимум информации воспринимает через зрительный канал, то качество систем отображения информации очень сильно влияет на количество воспринимаемой информации, а так же на утомляемость.

Поэтому лучше работа СОИ тем активнее происходит взаимодействие человека и компьютера.

В данной работе мы будем производить расчет СОИ. Ознакомимся с принципами построения устройств данного типа.

1 Выбор и обоснование структурной схемы устройства

Средства отображения информации служат для преобразования информации, полученной от одного или нескольких источников информации (ИИ ), в информационную модель, удобную для восприятия оператором.

Функциональная схема СОИ телевизионного типа изображена на рисунке 1.

Информационный массив заносится через устройство интерфейса ( УИ ) в буферное запоминающее устройство ( БЗУ ) и адресная информация ( m ), которая поступает на счетчик маркера:

СчМтс – счетчик маркера знаков ( формирует младшие разряды( r ) адреса);

СчМтс – счетчик маркера текстовых строк ( формирует старшие k-r разрядов);

MS – мультиплексор ( служит для переключения адресной информации, поступающей от счетчиков маркера и счетчиков регенерации);

СчЗН – счетчик знаков;

СчТС – счетчик текстовых строк.

Адресная информ с выхода MS поступает на экранную память(видеопамять)

ЗГ – знакогенератор ( преобразует код знака в последовательность в виде импульсов, формирующих на экране знак).

БЗУ ( экранная память ) хранит коды знака в объеме одной или нескольких экранных страниц. Коды знаков БЗУ располагаются в порядке в каком они будут выводится на экран при формировании изображения.

ЛЗ – линия задержки ( задерживает сигнал чтения записи БЗУ на время срабатывания MS с тем, чтобы адрес на входе БЗУ был стабильным на момент чтения или записи ).

Устройство синхронизации состоит из ГТИ ( генератора тактовых импульсов, вырабатывает частоту fтг), D(делитель) – делит частоту fтг до частоты знаков

fзн= fтг /(b’з+b’п), счетчик регенерации( СчЗН, СчТС ), счетчик Z – счетчик рядов матрицы знака ( формирует младшие разряды адреса, поступающее на ПЗУ знакогенератора для развертки знака по вертикали).

СФСИГИ – схема формирования синхро и гасящих сигналов вырабатывает следующие сигналы:

ССИ – строчный синхроимпульс;

СГИ – строчный гасящий импульс;

КСИ – кадровый синхроимпульс;

КГИ – кадровый гасящий импульс.

Импульсы поступают на сумматор, одновременно туда поступает видеосигнал (ВС) и сигнал с выхода формирования маркера (ФМ) .

На выходе сумматора образуется полный видеосигнал

С помощью УИ осуществляется электрическое и алгоритмическое согласование между собой выходных цепей ИИ и выходных цепей СОИ.

Рисунок 1 – Функциональная схема устройства отображения информации

2 Расчет числа знаков на экране системы

Расчет количества знаков, которые можно сформировать на экране

средства отображения информации (СОИ):

![]()

где ![]() – количество телевизионных строк;

– количество телевизионных строк;

![]() – коэффициент обратного хода кадровой развертки;

– коэффициент обратного хода кадровой развертки;

![]() – коэффициент использования растра по вертикали;

– коэффициент использования растра по вертикали;

![]() – количество телевизионных линий в одном элементе изображения.

– количество телевизионных линий в одном элементе изображения.

Расчет количества текстовых строк:

![]()

где ![]() – высота знака;

– высота знака;

![]() – высота промежутка между знаками.

– высота промежутка между знаками.

Расчет количества элементов в текстовой строке:

![]()

где ![]() – коэффициент формы экрана, для стандартного телевизионного экрана

– коэффициент формы экрана, для стандартного телевизионного экрана ![]() ;

;

![]() – коэффициент использования растра по вертикали;

– коэффициент использования растра по вертикали;

![]() – коэффициент использования растра по горизонтали.

– коэффициент использования растра по горизонтали.

Расчет количества знаков в текстовой строке:

![]()

где ![]() – ширина знака;

– ширина знака;

![]() – ширина промежутка между знаками.

– ширина промежутка между знаками.

Расчет количества знаков в кадре:

![]()

Расчет частоты тактового генератора

Время развертки одного элемента равно:

![]()

где: ![]() с

- период строчной развертки

с

- период строчной развертки

![]()

Расчет верхней граничной частоты в полосе пропускания:

![]()

3 Расчет буферного запоминающего устройства

Хранит коды символов, которые будут отображаться на экране.

Коды символов в буферном запоминающем устройстве (БЗУ) располагаются в том порядке, в каком они будут выводиться.

Исходные данные для расчета:

число текстовых строк Nтс =9,6;

число знаков в текстовой строке Nзтс =65,5;

основание кода алфавита Nа =30;

Находим требуемую разрядность БЗУ

![]()

где ![]() – разрядность обеспечения алфавита;

– разрядность обеспечения алфавита;

![]() – разрядность обеспечения признаков.

– разрядность обеспечения признаков.

По заданию

![]() ,

,![]() .

.

![]()

Выбираем требуемое число адресных разрядов

Адресация двух координатная:

младшие разряды адреса поступают от счетчика знаков маркера (регенерации);

старшие разряды адреса поступают от счетчика текстовых строк маркера (регенерации).

![]()

![]() – количество младших разрядов адреса

– количество младших разрядов адреса

![]()

![]() – количество старших разрядов адреса.

– количество старших разрядов адреса.

минимальное число адресных разрядов К=12.

Расчет числа ячеек памяти БЗУ

Количество ячеек памяти определяется по следующей формуле:

![]()

Следовательно:

![]() бит

бит

Определим требуемое быстродействие БИС ОЗУ относительно адреса:

![]() .

.

Выбираем БИC ОЗУ:

По быстродействию, информационной ёмкости, и организации подходит микросхема ОЗУ КР537РУ16А, имеющая информационную емкость СБИС = 8к´8, NБИС =8k, nБИС =8. Такая организация обеспечивает минимальное число интегральных схем в модуле при минимальной избыточности. Особенностью этой микросхемы является двунаправленный вход-выход с тремя устойчивыми состояниями

| Справочные данные микросхемы: | |

| Входной ток логического нуля IIDL | не менее 0,4 мА |

| Входной ток логической единицы IIDH | не более 0,04 мА |

| Входная емкость по информационному входу БИС CID | не более 4 пФ |

| Время выборки адреса tBA | не более 60 нс |

| Потребляемая мощность | 880 мВт |

Рассчитываем число БИС ОЗУ в ряду матрицы, необходимое для получения двенадцати разрядного информационного слова:

![]() .

.

Определим число рядов матрицы:

![]() .

.

Общее число БИС ОЗУ:

![]() .

.

Такое количество БИС ОЗУ обеспечивает объем памяти

СБЗУ =8к x16 бит.

Полученная избыточность определяется тем, что NЗУ в данном случае не кратно NБИС .

Определяем токовую IDL и IDH и емкостные Cd нагрузки для схем ввода информации в ОЗУ по формулам (mc = 1– число рядов матрицы , p = 2 – общее число микросхем):

![]()

![]()

![]()

Определим токи нагрузки и величину емкостной нагрузки на информационные выходы БИС ОЗУ по формулам:

![]()

![]()

Где IQ У T = 20μА – ток утечки невыбранного выхода;

IОУ T = 20мкА – ток утечки схем ввода информации;

![]()

CQO =10 pF – выходная емкость одного информационного выхода БИС ОЗУ.

CmQ =10 pF – монтажная емкость цепи информационного

CО Q =20 pF – выходная емкость схем ввода информации.

Полученные значения токов и емкостей нагрузки удовлетворяют соответствующим требованиям для ИС серии КР537.

Определяем токи нагрузки и емкостную нагрузку по адресным цепям БИС ОЗУ по формулам:

![]()

![]()

![]()

Для схем серии КР537 указанная нагрузка допустима.

Рассчитаем потребляемую мощность БЗУ.

Потребляемая мощность БИС КМ132РУ13А 880mW.

Поэтому потребляемая мощность ОЗУ:

РБЗУ =2∙0,880= 1760 (W).

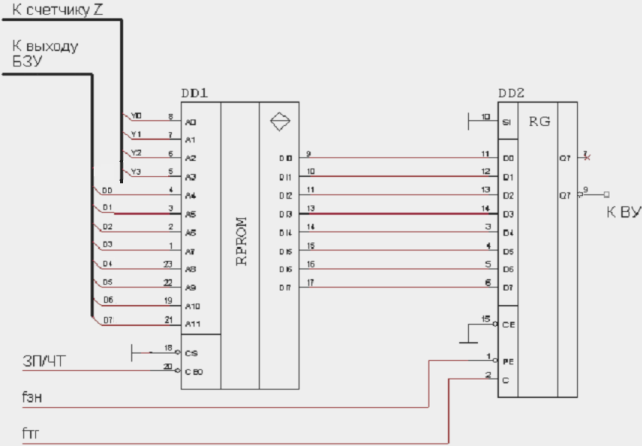

Рисунок 2 – Принципиальная электрическая схема БЗУ

4 Выбор мультиплексора

Мультиплексор – устройство, осуществляющее коммутацию цифровых сигналов с n информационных входов на один выход. В нашем случае n =3 (необходимо коммутировать на адресную шину БЗУ содержимое счетчиков маркера или счетчиков регенерации).

В нашем случае необходимо коммутировать 12 цифровых (бинарных) сигналов.

В качестве мультиплексора применим микросхему К555КП11, содержащую в одном корпусе 4 мультиплексора из двух направлений в одно. В связи с тем, что нам необходимо коммутировать 12 цифровых сигналов, используем 3 микросхемы К555КП11.

Микросхема К555КП11 имеет следующие параметры:

–Мин. вых. напряжение высокого уровня,В 2,5

–Макс. вых. напряжение низкого уровня,мВ 480

–Макс. вх. ток высокого уровня,мкА 20

–Макс. вх. ток низкого уровня,мкА 760

–Макс. ток потребления,мА 9,7

–Напряжение источника питания,В 5

–Временная задержка распред. сигнала, нс 21

Рисунок 3 – Принципиальная электрическая схема мультиплексора

5 Расчет ПЗУ знакогенератора

Для хранения информации о графике каждого знака требуется 7 ячеек памяти с разрядностью 10.

В связи с тем, что число адресуемых ячеек памяти должно быть кратно степени 2, на каждый знак приходится 2пу ячеек памяти.

Определим число ячеек памяти ПЗУ, необходимое для размещения в нем всех знаков алфавита:

Необходимая информационная ёмкость ПЗУ:

![]() ,

,

где ![]() — разрядность адресных входов, необходимая для адресации рядов матрицы знака.

— разрядность адресных входов, необходимая для адресации рядов матрицы знака.

![]() ,

,

![]() .

.

![]()

В качестве ПЗУ выбираем электрически программируемую БИС КР1656РЕ3.

| Справочные данные микросхемы: | |

| Информационная ёмкость: | С = 32768 бит |

| Организация: | 4k´8 |

| Время выборки относительно адреса | tВА не более 50 нс |

| Напряжение питания | UСС = +5 В ± 5 % |

| Ток потребления | Iпот = 90 мА |

Для полноценной работы знакогенератора достаточно одной микросхемы ПЗУ КР1656РЕ3.

Количество знаков, которое можно разместить в выбранную БИС:

![]() .

.

Таким образом, выбранная БИС удовлетворяет заданию, так как ![]()

6 Выбор регистра знакогенератора

Так как разрядность сдвигового регистра должна быть не менее b’З =8, то в качестве регистра выбираем восьмиразрядный знаковый регистр К555ИР9, имеющий параллельные и последовательные входы. Параллельно данные загружаются в регистр через входы D0-D7 асинхронно, если на вход разрешения параллельной загрузки РЕ подается напряжение низкого уровня. Если на входе РЕ присутствует напряжение высокого уровня, то данные вводятся в регистр через последовательный вход S1. Сдвиг данных вправо на одну позицию происходит согласно каждому положительному перепаду тактового импульса на входе С . Вход разрешения тактовым импульсам СЕ имеет активный низкий уровень. Регистр имеет комплиментарные выходы Q7 и Q7. Микросхема К555ИР9 потребляет ток 63 мА.

Рисунок 4 – Принципиальная электрическая схема знакогенератора

7 Выбор компаратора

Компараторы кодов служат для сравнения двух многоразрядных двоичных слов. В разрабатываемом устройстве отображения информации компаратор формирует единичный сигнал при равенстве кодов с выхода счетчиков регенерации и счетчиков маркера.

Применим четырехразрядный компаратор кодов К555СП1 – микросхему средней степени интеграции. Требуется построить 12-разрядный компаратор, следовательно, будет использоваться 4 микросхемы К555СП1 (последовательный режим наращивания). Время задержки сигнала одной микросхемой – 15 нс, следовательно, составной 11-разрядный компаратор задерживает сигнал на 45 нс.:

![]() ,

,

где ![]() – время задержки распространения сигнала одним компаратором;

– время задержки распространения сигнала одним компаратором;

n – количество микросхем.

Рисунок 5 – Принципиальная схема компаратора

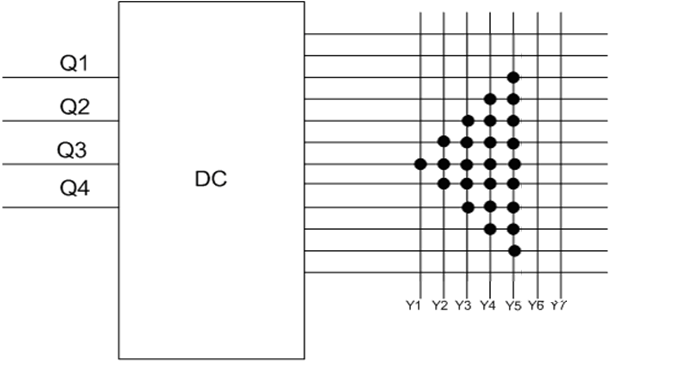

8 Расчет блока формирования маркера

Рисунок 6. Форма маркера и дешифратор.

Составим карты Карно для нахождения функций Y1 , Y2 , Y3 , Y4 , Y5 .

| Y1 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 0 | 0 |

| 01 | 0 | 1 | 0 | 0 |

| 11 | X | X | X | X |

| 10 | 0 | 0 | 0 | 0 |

| Y2 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 0 | 0 |

| 01 | 1 | 1 | 0 | 1 |

| 11 | X | X | X | X |

| 10 | 0 | 0 | X | X |

| Y3 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 1 | 0 |

| 01 | 1 | 1 | 1 | 1 |

| 11 | X | X | X | X |

| 10 | 0 | 0 | X | X |

| Y4 | 00 | 01 | 11 | 10 |

| 00 | 0 | 0 | 1 | 1 |

| 01 | 1 | 1 | 1 | 1 |

| 11 | X | X | X | X |

| 10 | 1 | 0 | X | X |

| Y5 | 00 | 01 | 11 | 10 |

| 00 | 0 | 1 | 1 | 0 |

| 01 | 1 | 1 | 1 | 1 |

| 11 | X | X | X | X |

| 10 | 1 | 1 | X | X |

Y5= Q1+ Q2+ Q3 +4

![]()

![]()

![]() Y4

= Q4 Q3+Q2 Q3 Q4

Y4

= Q4 Q3+Q2 Q3 Q4

![]()

![]()

![]() Y3=

Q3 Q4+ Q1Q2Q3Q4

Y3=

Q3 Q4+ Q1Q2Q3Q4

![]()

![]()

![]()

![]() Y2=

Q2 Q3 Q4+Q1Q2Q3Q4

Y2=

Q2 Q3 Q4+Q1Q2Q3Q4

![]()

![]() Y1=

Q1

Q2

Q3

Q4

Y1=

Q1

Q2

Q3

Q4

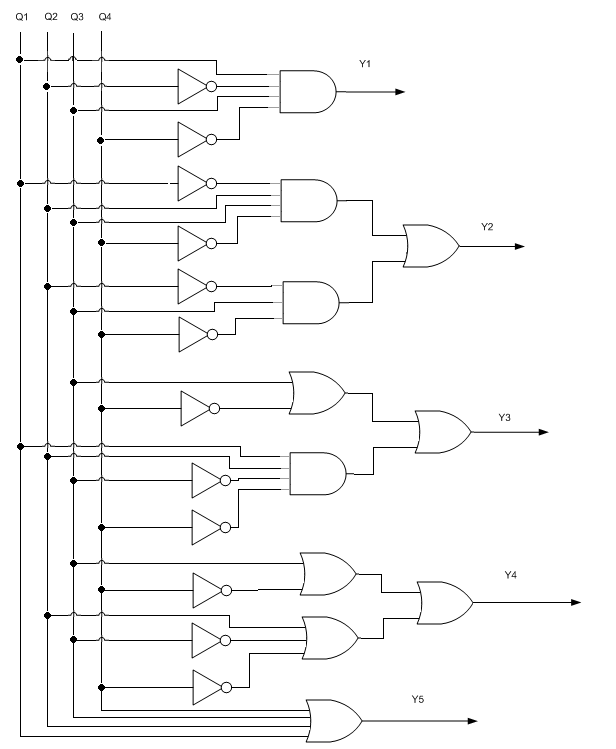

Рисунок 7 – Функциональная схема формирователя маркера

9 Расчет устройства синхронизации

Исходные даные:

Число знаков в строке Nзтс=65,5

Число текстовых строк Nтс=9,6

Матрица знака 7 х 10

Интервалы между знаками и текстовыми строками ![]()

![]()

Коэффициент использования телевизионного растра по горизонтали и вертикали bг=0,9; bв=0,8;

Коэффициент обратного хода строчной и кадровой разверток

![]()

![]()

Длительность прямого хода развертки в безразмерной форме

![]()

Период строчной развертки

![]()

Для удобства получения коэффициента деления примем

![]()

![]()

Из этих величин для затемнения с левой и правой сторон экрана выделяем по 5 знакомест. Начало отсчета взято с первого знакоместа, входящего в информационное поле.

Определим коэффициент деления D2 по формуле:

![]()

Построим делитель на 11 при помощи микросхемы К555ИЕ5. Сигнал сброса должен быть получен при комбинации 1100 на выходе.

Коэффициент деления ![]() реализуем на двух четырехразрядных десятичных счетчиках DD2 и DD3 типа К555 ИЕ5. Счетчик DD2 работает в режиме деления на 10 (комбинация 1010), а DD3 в режиме деления на 8 (комбинация 1000), что обеспечивается соответствующими сигналами сброса.

реализуем на двух четырехразрядных десятичных счетчиках DD2 и DD3 типа К555 ИЕ5. Счетчик DD2 работает в режиме деления на 10 (комбинация 1010), а DD3 в режиме деления на 8 (комбинация 1000), что обеспечивается соответствующими сигналами сброса.

Формирование требуемой длительности и временного положения СГИ и ССИ осуществляется с помощью программируемого ПЗУ DD4.

Рисунок 8 – Делитель и формирователь СГИ и ССИ. Схема структурная.

10 Разработка схемы формирования КГИ и КСИ

Расчет данного блока полностью аналогичен предыдущему расчету. В этом случае имеем следующее:

![]()

![]()

Для удобства принимаем nКпр равный 80.

Из этих размеров для затемнения сверху и снизу возьмем по две текстовые строки. Построение данного блока производим по тому же принципу, что и для предыдущего. Таким образом, коэффициент деления делителя частоты тактового генератора определяется следующим выражением:

![]()

Построим делитель на 20 при помощи двух микросхем К555ИЕ5. На первой микросхеме организуем делитель на 4 и на второй микросхеме делитель на 4.

Коэффициент деления ![]() реализуем на двух четырехразрядных десятичных счетчиках DD2 и DD3 типа К555 ИЕ5. Счетчик DD2 работает в режиме деления на 7 (комбинация 0111), а DD3 в режиме деления на 6 (комбинация 0110) что обеспечивается соответствующими сигналами сброса.

реализуем на двух четырехразрядных десятичных счетчиках DD2 и DD3 типа К555 ИЕ5. Счетчик DD2 работает в режиме деления на 7 (комбинация 0111), а DD3 в режиме деления на 6 (комбинация 0110) что обеспечивается соответствующими сигналами сброса.

Формирование требуемой длительности и временного положения КГИ и КСИ осуществляется с помощью программируемого ПЗУ DD4.

Тогда принципиальная схема разрабатываемого блока будет иметь вид, приведенный на рисунке 9:

Рисунок 9 – Схема электрическая принципиальная делителя-формирователя КГИ и КСИ

Вывод

В ходе работы была разработана система отображения информации в соответствии с заданным вариантом. Данная система имеет очень простую структуру, малое экранное разрешение, возможно отображение только текстовой информации. Алфавит текста ограничен. Данные ограничения накладываются на устройство из-за его функционального назначения, стоимости, а так же отображаемой информации.Поэтому, применение подобных систем отображения информации оправданно лишь в производственных условиях.

При расчете узлов СОИ ознакомились с принципами проектирования данных узлов, научились выбирать элементы устройств (память, компаратор, мультиплексор, счетчики).