| Скачать .docx |

Реферат: Структура та класифікація 8-розрядних мікропроцесорів

Структура та класифікація 8-розрядних мікропроцесорів

8-розрядні мікропроцесори і МП комплекти, такі як МПК КР580, МП Z80 та К1821МВ85 сьогодні досить широко використовуються в периферійних керуючих пристроях, системах технічного обслуговування та діагностики вузлів зв’язку.

Особливістю мікропроцесорного комплекту КР580 є його універсальність. Хоч сам процесор КР580ВМ80 у нових розробках не використовується, більшість інтерфейсних БІС цього комплекту (або їх найближчих аналогів) використовуються в сучасних пристроях, вже з іншими процесорами. Вивчення комплекту доцільно починати з центрального процесора.

Структурна схема МП КР580 складається з АЛП, блока регістрів загального призначення, схеми керування та синхронізації та буферів шин.

Особистістю блока регістрів КР580 є функціональна спеціалізація його окремих елементів.

PC - регістр лічильника команд використовується для зберiгання адреси елемента пам’яті, з якого вибиратиметься наступна команда. При виконанні лінійної програми вміст лічильника команд послідовно збільшується. При виконанні команд переходів або викликів підпрограм лічильник команд встановлюється відповідно з вказаною адресою.

SP - регістр стека використовується для указання на текучу вершину стеку, він використовується для організації повернення з підпрограм і для часового зберігання в ОЗП вмісту регістрових пар (наприклад параметрів підпрограми).

Регістри загального призначення - В,С,D,E. Програмісту надана можливість запису і читання інформації з цих регістрів, а також видачі цієї інформації на шину даних.

HL - регістр указника адреси може використовуватись для тієї ж мети, що і регістри загального призначення, а може використовуватись для формування адреси в командах з непрямою адресацією.

Регістр ознак (прапорців) уявляє собою набір тригерів, які показують результат останньої операції, що виконав АЛП. За допомогою регістра F реалізується організація умовних переходів у МП КР580. В цьому регістрі є п’ять умовних ознак, які змінюють своє значення в результаті виконання різних арифметичних і логічних команд: ознаки нуля Z, знаку S, парності Р, переносу CY і допоміжного переносу AC. Ознаку встановлено, якщо біт дорівнює 1, ознаку скинуто, якщо він дорівнює 0. Ознака нуля встановлюється, якщо результат операції дорівнює 0, скидається, якщо результат не дорівнює 0.

При вивченні системи команд будь-якого мікропроцесора треба зосередити увагу на трьох важливих аспектах - розглянути формати команд, режими адресації та групи команд.

В системі команд МП КР580ВЕ80 є одно-, дво- і трибайтні команди. Формат команди і режим адресації задаються в команді кодом операції. Код операції завжди стоїть на першому місці і в процесорі, що розглядається, займає 1 байт. Далі, залежно від режиму адресації, може йти 1 байт даних, 1 байт адреси порту, 2 байти даних чи 2 байти адреси в ОЗП чи ПЗП. При прямій або непрямій регістровій адресації команда складається з одного байта – коду операції, і кожний з регістрів вибирається з допомогою 3 бітів в цьому байті.

Приклади однобайтних команд:

MOV C, D - переслати з D в C;

ADD M- A=A+B;

RET - повернення з підпрограми;

HLT - команда зупинки.

Приклади двобайтних команд:

MVI A, байт - загрузити байт (00-FF) в А;

ANI байт - логічно помножити акумулятор на байт (00-FF);

IN адр_порта - ввести дані з порту aдр_порта (00-FF) в А.

Приклади трибайтних команд:

JMP адреса- перейти до виконання команди з вказаною адресою (0000-FFFF);

CALL адреса - визвати підпрограму з вказаною адресою (0000-FFFF),

LXI H, 2 байти - загрузити до регістрової пари HL 2 байти даних.

МП КР580ВМ80 має шість різних засобів адресації даних, що зберігаються в пам’яті або в регістрах: неявна, регістрова, безпосередня, пряма, не пряма, регістрова, стекова.

В двоадресних командах можливо використання комбінації вказаних видів адресації, тобто один із операндів (частіше за все акумулятор) може бути заданим неявно, а другий - явно.

Команди розглядуваного мікропроцесора можна розділити на 5 груп: команди пересилання (передачі даних), арифметичні, логічні, передачі керування (розгалуження), спеціальні.

До команд пересилки відносяться команди MOV, MVI, LXI, LDA, STA, LDAX, STAX, PUSH, POP, IN, OUT.

До арифметичних команд відносяться команди ADD, DAD, ADC, ADI, SUB, SUI, INR, INX, DCR, DCX.

До логічних команд та зсувів відносяться команди ANA, ANI, ORA, ORI, XRA, XRI, RAR, RRC, RAL, RLC.

До команд передачі керування відносяться команди безумовного переходу JMP та умовних переходів JZ, JNZ, JC, JNC, JP, JM (за 4 прапорцями регістру ознак), виклику підпрограм CALL, RET та ін.

До спеціальних команд відносяться команди NOP – пуста операцїя, HLT - зупинка, EI – дозвіл переривань, DI – заборона переривань.

При виконанні команд умовних переходів передача керування здійснюється за прапорцями регістру ознак, які встановлюються попередньою командою.

Команда СALL спочатку автоматично зберігає в стеку адресу повернення, а далі завантажує вказану адресу в лічильник команд (РС).

Команда повернення RET містить в лічильник команд останнє записане у стеку число (тобто витягає адресу повернення). Після цього виконання головної програми продовжується з цiєї адреси.

Мікропроцесор Z80 є закінченим однокристальним мікропроцесором з фіксованою системою команд. МП оперує 8 розрядними словами (байтами) і може адресувати 64 К пам’яті і до 64 К портів. Система команд МП Z80 є розширенням системи команд процесора КР580ВМ80А. Крім того МП Z80 має розширену шину керування, що полегшує підключення до нього інших ВІС. Однофазна синхронізація і однополярна напруга живлення спрощує синхронізацію всієї системи, побудованої на його підставі. В МП є вбудовані сигнали для вибірки мікросхем пам’яті і пристроїв вводу-виводу. Пам’ять має байтову структуру – можлива адресація в пам’яті будь-якого байта.

Організація МП Z80 має такі основні особливості:

- тришинна структура з шинами адреси, даних і керування;

- магістральний принцип побудови, реалізований у вигляді двоспрямованої шини даних, яка зв’язує основні вузли МП та має ширину, що дорівнює довжині слів, що обробляє мікропроцесор (8 розрядів);

- наявність 16-розрядної шини адреси, яка забезпечує можливість прямої адресації будь-якого байта в пам’яті ємністю 64 К;

- наявність регістрової пам’яті, у вигляді програмно доступних загальних і спеціалізованих регістрів, а також регістрів тимчасового зберігання;

- наявність двох (головного і допоміжного) акумуляторів, регістрів ознак і подвоєного набору РЗП;

- наявність засобів організації стекової пам’яті (регістр - вказівник стека, схеми виконання операцій інкременту, декременту, спеціальні команди операцій зі стеком);

- наявність 10 засобів адресації, таких як: безпосередня, регістрова, непряма, абсолютна, модифікована нуль сторінкова, відносна, індексна, бітова, вбудована і змішана;

- спрощеними схемами інтерфейсу в МП режиму прямого доступу до пам’яті шляхом підключення спеціальної ВІС (контролера ПДП);

- відсутність необхідності в додаткових ВІС, таких як, наприклад, системний контролер для МП 8080;

- наявність вбудованої схеми регенерації динамічного ОЗП;

- спрощені схеми інтерфейсу та відлагодження.

Архітектура МП Z80 є типовою для 8-розрядних мікропроцесорів. В нiй можна виділити такі основні частини: блок регістрів, арифметично-логічний пристрій, регістр команд, дешифратор команд та пристрій керування, схеми керування шинами адреси і даних. Блок регiстрів містить програмно-доступні 8-розрядні регістри: регістр-акумулятор, загальні регістри, регістр ознак і 16-розрядні спеціалізовані регістри.

До складу мікропроцесорного комплекту КР580 входить значна кількість програмованих і непрограмованих ВІС. Найбільш важливі з них:

КР580ВГ24 – генератор тактових сигналів;

КР580ВК28 - системний контролер; непрограмовані ВІС;

КР580ВА86 - шинний формувач;

КР580ВВ51 - програмований послідовний (зв’язковий) адаптер;

КР580ВИ53 - програмований інтервальний таймер;

КР580ВВ55 - програмований паралельний адаптер;

КР580ВТ57 - контролер прямого доступу до пам’яті;

КР580ВН59 - контролер переривань;

КР580ВТ79 - контролер відеотерміналу;

КР580ВМ80 - центральний процесор.

Перші три з перелічених мікросхем - непрограмовані ВІС, що використовуються для формування шин МП пристрою на базі КР580ВМ80, в першу чергу тих керуючих сигналів, які процесор не виробляє – сигналів тактової синхронізації, стробу, роздільних сигналів звертання до пам’яті та портів.

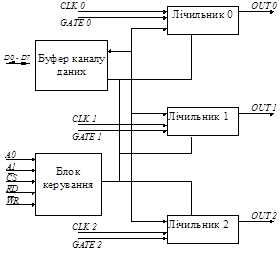

ВІС КР580ВИ53 використовується у МП системах для реалізації часових функцій. Ця ВІС, по суті, є триканальним програмованим інтервальним таймером (ПІТ). Програмування режимів роботи каналів здійснюється індивідуально і у вільному порядку, шляхом вводу спочатку керуючих бітів у регістри режимів каналів, потім потрібного числа байтів у лічильники. Лічильники виконують відрахунок від записаного в них числа до нуля і виробляють вихідні сигнали в залежності від встановленого режиму роботи.

Схема ВІС КР580ВИ53 наведена на рис 1. Сигнали C0 - C3 – це вхідні сигналі тактової синхронізації лічильників, СЕ0 - СЕ3 – сигнали дозволу рахування, OUT0 – OUT3 – вихідні сигнали лічильників. До буфера каналу даних підключається шина даних, до блока керування – декотрі сигнали шини адреси та керування, що потрібні для керування роботою цієї ВІС.

В залежності від режиму роботи низький рівень на входах СЕ0 - СЕ3 припиняє (режими 0,2,4), чи повністю зупиняє рахунок.

ПІТ може функціонувати в таких режимах:

0 – термінальний рахунок; в цьому режимі лічильник відраховує від записаного значення до нуля і на виході формується логічна одиниця;

1 – на виході очiкуючого мультивібратора формується позитивний імпульс тривалістю n Тс, де n – число, записане у лічильник, Тс – період тактової частоти. Після цього формується негативний короткий імпульс. Потім процес повторюється.

2 – генератор імпульсів – таймер працює як подільник імпульсів на число, що записане в лічильник.

3 – аналогічний режиму 2 крім того, що тривалість вихідних сигналів для парних чисел на Тс менш ніж для непарних.

4 – одиночний програмний строб – по закінченнi рахунку, на виході формується негативний імпульс тривалістю Тс.

5 – одиночний апаратний строб – аналогічний режиму 4 за виключенням того, що передавач виробляється автоматично.

Рисунок 1 – Структурна схема ВІС КР580ВИ53

ВІС програмованого паралельного інтерфейсу КР580ВВ55 призначена для організації вводу-виводу паралельної інформації різного формату і дозволяє реалізувати більшість відомих протоколів обміну за паралельними каналами. ВІС програмованого паралельного інтерфейсу може використовуватись для спряження мікропроцесорного пристрою з периферійним обладнанням або для організації внутрішньосистемних магістралей, наприклад, у цифрових АТС.

У склад ВІС входять: двоспрямований 8-розрядний буфер даних; блок керування записом-читанням; три 8-розрядних канали вводу-виводу; схема керування групою А (керує каналом А і старшими розрядами каналу С ); схема керування групою В (керує каналом В і молодшими розрядами каналу С ).

Режим роботи кожного із каналів програмується за допомогою керуючого слова. Керуюче слово може задати один із трьох режимів: основний режим вводу-виводу ( режим 0 ), режим стробуємого вводу-виводу ( режим 1), режим двоспрямованої передачі інформації ( режим 2 ). Одним керуючим словом можна встановити різні режими роботи для кожного із каналів.

Канал А може працювати в будь-якому із трьох режимів, канал В – в режимах 0 і 1. Канал С може бути використано для передачі даних тільки в режимі 0, а в інших режимах він потрібний для передачі керуючих сигналів, які супроводжують процес обміну по каналам А і В.

Режим 0 використовується при синхронному обміні або при програмній організації асинхронного обміну. Мікросхема може розглядатись в цьому режимі як пристрій, який складається, з чотирьох портів ( два 8-розрядних і два 4-розрядних ), що незалежно настроюються на ввід або вивід.

Режим 1 забезпечує стробуючий односпрямований обмін інформацією з зовнішнім пристроєм. Передача даних виконується по каналам А і В, а лінії каналу С керують передачею. Роботу каналу в режимі 1 супроводжують три керуючих сигнали. Якщо один з каналів запрограмувати на режим 1, то інші 13 інтерфейсних ліній можна використати в режимі 0. Якщо обидва канали запрограмовані на режим 1, то останні дві інтерфейсні лінії каналу С можуть бути настроєні на ввід або вивід.

Режим 2 забезпечує двоспрямовану передачу інформації по каналу А до зовнішнього пристрою і зворотно. Процес обміну супроводжують п’ять керуючих сигналів, що подаються лініями РС7-РС3. Останні 11 інтерфейсних ліній можуть ладнатися на режим 0 або режим 1.

ВІС КР580ИК51 уявляє собою універсальний синхронно–асинхронний прийомопередавач (УСАПП). Він може приймати дані з 8-розрядної шини даних мікропроцесора і передавати їх в послідовному форматі периферійним пристроям, а також отримати дані від периферії і перетворювати їх в паралельну форму для передачі в мікропроцесор.

Обмін даними виконується в асинхронному режимі зі швидкістю до 9,6 Кбіт/с або в синхронному – зі швидкістю до 56 Кбіт/с. Довжина символів, що передаються складає від 5 до 8 біт. При передачі в мікропроцесор символів довжиною менш 8 біт невикористані біти замінюються нулями. Формат символу мiстить також службові біти і необов’язковий біт контролю по парності (непарності).

Режим роботи УСАПП задається програмно шляхом завантаження в нього керуючих слів з мікропроцесора. Відрізняють керуючі слова двох видів: інструкцій режиму і команди. Інструкція режиму задає синхронний або асинхронний режим роботи, формат даних, швидкість прийому або передачі, необхідність контролю. Вона посилається відразу після установлення УСАПП у початковий стан програмно або за сигналом RESET і замінюється лише при необхідності зміни режиму. Керуюче слово команди встановлює керування режимом обміну і може багаторазово задаватись в процесі обміну, керуючі різними його етапами.

При асинхронному обміні команда завантажується відразу після інструкції режиму, а при синхронному обміні перед нею розташовуються один або два синхросимволи.

В асинхронному режимі роботи формат даних містить нульовий старт-біт, біти даних, контрольний біт і стоп-біти. Число бітів даних і стоп-бітів, а також наявність або відсутність біта контролю задаються інструкцією режиму.

При синхронному обміні дані передаються у вигляді масивів слів, а для синхронізації запуску при прийомі даних використовується один або два символи синхронізації.

Після запису інструкції режиму і команди УСАПП готовий до виконання обміну даними в одному з п’яти режимів: синхронна передача; синхронний прийом з внутрішньою синхронізацією; синхронний прийом з зовнішньою синхронізацією; асинхронна передача; асинхронний прийом.

ВІС програмованого контролера прямого доступу до пам’яті (ПДП) реалізує функції апаратурно-керуючого обміну даними між основною пам’яттю і зовнішніми пристроями (частіше за все iз зовнішньою пам’яттю на магнітному носії). Контролер може керувати в режимі ПДП передачею інформації побайтно, послівно і блоками даних. З цією метою КПДП формує і модифікує адреси, які приймають участь в передачах елементів ПЗП, веде підрахунок байт, які передаються, виявляє момент закінчення передачі. КПДП настроюється на той чи інший режим роботи з використанням керуючого слова.

Контролер ПДП має чотири незалежних канали ПДП, до складу кожного з яких входять: 16-розрядний регістр адреси, 14-розрядний лічильник довжини блоку даних і 2-розрядний регістр режиму каналу.

КПДП може знаходитись в двох станах - відомого і ведучого. На етапі ініціалізації КПДП є веденим. При сигналі на вході ВК (CS) =0 мікропроцесор завантажує в ВТ57 початкові адреси областей ПЗП, розміри блоків даних і коди режимів. Одразу після ініціалізації КПДП переходить в режим ведучого. В режимі ведучого ВТ57 сам формує сигнали DBIN і WR, виробляє сигнал "запит захвату шин" HOLD і, при появі відповідного сигналу HLDA, видає на шину адреси елементів ПЗП і зовнішніх пристроїв, між якими виконується обмін. Сигнал ВК при цьому блокується.

ВІС програмованого контролера переривань (ПКП) призначена для використання в МП системах, в яких режим обробки інформації має змінюватись в залежності від зовнішніх програмно-непередбачених подій. Основна функція ПКП зводиться до впізнання зовнішніх подій і видачі керуючих сигналів мікропроцесора, який ( при дозволу переривань) припиняє виконання існуючої програми і переходить до виконання програми обробки переривань.

Контролер реалізує керування перериваннями від 8 джерел. Кількість зовнішніх джерел, що обслуговуються, може бути збільшено до 64 шляхом каскадного підключення контролерів (один - ведучий, вісім - ведених). Приклад каскадного підключення двох ПКП зображений на рис. 2.

Контролер ініціюється під керуванням програми і з використанням керуючих слів може бути налаштований для роботи в одному із чотирьох режимів: векторне переривання з фіксованим пріоритетом, векторне переривання з циклічним перерозподілом пріоритетів, векторне переривання з адресуючим розподілом пріоритетів, переривання за результатом опиту.

Рисунок 2. - Схема каскадного підключення двох контролерівпереривань до шин 8-розрядного МП пристрою

Для приведення ПКП в робочий стан прикладна програма має завантажити в нього два або три керуючих слів ініціалізації, які виявляють наявність в системі одного або декількох ПКП, початкову адресу масиву підпрограм обслуговування переривань, інтервал розташування початкових адрес підпрограм в пам’яті системи та типи розподілу пріоритетов при одночасному надходженні переривань з двох джерел.

Вузол клавіатури і індикації можна організувати по-різному.

По-перше, для виводу даних на 7-сегментні індикатори і вводу з клавіатури можна використовувати ППІ КР580ВМ80. Але при цьому такі функції, як усування дріб’язку клавіатури або регенерація відображення на індикаторах, треба виконувати програмним шляхом.

По-друге, можна використовувати спеціалізовану ВІС – контролер індикатора і клавіатури КР580ВД79, до складу якої входять схеми усування дріб’язку клавіатури і динамічної індикації.

Крім цього, увід із клавіатури можна здійснювати за перериваннями, а вивід на індикацію – з допомогою схем прямого доступу в пам’ять, коли для зберігання образу на дисплеї відводиться конкретний масив елементів в ПЗП.