| Скачать .docx |

Реферат: Контрольная работа: Счетчик команд. Регистр DPTR. Память. Порты

Счетчик команд. Регистр DPTR . Память. Порты

Счетчик команд (PC) предназначен для формирования текущего 16-разрядного адреса программной памяти и 8/16-разрядного адреса внешней памяти данных.

В состав счетчика команд входят 16-разрядные буфер PC, регистр указателя данных DPTR, регистр PC, схема инкремента, регистр адреса памяти.

Буфер PC осуществляет связь между 16-разрядной шиной PC к восьмиразрядной магистралью данных, обеспечивая запись, хранение и коммутацию информации.

Регистр указателя данных (DPTR) предназначен для хранения 16-разрядногс адреса внешней памяти данных. Состоит из двух восьмиразрядных регистров DPH и DPL, входящих в блок регистров специальных функций. Они программно доступны и могут использоваться в качестве двух независимых РОН, если нет необходимости в хранении 16-разрядного адреса внешней памяти данных. В регистре PC хранится текущий 16-разрядный адрес памяти программ. Схема инкремента увеличивает текущее значение 16-разрядного адреса памяти программ на единицу.

Регистр адреса памяти предназначен для записи и хранения исполнительного 16-разрядного адреса памяти программ или 8/16-разрядного адреса внешней памяти данных, а также для передачи данных на порт Р0 при выполнении команд MOVX @Ri, А и MOVX @DPTR, А, обеспечивающих запись данных через порт Р0 во внешние устройства через порты Р0, Р1, Р2, РЗ.

Порты Р0, Р1, Р2, РЗ являются двунаправленными портами ввода-вывода и предназначены для обеспечения обмена информацией ОМЭВМ с внешними устройствами, образуя 32 линии ввода-вывода. Каждый из портов содержит фиксатор-защелку, который представляет собой восьмиразрядный регистр, имеющий байтовую и битовую адресацию для установки (сброса) разрядов с помощью программного обеспечения.

Физические адреса фиксаторов Р0, Р1, Р2, РЗ составляют для:

Р0 — 80Н, при битовой адресации 80Н—87Н;

Р1 — 90Н, при битовой адресации 90Н—97Н;

Р2 — А0Н, при битовой адресации А0Н—А7Н;

РЗ — В0Н, при битовой адресации В0Н—В7Н.

Помимо работы в качестве обычных портов ввода/вывода линии портов Р0—РЗ могут выполнять ряд дополнительных функций, описанных ниже.

Через порт Р0:

— выводится младший байт адреса А0—А 7 при работе с внешней памятью программ и внешней памятью данных;

— выдается из ОМЭВМ и принимается в ОМЭВМ байт данных при работе с внешней памятью (при этом обмен байтом данных и вывод младшего байта адреса внешней памяти мультиплексированы во времени);

— задаются данные при программировании внутреннего ППЗУ и читается содержимое внутренней памяти программ.

Через порт Р1:

— задается младший байт адреса при программировании внутреннего ППЗУ и при чтении внутренней памяти программ.

Через порт Р2:

— выводится старший байт адреса А 8—А15 при работе с внешней памятью программ и внешней памятью данных (для внешней памяти данных — только при использовании команд MOVXA,@DPTR и MOVX @DPTR,A, которые вырабатывают 16-разрядный адрес);

— задается старший байт (разряды А8—А14) адреса при программировании внутреннего ППЗУ и при чтении внутренней памяти программ.

Каждая линия порта РЗ имеет индивидуальную альтернативную функцию:

РЗ. 0 — RxD, вход последовательного порта, предназначен для ввода последовательных данных в приемник последовательного порта;

РЗ. 1 — TxD, выход последовательного порта, предназначен для вывода последовательных данных из передатчика последовательного порта;

РЗ. 2 — INT0, используется как вход 0 внешнего запроса прерывания;

РЗ. 3 — INT1, используется как вход 1 внешнего запроса прерывания;

РЗ. 4 — Т0, используется как вход счетчика внешних событий Т/С 0;

РЗ. 5 — Т 1, используется как вход счетчика внешних событий Т/С 1;

РЗ. 6— WR, строб записи во внешнюю память данных, выходной сигнал, сопровождающий вывод данных через. порт Р0 при использовании команд MOVX @Ri,A и MOVX @DPTR, А.

РЗ. 7 — RD, строб чтения из внешней памяти данных, выходной сигнал, сопровождающий ввод данных через порт Р0 при использовании команд MOVXA,@Ri и MOVX A,@DPTR.

Альтернативная функция любой из линий порта РЗ реализуется только в том случае, если в соответствующем этой линии разряде фиксатора-защелки содержится "1". В противном случае на линии порта РЗ будет присутствовать "0".

Электрические параметры портов Р0—РЗ приведены в табл 1. Выход триггера Q может быть подключен на внутреннюю шину ОМЭВМ через буфер В1 сигналом "Чтение защелки", что обеспечивая возможность программного чтения содержимого фиксатора. Значение сигнала непосредственно на выводе порта может быть программно считано па внутреннюю шину ОМЭВМ через буфер В2, управляемый внутренним сигналом "Чтение выводов". Часть команд ОМЭВМ при чтении порта активизируют сигнал "Чтение защелки", другая часть команд — сигнал "Чтение выводов".

Выходные каскады порта Р0 (образованы транзисторами Nl, N) и порта Р2 (образованы транзисторами Nl, N2, N) через мультиплексоры MX могут подключаться либо к выходу защелок, либо к внутренним шинам "Адрес/данные" и "Адрес". Последнее используется при обращении к внешней памяти. Во время обращения к внешней памяти содержимое защелок порта Р2 не изменяется. В аналогичной ситуации в защелки порта Р0 всегда автоматически записываются "1" во все разряды.

Если защелка вывода порта РЗ содержит "1", то выходным каскадом управляет внутренний сигнал обеспечивающий выполнение соответствующей альтернативной функции. Если альтернативная функция предполагает, что данный вывод порта РЗ является входом, то значение уровня сигнала на нем поступает на внутреннюю линию "Альтернативная функция входа".

Все выводы портов Р1, Р2 и РЗ имеют внутренние подключенные к питанию подтягивающие резисторы. Каждый вывод указанных портов может независимо от других использоваться как вход или как выход. Для использования вывода в качестве входа необходимо, чтобы его защелка содержала "1", которая при этом запирает выходной транзистор N. Из-за наличия внутреннего подтягивающего резистора выводы портов Р1, Р2, РЗ в режиме "оборванный вход" имеют уровень "1". Благодаря этой особенности порты Р1, Р2, РЗ иногда называют "квазидвунаправленными".

Порт Р0 не имеет внутренних подтягивающих резисторов. Транзистор N1 в выходном каскаде выводов порта Р0 открыт только когда через эти выводы выдается "1" при обращениях к внешней памяти. Во всех других режимах работы транзистор NI заперт. Таким образом, в случае использования порта Р0 в качестве выходного порта общего назначения, необходимо устанавливать на его выводах внешние подтягивающие резисторы для задания уровня "1". Запись "1" в защелку вывода порта Р0 закрывает транзистор N и при отсутствии внешнего подтягивающего резистора переводит вывод в высокоимпедансное состояние. При этом данный вывод может использоваться в качестве входа. Если порт Р0 используется в качестве порта ввода/вывода общего назначения, каждый из его выводов может независимо от других работать как вход или как выход. Порт Р0 является в чистом виде двунаправленным портом.

Все разряды фиксаторов-защелок портов Р0—РЗ по сбросу устанавливаются в" 1". Если защелка вывода порта содержит "0", то для настройки данного вывода на ввод необходимо записать в защелку "1".

При выполнении команды записи в порт новое значение записывается в защелку в фазе S6P2 последнего машинного цикла команды. Однако, новое содержимое защелки выводится непосредственно на выходной контакт порта только в фазе S1P1 следующего машинного цикла.

При переходе выводов портов Р1, Р2 и РЗ из состояния "0" в состояние "1" для уменьшения времени переключения используется дополнительный транзистор N1, который включается на время, равное двум периодам tbq тактовой частоты ОМЭВМ fBQ (транзистор N1 открыт в течение фаз S1P1 и S1P2 машинного цикла, в котором происходит смена состояния вывода порта). В открытом состоянии транзистор N1 обеспечивает ток приблизительно в 100 раз больший, чем постоянно открытый транзистор N2.

Рассматриваемый выходной каскад содержит три р-канальных МОП транзистора (Р1, Р2, РЗ), подключенных к источнику питания, и один п-МОП транзистор, подключенный к общей шине. Можно отметить, что п-МОП транзисторы, используемые в выходных каскадах ОМЭВМ серий 1816 и 1830 открыты, когда на их затворах логическая "1" и закрыты, когда на их затворах логический "0". р-МОП транзисторы, наоборот, открыты, когда на их затворах "0" и закрыты, когда на затворах "1".

Транзистор Р1 на рис. 2 включается на два периода TBQ для уменьшения времени переключения при переходе вывода порта из состояния "0" в состояние "1". Как только открывается транзистор Р1, сигнал с выхода порта через инвертор поступает на затвор транзистора РЗ и также открывает его. Этот инвертор и транзистор РЗ образуют триггер, который удерживает состояние логической "1" на выходе порта после того, как транзистор Р1 закрывается.

Для предотвращения подобной ситуации служит транзистор Р2, работающий в противофазе с транзистором N. После исчезновения помехи транзистор Р2 через инвертор вновь откроет транзистор РЗ. Мощность транзистора Р2 приблизительно в 10 раз меньше мощности транзистора РЗ.

Команды чтения портов ОМЭВМ делятся на две категории: команды, считывающие информацию с выходов защелок, и команды, считывающие информацию непосредственно с внешних контактов выводов порта. Команды, считывающие информацию с выходов защелок, реализуют так называемый режим "Чтение— Модификация—Запись", заключающийся в том, что команда считывает состояние защелки, при необходимости модифицирует полученное значение и записывает результат обратно в защелку.

Ниже приводятся команды, работающие в режиме "Чтение—Модификация-Запись". Во всех случаях, когда операндом и регистром назначения результата является порт или бит порта, команды считывают информацию с выходов защелок, а не с внешних контактов выводов порта. ANL (логическое И, например, ANL Р1, А) ORL (логическое ИЛИ, например, ORL Р2,А) XRL (логическое ИСКЛЮЧАЮЩЕЕ ИЛИ, например, XRL РЗ,А) JBC (переход, если бит = 1 и очистка бита, например, JBC Р1 .I,LABEL) CPL (инверсия бита, например, CPL РЗ. 0) INC (инкремент, например, INC Р2) DEC (декремент, например, DEC Р2)

DJNZ декремент и переход, если не ноль, например, DJNZ РЗ,LABEL) MOV РХ. Y, С (пересылка бита переноса в бит Y порта X) CLR РХ. Y (очистка бита Y порта X) SETB РХ. Y (установка бита Y порта X)

Не очевидно, что последние три команды в приведенном списке работают в режиме "Чтение—Модификация—запись", однако, это так. Указанные команды] считывают с порта весь байт целиком, модифицируют адресуемый бит, после чеу записывают полученный новый байт обратно в фиксатор-защелку порта.

Чтение информации с выходов защелок, а не с внешних контактов выводов порта позволяет исключить возможную в ряде случаев неправильную интерпретацию уровня напряжения на выводе порта. К примеру, вывод порта может использоваться для управления базой п-р-п транзистора. В этом случае, когда в защелку вывода порта записывается "1", транзистор открывается. Если после этого ОМЭВМ прочитает состояние внешнего контакта рассматриваемого вывода порта, то получит значение логического "0", т. к. на контакте в это время присутствует напряжение базы открытого транзистора. Чтение же выхода защелки покажет истинное значение сигнала на выводе порта, т. е."1" из памяти данных.

Память данных предназначена для приема, хранения и выдачи информации, используемой в процессе выполнения программы. Память данных, расположенная на кристалле ОМЭВМ, состоит из регистра адреса ОЗУ, дешифратора, ОЗУ и указателя стека.

Регистр адреса ОЗУ предназначен для приема и хранения адреса выбираемой с помощью дешифратора ячейки памяти, которая может содержать как бит, так и байт информации.

ОЗУ представляет собой 128 восьмиразрядных регистров, предназначенных для приема, хранения и выдачи различной информации.

Указатель стека представляет собой восьмиразрядный регистр, предназначенный для приема и хранения адреса ячейки стека, к которой было последнее обращение. При выполнении команд LCALL, ACALL содержимое указателя стека увеличивается на 2. При выполнении команд RET, RETI содержимое указателя стека уменьшается на 2. При выполнении команды PUSHdirect содержимое указателя стека увеличивается на 1. При выполнении команды POPdirect содержимое указателя стека уменьшается на 1. После сброса в указателе стека устанавливается адрес 07Н, что соответствует началу стека с адресом 08Н.

В ОМЭВМ предусмотрена возможность расширения памяти данных путем подключения внешних устройств емкостью до 64 Кбайт. При этом обращение к внешней памяти данных возможно только с помощью команд MOVX.

Команды MOVX @Ri,A и MOVXA,@Ri формируют восьмиразрядный адрес, выдаваемый через порт Р0. Команды MOVX ©DPTR.A и MOVX ©A.DPTR формируют 16-разрядный адрес, младший байт которого выдается через порт Р0, а старший — через порт Р2.

Байт адреса, выдаваемый через порт Р0, должен быть зафиксирован во внешнем регистре по спаду сигнала ALE, т. к. в дальнейшем линии порта Р0 использутся как шина данных, через которую байт данных принимается из памяти при чтении или выдается в память данных при записи. При этом чтение пробируется сигналом ОМЭВМ RD, а запись — сигналом ОМЭВМ WR. При работе с внутренней памятью данных сигналы RD и WR не формируются, а является основой памяти программ.

Память программ предназначена для хранения программ и имеет отдельное от памяти данных адресное пространство объемом до 64 Кбайт, причем, для микросхем КР1816ВЕ51, КМ1816ВЕ751 и для КР183ОВЕ51 часть памяти программ с адресами 0000Н—0FFFHрасположена на кристалле ОМЭВМ. Память программ, расположенная на кристалле, состоит из 12-разрядного дешифратора и ПЗУ емкостью 4К*8 бит для микросхем КР1816ВЕ51, КР183ОВЕ51 или ППЗУ с ультрафиолетовым стиранием емкостью 4К*8 бит для КМ1816ВЕ751. Запись программ в ПЗУ происходит во время изготовления кристаллов.

Если на вывод ОМЭВМ DEMA подано напряжение питания Ucc, то обращение к внешней памяти программ происходит автоматически при выработке счетчиком команд адреса, превышающего 0FFFH. Если адрес находится в пределах 0000Н—0FFFH, обращение происходит к памяти программ, расположенной на кристалле (внутренней памяти программ).

Если на вывод ОМЭВМ DEMA подан "0", внутренняя память программ отключается и начиная с адреса 0000Н все обращения выполняются к внешней памяти программ.

Если ОМЭВМ не имеет внутренней памяти программ, ее вывод DEMA должен быть подключен к шине 0 В.

Чтение из внешней памяти программ стробируется сигналом ОМЭВМ РМЕ. При работе с внутренней памятью программ сигнал РМЕ не формируется. ОМЭВМ не имеют инструкций и аппаратных средств для программной записи в память программ.

При обращениях к внешней памяти программ всегда формируется 16-разрядный адрес, младший байт которого выдается через порт Р0, а старший — через порт Р2. При этом байт адреса, выдаваемый через порт Р0, должен быть зафиксирован во внешнем регистре по спаду сигнала ALE, т. к. в дальнейшем линии порта Р0 используются в качестве шины данных, по которой байт из внешней памяти программ вводится в ОМЭВМ.

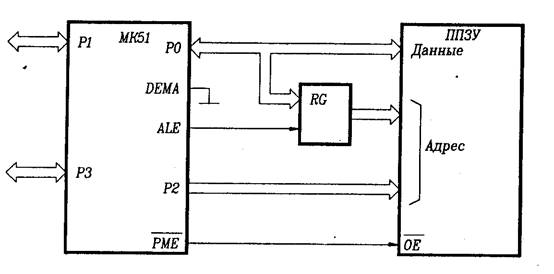

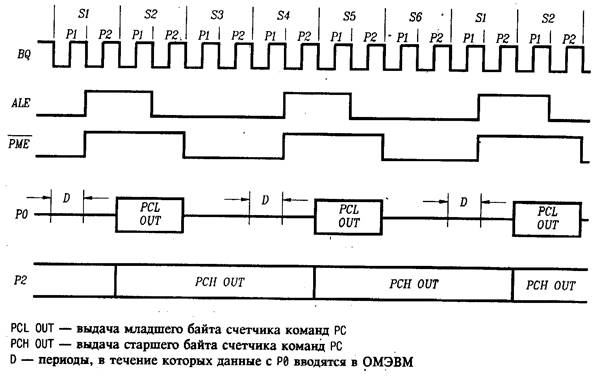

Порт Р0 работает как мультиплексированная шина адрес/данные: выдает младший байт счетчика команд, а затем переходит в высокоимпедансное состояние и ожидает прихода байта из ППЗУ программ. Когда младший байт адреса находится на выходах порта Р0, сигнал АLЕ защелкивает его в адресном регистре RG. Старший байт адреса находится на выходах порта Р2 в течение всего времени обращения к ППЗУ. Сигнал РMЕ разрешает выборку байта из ППЗУ, после чего выбранный байт поступает на порт Р0 МК51 и вводится в ОМЭВМ.

На рис. 1 и 2 приведены диаграммы, показывающие формирование соответствующих сигналов при работе ОМЭВМ с внешней памятью программ. Как видно из диаграмм, при работе с внешней памятью программ сигнал РMЕ формируется дважды в каждом машинном цикле независимо от количества байт в команде. Если второй выбираемый байт в текущей команде не используется, он игнорируется ОМЭВМ. В дальнейшем при переходе к выполнению следующей команды этот байт будет введен вторично.

Рис. 1. Схема включения МК51 с внешним ППЗУ программ

Рис. 2. Работа с внешней памятью программ

Если выполняется команда MOVX (рис. 2), два сигнала РМЕ не формируются, т. к. порт Р0 освобождается для адресации и обмена данными с внешней памятью данных.

Когда ОМЭВМ работает с внутренней памятью программ, РМЕ не формируется и адрес на портах Р0 и Р2 не выдается. Тем не менее, сигнал ALE будет формироваться дважды в каждом машинном цикле всегда за исключением случая команды MOVX (в этом случае один сигнал ALE пропускается). Таким образом, если не используются команды MOVX, сигнал ALE может быть задействован в качестве выходного синхросигнала.

Литература

1 Тавернье К. PIC-микроконтроллеры. Практика применения: Пер. с фр. -М: ДМКПресс, 2008. - 272 с.: ил. (Серия «Справочник»).

2 Борзенко А.Е. IBMPC: устройство, ремонт, модернизация. – 2-е изд. перераб. и доп. – М.: ТОО фирма «Компьютер Пресс», 2006. – 344с.: ил.

3 Цифровые интегральные микросхемы: Справ./М. И. Богданович, И.Н. Грель, В.А. Прохоренко, В.В. Шалимо.–Мн.: Беларусь, 2001. – 493 с.: ил.

4 ДСТУ 3008-95. Документация. Отчеты в сфере науки и техники. Структура и правила оформления.