| Скачать .docx |

Курсовая работа: Курсовая работа: Мікропроцесорний АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується

Міністерство освіти і науки України

Вінницький національний технічний університет

Інститут інформаційних технологій та комп’ютерної інженерії

Кафедра ОТ

Пояснювальна записка

з дисципліни «Цифрові ЕОМ та мікропроцесорні системи»

до спеціалізованого курсового проекту за спеціальністю 7.160104 “Адміністративний менеджмент у сфері захисту інформації з обмеженим доступом” 08-23.ЦМ.004.00.000 ПЗ

МІКРОПРОЦЕСОРНИЙ АЦП ПОРОЗРЯДНОГО ВРІВНОВАЖЕННЯ ІЗ ВАГОВОЮ НАДЛИШКОВІСТЮ, ЩО КАЛІБРУЄТЬСЯ

Керівник курсової роботи

«___» ____________2009 р.

Розробив студент гр. АМЗ-04

_____________________

«___» ____________2009 р.

Вінниця ВНТУ 2009

Міністерство освіти і науки України

Вінницький національний технічний університет

Інститут інформаційних технологій та комп’ютерної інженерії

ЗАТВЕРДЖУЮ

Зав. Кафедри ОТ проф., д.т.н.

_______________ О.Д. Азаров

«___» _____________ 2007 р.

ІНДИВІДУАЛЬНЕ ЗАВДАННЯ

на спеціалізований курсовий проект

з дисципліни «Цифрові ЕОМ та мікропроцесорні пристрої»

студенту _____________________факультету КСМ групи 1 АМЗ-04

ТЕМА: МІКРОПРОЦЕСОРНИЙ АЦП ПОРОЗРЯДНОГО ВРІВНОВАЖЕННЯ ІЗ ВАГОВОЮ НАДЛИШКОВІСТЮ, ЩО КАЛІБРУЄТЬСЯ

Розробити функціональну схему та алгоритм функціонування мікропроцесорного АЦП порозрядного врівноваження із ваговою надлишковістю, що самокалібрується. Обгрунтувати тип мікропроцесора, який можна використовувати для калібрування характеристики перетворення.

Функціональні можливості пристрою:

Робота в режимі:

режим основного перетворення аналог-код з програмною корекцією ваг розрядів надлишкового ЦАП;

Розробка програми керування роботою АЦП у заданому режимі.

Додаткові вимоги:

число розрядів вихідного двійкового коду АЦП N=14;

час перетворення в основному режимі ![]() ;

;

система числення надлишкового ЦАП – НПСЧ на основі золотої пропорції;

число розрядів ЦАП N=20;

Термін здачі студентом завершеного проекту ______________________

Зміст пояснювальної записки

Вступ

Аналіз технічного завдання.

Розробка функціональної схеми.

Вибір мікроконтролера та огляд його архітектури

Вибір додаткових елементів.

Розробка загального алгоритму функціонування АЦП.

Розробка функціональної схеми АЦП.

Розробка програмного забезпечення.

Розробка алгоритму функціонування.

Організація пам’яті та розподіл адресного простору.

Розробка програми, що керує роботою мікропроцесора.

4. Моделювання роботи.

Висновки.

Література.

Графічна частина:

Алгоритм функціонування АЦП.

Граф-схема алгоритму.

3. Принципіальна схема пристрою.

Анотація

Дана робота присвячена розробці мікропроцесорного АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується.

Проводиться аналіз умов та можливостей використання мікропроцесора для керування роботи АЦП, а також розробка функціональної схеми АЦП на базі мікроконтролера та програмного забезпечення для функціонування ЦОП.

У додатках наводяться граф-схема алгоритму, лістинги програм.

Зміст

Перелік умовних скорочень

Вступ

1. Аналіз технічного завдання

2. Розробка функціональної схеми

2.1 Вибір мікроконтролера та огляд його архітектури

2.2 Вибір додаткових елементів

2.3 Розробка загального алгоритму функціонування АЦП

2.4 Розробка функціональної схеми АЦП

3. Розробка програмного забезпечення

3.1 Розробка алгоритму функціонування пристрою

3.2 Організація пам’яті та розподіл адресного простору

3.3 Розробка програми, що керує роботою мікропроцесора

4. Моделювання роботи

Висновки

Перелік літературних джерел

Додаток А. Алгоритм функціонування АЦП

Додаток Б. Алгоритм функціонування пристрою

Додаток В. Алгоритм підпрограми підготовки

Перелік умовних скорочень

АК–аналоговий комутатор

АЛП–арифметико-логічний пристрій

АЦП–аналого-цифровий перетворювач

БДС–блок допоміжних сигналів

БК–блок керування

БП–блок пам’яті

БПВ–блок порозрядного врівноваження

ВІС–велика інтегральна схема

ЕОМ–електронно-обчислювальна машина

МЗР–молодший значущий розряд

МК–мікроконтролер

МП–мікропроцесор

НПСЧ–надлишкова позиційна система числення

ОЗП–оперативний запам’ятовуючий пристрій

ПВЗ–підсилювач вибирання-зберігання

ПЗП–постійний запам’ятовуючий пристрій

РПН–регістр послідовного наближення

САЦП–АЦП, що самокалібруються

СЗР–старший значущий розряд

СП–схема порівняння

ЦАП–цифро-аналоговий перетворювач

ЦОП–цифровий обчислювальний пристрій

Вступ

За останнє десятиліття в світі створене більше сотні типів АЦП, відмінних по функціональному складу і призначенню, конструктивним, електричним і експлуатаційним характеристикам. Відоме їх застосування спільно з МП і мікро ЕОМ у складі пристроїв сполучення між об'єктами і інтерфейсом, а також використання як самостійних функціональних елементів у вузлах і блоках.

Сучасний етап характеризує великі і надвеликі інтегральні схеми АЦП, що володіють високими експлуатаційними параметрами: швидкодією, малими погрішностями, багаторозрядністю. АЦП знаходять широке застосування в різних областях сучасної науки і техніки. Вони є невід’ємною частиною цифрових вимірювальних приладів, систем перетворення і відображення інформації, програмованих джерел живлення, індикаторів на електронно-променевих трубках, систем радіолокації, установок для контролю елементів і мікросхем, а також важливими компонентами різних автоматичних систем контролю і управління, пристроїв вводу/виводу інформації ЕОМ. На їх основі будують перетворювачі і генератори практично будь-яких функцій, аналогові реєструючі пристрої, корелятори, аналізатори спектру і т.д. Великі перспективи використовування швидкодіючих перетворювачів в телеметрії і телебаченні.

Поза сумнівом, серійний випуск малогабаритних і відносно дешевих АЦП ще більш підсилить тенденцію проникнення методу дискретно-безперервного перетворення в сферу науки і техніки.

В даний час застосовують різні типи АЦП, що містять в своєму складі МП, які виконують обробку даних. Очевидно, що обробка даних – одна із головних функцій МП, яка включає як і маніпулювання так і обрахунок даних. Іншою функцією МП є управління системою. Схеми управління дозволяють декодувати і виконувати програми – набір команд для обробки даних. Робота МП складається з наступних кроків: спочатку вибирається команда, потім логічна схема її декодує, після чого здійснюється виконання цієї команди. Також відбувається обмін інформацією з зовнішніми пристроями, які під’єднані до МП.

МП являють собою цифрові ВІС, призначені для виконання простих операцій, інакше названих командами, що зчитуються і здійснюються послідовно з великою швидкістю. До числа внутрішніх схем МП відносяться багаторозрядні регістри, рівнобіжні тракти даних, буфери для підключення зовнішніх пристроїв, багатофункціональні схеми, логічні схеми синхронізації і керування. Багатофункціональні схеми призначені для реалізації простих арифметичних і логічних дій над двійковими числами, що знаходяться в регістрах процесора, і пересилок даних як усередині процесора, так і між ним і зовнішніми пристроями. Схеми синхронізації і керування задають порядок дій процесора, для виконання функцій синхронізації їм необхідні тактові імпульси, що постійно поступають.

Мікропроцесорні засоби використовуються у виді мікропроцесорних комплектів інтегральних мікросхем, що мають єдине конструктивно-технологічне виконання і призначених для спільного застосування. Мікропроцесорний комплект крім самого МП містить мікросхеми, що підтримують функціонування МП і розширюють його логічні можливості.

МК являє собою логічний автомат з високим ступенем детермінованості, який допускає небагато варіантів в його системному включенні.

В пристроях управління об’єктами МК розглядаються у вигляді сукупності апаратно-програмних засобів. При проектуванні схем на базі МК потрібна реалізація оптимального розподілу функцій між апаратними засобами і програмним забезпеченням. Рішення такої задачі ускладнюється тим, що взаємозв’язок і взаємодія між апаратними і програмними засобами динамічно змінюються.

В даний час розповсюджена така методологія, при якій весь цикл розробки схем з використанням МК поділяють на три фази:

1) аналіз задачі і вибір апаратних засобів;

2) розробка прикладного програмного забезпечення;

3) комплексування апаратних засобів і програмного забезпечення;

Дана робота присвячена розробці мікропроцесорного АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується.

1. Аналіз технічного завдання

Для з’ясування вимог до технічного завдання, доцільно навести структуру АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується [1], яку зображено на рисунку 1.1.

Структура повинна містити: аналоговий комутатор (АК) – для переключення між джерелами аналогових сигналів; для процедури врівноваження вхідного аналогового сигналу використовується схема порівняння (СП), регістр послідовних наближень (РПН) та цифро-аналоговий перетворювач (![]() -ЦАП), який працює в надлишковій позиційній системі числення (НПСЧ) (назвемо її робочою системою числення); цифровий обчислювальний пристрій (ЦОП) в якому, в залежності від способу калібрування повинні виконуватись операції додавання, віднімання, множення, ділення та операції з пам’яттю; для збереження цифрових еквівалентів дійсних ваг розрядів та проміжних результатів обчислень – блок пам’яті (БП); блок допоміжних сигналів (БДС) для створення нульового вхідного аналогового сигналу, під час визначення похибки зміщення нуля та, для вимірювальних АЦП, наближене до еталонного джерело напруги або струму, що використовується під час визначення масштабного коефіцієнту; в деяких випадках для фіксації рівня вхідного аналогового сигналу використовується пристрій вибірки та збереження (ПВЗ); для узгодження роботи вище згаданих блоків використовується блок керування (БК). Як бачимо, введення вагової надлишковості відбивається тільки на

-ЦАП), який працює в надлишковій позиційній системі числення (НПСЧ) (назвемо її робочою системою числення); цифровий обчислювальний пристрій (ЦОП) в якому, в залежності від способу калібрування повинні виконуватись операції додавання, віднімання, множення, ділення та операції з пам’яттю; для збереження цифрових еквівалентів дійсних ваг розрядів та проміжних результатів обчислень – блок пам’яті (БП); блок допоміжних сигналів (БДС) для створення нульового вхідного аналогового сигналу, під час визначення похибки зміщення нуля та, для вимірювальних АЦП, наближене до еталонного джерело напруги або струму, що використовується під час визначення масштабного коефіцієнту; в деяких випадках для фіксації рівня вхідного аналогового сигналу використовується пристрій вибірки та збереження (ПВЗ); для узгодження роботи вище згаданих блоків використовується блок керування (БК). Як бачимо, введення вагової надлишковості відбивається тільки на ![]() -ЦАП, решта блоків залишається стандартними, тому всі обчислення відбуваються у загально прийнятій двійковій системі числення. Основна перевага надлишкових позиційних систем числення (НПСЧ), реалізована при аналого-цифровому перетворенні складається у відсутності "розривів" у перетворювальній характеристиці, викликаних відхиленнями реальних ваг розрядів від їхніх розрахункових значень. Для "двійкових" АЦП ці відхилення не повинні перевищувати половини молодшого розряду.

-ЦАП, решта блоків залишається стандартними, тому всі обчислення відбуваються у загально прийнятій двійковій системі числення. Основна перевага надлишкових позиційних систем числення (НПСЧ), реалізована при аналого-цифровому перетворенні складається у відсутності "розривів" у перетворювальній характеристиці, викликаних відхиленнями реальних ваг розрядів від їхніх розрахункових значень. Для "двійкових" АЦП ці відхилення не повинні перевищувати половини молодшого розряду.

Рисунок 1.1 – Структурна схема АЦП порозрядного врівноваження з ваговою надлишковістю

Для АЦП на основі "золотої пропорції" відносна похибка ваг розряду за рахунок технологічних, температурних, часових факторів може досягати до 23,6% [2], що не приведе до пропусків кодів. Таким чином, є можливість, знаючи точні значення реальних ваг розрядів, що беруть участь у перетворенні, одержати точне значення вхідного аналогового сигналу. Задача зводиться до визначення реальних ваг розрядів у спеціальному режимі роботи АЦП, названому калібруванням.

Використання НПСЧ при задані ваг розрядів ЦАП, дозволяє, за рахунок наявності зон перекриття між сусідніми розрядами отримати нерозривну передатну характеристику навіть за умови наявності значних відхилень ваг розрядів [3]. Головним недоліком ЦАП, побудованих з використанням НПСЧ, вважається збільшення кількості розрядів порівняно з двійковим ЦАП, що теоретично мало б призводити до збільшення часу врівноваження. Але, як було доведено в працях професора О.Д.Азарова, швидкодія таких перетворювачів може бути на порядок більша за двійкові без втрати точності за рахунок компенсації динамічних похибок першого та другого роду [4].

Основою системи числення [5] називається співвідношення ваг сусідніх розрядів

.

.

Для двійкової системи ![]() , а для надлишкових систем

, а для надлишкових систем ![]() . До НПСЧ з дробовими вагами розрядів зокрема відносяться так звані системи числення золотої

. До НПСЧ з дробовими вагами розрядів зокрема відносяться так звані системи числення золотої ![]() - пропорції[6].У системах числення золотої

- пропорції[6].У системах числення золотої ![]() -пропорції, будь-яке натуральне число N* можна зобразити у вигляді

-пропорції, будь-яке натуральне число N* можна зобразити у вигляді

1.1

1.1

де

![]()

– вага ![]() -го розряду або

-го розряду або ![]() -а ступінь золотої

-а ступінь золотої ![]() -пропорції. Відповідно при

-пропорції. Відповідно при ![]() =0 НПСЧ вироджується у двійкову систему числення,

=0 НПСЧ вироджується у двійкову систему числення, ![]() =1 – золота пропорція,

=1 – золота пропорція, ![]() – одиничний код. Значення

– одиничний код. Значення ![]() для золотої пропорції рівне 1,618.

для золотої пропорції рівне 1,618.

Застосування вказаної системи числення в порозрядних АЦП дозволяє виконувати самокалібрування виключно у цифровій формі. Це в свою чергу дозволяє відмовитися від введення додаткових аналогових вузлів та блоків для реалізації процедури калібрування ваг розрядів. Використання таких додаткових вузлів у пристрої значно ускладнює аналогову частину АЦП. Разом з тим, калібрування ваг розрядів у цифровій формі в АЦП на основі НПСЧ дозволяє максимально використати можливості цифрових обчислювальних пристроїв, замінити аналогові вузли цифровими і тим самим спростити аналогову частину перетворювачів, а також знизити її вартість.

2. Розробка функціональної схеми

2.1 Вибір мікроконтролера та огляд його архітектури

Сучасні радіоелектронні пристрої побудовані на МК. Це дозволяє спростити схему радіоелектронного пристрою, зробити її більш універсальною, що дозволяє змінюючи програму МК покращувати її споживчі та експлуатаційні характеристики.

Розробнику мікропроцесорних пристроїв приходиться вирішувати ряд характерних задач: на якому процесорі будувати систему, які периферійні пристрої (таймери, послідовні і паралельні порти, АЦП, ЦАП, і т. д. ) вибрати, який блок живлення, скільки коштує розробка.

До недавнього часу у розробників не було широкого вибору. Сімейство однокристальних мікро–EОM Intel 8051, здавалось, перекривало по можливостям задачі, які найбільш часто зустрічаються.

Сьогодні на ринку з’явився цілий ряд фірм зі своїми пропозиціями до однокристальних восьмирозрядних мікро – EОM. В першу чергу це мікро - ЕОМ сімейства Z86 фірми Zilog, МС 68 (Motorola), РІС 16/17 (Microchip). Менш відомі – мікро – ЕОМ ST62 (Thomson) та СОР800(National).

Для того, щоб вибрати з цього різноманіття найбільш вдалу базу для майбутнього мікропроцесорного пристрою, необхідно мати порівняльні характеристики всіх вище перерахованих однокристальних мікро – ЕОМ. Однак кінцевий вибір залежить від багатьох факторів. В першу чергу, це прив’язаність розробника чи традиції, далі – складність вирішуваної задачі ціна однокристальної мікро – ЕОМ.

Цікаве опитування було проведено серед відвідувачів сайту «Телесистеми». Учасники могли відповісти на питання: “Якому мікроконтролеру ви віддаєте найбільшу перевагу?“ Голоси розподілилися таким чином (таблиця 2.1): найбільш популярними стали МК архітектура AVR ( розробка Atmel) і класичної архітектури MCS-51 (розробка Intel).

Популярна також структура PIC, розроблена Microchip. Малопопулярні МК фірми Zilog типу Z8 — виключно із-за одноразової структури програмування. Технічні параметри приблизно однакові, показники надійності — теж. Залишаються тільки міркування чисто фінансового характеру. І ось тут відмінності істотні. Наприклад, ціна МК фірми Intel, в 2, а то і в 3 рази вище за ціну МК фірми Atmel.

Таблиця 2.1 – Статистика опитування на сайті http://www.telesys.ru

| Мікроконтролер | Кількість голосів |

| АСІ | 3 (0%) |

| AVR | 309 (29%) |

| MCS-51 | 220 (21%) |

| PIC | 317 (30%) |

| Z8 | 35 (3%) |

| Z80 | 21(2%) |

| Інший | 60 (5%) |

| Кращий мікроконтролер — DSP | 33 (3%) |

| Ненавиджу мікроконтролери | 41(3%) |

Фірма Atmel запропонувала цікаву серію AVR, яка миттєво знайшла підтримку у радіоаматорів. У МК серії AVR використовуються принципи так званої RISC архітектури, коли пам'ять програм і пам'ять даних, з якими програма оперує, не тільки розділені фізично, але ще мають і різні канали зв'язку з ядром (різні шини). Окрім цього, є ще одна цікава особливість, яка називається конвеєризацією. Конвеєризація дозволяє одночасно і виконувати команду, і готувати до виконання наступну. Гарвардська архітектура, а також конвеєризація і деякі інші спеціальні заходи дозволяють виконувати інструкції дуже швидко — за один машинний цикл.

МК серії AVR мають в своєму складі компаратори, АЦП, пристрої ШІМ, послідовні порти вводу/виводу. Звичайно, різні типономінали включають різні пристрої, але їх набір на сьогоднішній момент є нормою.

Таким чином вибираємо МК фірми Atmel [7].

Для вибору мікроконтролера потрібно враховувати його технічні характеристики, такі як:

швидкодія мікроконтролера;

наявність потрібної периферії;

число ліній введення-виведення;

споживану потужність.

Мікроконтролер, який відповідає даним параметрам належить до сімейства AVR. АVR — це нове сімейство 8-розрядних RISC-мікроконтролерів фірми Atmel. Ці мікроконтролери дозволяють вирішувати безліч задач убудованих систем. Вони відрізняються від інших розповсюджених у даний час мікроконтролерів більшою швидкістю роботи, більшою універсальністю. Швидкодія даних мікроконтролерів дозволяє в ряді випадків застосовувати їх у пристроях, для реалізації яких раніше можна було застосовувати тільки 16-розрядні мікроконтролери, що дозволяє відчутно знизити ціну готової системи. Крім того, мікроконтролери АVR дуже легко програмуються за допомогою компілятора мови асемблера.

Фірма Atmel випускає великий спектр мікроконтролерів серед яких із потрібними параметрами можна визначити модель AT90S2333.

AT90S2333 – економічний 8-бітовий КМОН МК, побудований з використанням розширеної RISC архітектури AVR. Виконуючи по одній команді за період тактової частоти, що дозволяє розробникам створювати системи оптимальні по швидкості і споживаній потужності. У основі ядра AVR лежить розширена RISC архітектура, об'єднуюча розвинений набір команд і 32 регістри загального призначення. Всі 32 регістри безпосередньо підключені до АЛП, що дає доступ до будь-яких двох регістрів за один машинний цикл.

Подібна архітектура забезпечує десятиразовий виграш в ефективності коду в порівнянні з традиційними CISC МК.

AT90S2333 пропонує наступні можливості: 2 Кбайт - пам'ять з підтримкою внутрішнього системного програмування, 128 байт EEPROM, 20 ліній I/O загального призначення, 32 робочих регістра загального призначення, два універсальні таймер/лічильники з режимами порівняння, внутрішні і зовнішні переривання, програмований послідовний UART, 6-ти канальний, 10-ти розрядний АЦП, програмований сторожовий таймер з вбудованим тактовим генератором і програмований послідовний порт SPI для завантаження програм в Flash пам'ять, а також, два програмно вибираних режиму економії енергоспоживання. Режим очікування «Idle» зупиняє CPU, але залишає функціонувати SRAM, таймер/лічильники, SPI порт і систему переривань. Режим економії енергоспоживання «Power Down» зберігає значення регістрів, але зупиняє тактовий генератор, відключаючи всю решту функцій мікроконтролера, аж до наступного зовнішнього переривання, або до апаратної ініціалізації.

МК виробляється з використанням технології незалежної пам'яті високої щільності фірми Atmel. Flash пам'ять на кристалі може бути перепрограмована прямо в системі через послідовний інтерфейс SPI або доступним програматором незалежної пам'яті. Об'єднуючи на одному кристалі вдосконалений 8-бітовий RISC процесор із Flash пам'яттю, AT90S2333 є потужним мікроконтролером, який дозволяє створювати ефективні та маловартісні пристрої.

AVR AT90S2333 підтримується повним набором програм і пакетів для розробки, включаючи: компілятори С, макроасемблери, внутрішньосхемні емулятори і набори для макетування.

Мікроконтролери сімейства AVR мають єдину базову структуру. Узагальнену структурну схему мікроконтролера AT90S2333 зображено на рисунку 2.1.

Рисунок 2.1 – Блок схема мікроконтролера AT90S2333

До складу мікроконтролера входять:

генератор тактового сигналу (GCK);

процесор (CPU);

постійний запам'ятовуючий пристрій для збереження програми виконаний за технологією Flash (FlashROM);

оперативний запам'ятовуючий пристрій статичного типу для збереження даних (SRAM);

постійний запам'ятовуючий пристрій для збереження даних, виконаний за технологією EEPROM, (EEPROM);

набір периферійних пристроїв для вводу/виводу даних і керуючих сигналів, і виконання інших функцій.

До складу процесора (CPU) входять:

лічильник команд (PC);

арифметико-логічний пристрій (ALU);

блок регістрів загального призначення (GPR, General Purpose Regіsters) і інші елементи.

Крім регістрів загального призначення в мікроконтролері маються регістри спеціальних функцій, що у сімействі AVR називаються регістрами вводу/виводу (І/O Regіsters, IOR). За участю цих регістрів здійснюються:

керування роботою мікроконтролера і окремих його пристроїв;

визначення стану мікроконтролера і окремих його пристроїв;

ввід даних у мікроконтролер й окремі його пристрої.

Кожному регістру присвоєне ім'я, пов'язане з функцією, яку виконує цей регістр. Мікроконтролер AT90S2333 має 20 регістрів вводу/виводу, які іменовані, як:

Port B (PB5..PB0) - Порт B є 6-бітовим двонаправленим портом вводу/виводу з внутрішніми підтягаючими резисторами. Вихідні буфери порту B можуть поглинати струм до 20мА. Якщо виводи PB0..PB5 використовуються як входи і ззовні встановлюються в низький стан, вони є джерелами струму, якщо включені внутрішні підтягаючі резистори.

Port С (PС5..PС0) - Порт С є 6-бітовим двонаправленим портом вводу/виводу з внутрішніми підтягаючими резисторами. Вихідні буфери порту С можуть поглинати струм до 20мА. Якщо виводи PС0..PС5 використовуються як входи і ззовні встановлюються в низький стан, вони є джерелами струму, якщо включені внутрішні підтягаючі резистори.

Port D (PD5..PD0) - Порт D є 8-бітовим двонаправленим портом вводу/виводу з внутрішніми підтягаючими резисторами. Вихідні буфери порту B можуть поглинати струм до 20мА. Якщо виводи PD0..PD7 використовуються як входи і ззовні встановлюються в низький стан, вони є джерелами струму, якщо включені внутрішні підтягаючі резистори.

RESET - вхід скидання. Утримання на вході низького рівня протягом двох машинних циклів (якщо працює тактовий генератор), скидає пристій.

Мікроконтролери сімейства AVR є пристроями синхронного типу. Дії, які виконуються в мікроконтролері, прив'язані до імпульсів тактового сигналу.

Як генератор тактового сигналу (GCK) використовуються:

внутрішній генератор із зовнішнім кварцовим чи керамічним резонатором (XTAL);

внутрішній RC-генератор (ІRC);

внутрішній генератор із зовнішнім RC-колом (ERC);

зовнішній генератор (ЕХТ).

У мікроконтролерів, які мають внутрішній генератор із зовнішнім резонатором. XTAL1 і XTAL2 є входом і виходом інвертуючого підсилювача, на якому можна зібрати генератор тактових імпульсів. Можна використовувати як кварцові, так і керамічні резонатори. Якщо сигнал генератора необхідно використовувати для управління зовнішніми пристроями, сигнал з виводу XTAL2 знімається через одиночний буфер. При подачі зовнішнього тактового сигналу вивід XTAL2 залишається непідключеним, а XTAL1 підключається до виходу зовнішнього генератора.

Процесор (CPU) формує адреса чергової команди, вибирає команду з пам'яті й організовує її виконання.

До складу процесора крім лічильника команд (PC), арифметико-логічного пристрою (ALU) і блоку регістрів загального призначення (GPR) входять:

регістр стану мікроконтролера SREG;

регістр-показник стека SP чи SPL і SPH.

Високопродуктивно AVR ALU з'єднано безпосередньо з усіма 32 швидкодіючими регістрами загального призначення. За один тактовий цикл ALU виконує операцію між регістрами цього реєстрового файлу. Операції ALU підрозділяються на три основні категорії: арифметичні, логічні і бітові [8].

2.2 Вибір додаткових елементів

Структурна схема АЦП порозрядного врівноваження містить в аналоговій частині «надлишковий» ЦАП, що використовується під час перетворення.

Число розрядів ![]() , задіяних у надлишковому ЦАП, природно, більше ніж у двійковому

, задіяних у надлишковому ЦАП, природно, більше ніж у двійковому ![]() й визначається зі співвідношення:

й визначається зі співвідношення:

![]() . (2.1)

. (2.1)

Так, для побудови АЦП 14-ти розрядної точності (![]() =14) при α=1,618 потрібен ЦАП на

=14) при α=1,618 потрібен ЦАП на ![]() =20 розряду коду "золотої пропорції". Незважаючи на збільшення розрядної сітки, швидкодія АЦП на основі НПСЧ не зменшується, а навпаки, може бути істотно збільшена. Зазначений ефект виникає внаслідок витрати частини надмірності ваг розрядів на автокомпенсацію динамічних похибок із сигналу, що компенсує [8].

=20 розряду коду "золотої пропорції". Незважаючи на збільшення розрядної сітки, швидкодія АЦП на основі НПСЧ не зменшується, а навпаки, може бути істотно збільшена. Зазначений ефект виникає внаслідок витрати частини надмірності ваг розрядів на автокомпенсацію динамічних похибок із сигналу, що компенсує [8].

Для роботи ЦАП використовується РПН, що забезпечує утворення кодових комбінацій, які створюють компенсуючий сигнал для компаратора в процесі порозрядного врівноваження. Основною складовою РПН є спеціальний регістр – мікросхема AM2504 [7], яка зображена на рисунку 2.2, яка призначена для побудови АЦП, що працюють по принципу послідовного наближення з числом розрядів до 12. Має в своєму складі 4 входи:

С – для подачі тактових імпульсів (спрацювання по зростанню тактових імпульсів), D – інформаційний вхід, Е – дозвіл перетворення та S – вхід “пуск“.

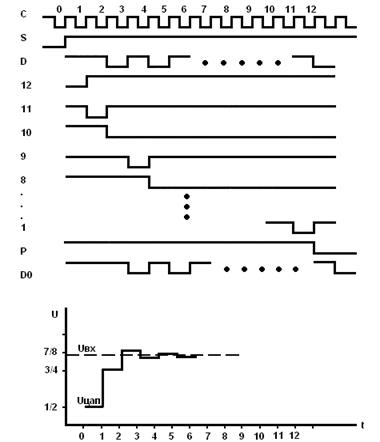

Робота мікросхеми показана на діаграмах C-DO, що зображена на рисунку 2.2.

Рисунок 2.2 – Мікросхема AM2504

При подачі на вхід S логічного 0 по спаду чергового імпульсу відбувається початкова установка тригерів регістра. На виході закінчення перетворення C0 з'являється логічна 1. Такий стан регістра зберігатиметься до тих пір, поки на вході S буде логічний 0.

Після встановлення на вході S логічної 1 перший спад імпульсу негативної полярності виробить запис в тригер регістра з виходами 12 і 12 інформації з входу D і встановить вихід 11 в стан 0, на виходах 10-1 і C0 буде логічної 1.

Спад чергового імпульсу негативної полярності виробить запис інформації з входу D в черговий тригер регістра і встановить наступний за ним вихід в стан 0. Таким чином, на виходах регістра по черзі з'являється логічний 0, вслід за ним - інформація з входу D.

Після запису інформації з входу D в останній тригер регістра (з виходом 1) на виході C0 з'являється логічний 0 і цей стан регістра фіксується до появи логічного 0 на вході S. Якщо вхід S з'єднати з виходом C0, поява логічного 0 на виході C0 по спаду чергового тактового імпульсу приведе до встановлення початкового стану регістра аналогічно імпульсу 0. В результаті мікросхема повторюватиме описаний вище цикл роботи.

Рисунок 2.3 – Часова діаграма роботи мікросхеми AM2504

Наявність входу Е дозволяє сполучати між собою мікросхеми для отримання регістрів послідовного наближення на більшу кількість розрядів, як показано на рисунку 2.4. Робота таких регістрів аналогічна роботі однієї мікросхеми.

Мікросхема дозволяє використовувати її як регістр послідовного наближення і з меншим, ніж на 12, числом розрядів, для чого для подачі сигналу на вхід S можна використовувати його з'єднання з будь-яким з виходів 1-11.

Рисунок 2.4 – З’єднання мікросхем AM2504 для збільшення кількості розрядів

2.3 Розробка загального алгоритму функціонування АЦП

АЦП порозрядного врівноваження перетворить аналоговий сигнал в цифровий за N кроків, де N — розрядність АЦП. На кожному кроці визначається по одному біту шуканого цифрового значення, починаючи СЗР і закінчуючи МЗР. Послідовність дій за визначенням чергового біта полягає в наступному. На ЦАП виставляється аналогове значення, утворене з бітів, вже визначених на попередніх кроках; біт, який повинен бути визначений на цьому кроці, виставляється в 1, більш молодші біти встановлені в 0. Отримане на допоміжному ЦАП значення порівнюється з вхідним аналоговим значенням. Якщо значення вхідного сигналу більше значення на допоміжному ЦАП, то визначуваний біт отримує значення 1, інакше 0. АЦП цього типу володіють одночасно високою швидкістю і хорошою розрядністю.

Слід зазначити, що використання АЦП із ЦАП на основі НПСЧ у складі систем цифрової обробки аналогових сигналів також дає певні переваги перед двійковими перетворювачами інформації. Так, зменшений час врівноважування дозволяє підняти частоту дискретизації, збільшити кількість оброблюваних каналів при роботі в багатоканальному режимі. Незважаючи на спрощену технологію виготовлення аналогових вузлів, результуюча точність перетворення як ЦАП, так і АЦП на основі НПСЧ може бути досить високою при роздільності не менше 14-16 двійкових розрядів. Це досягається, зокрема, калібруванням ваг розрядів і корекцією статичних похибок, що здійснюється цифровим обчислювальним пристроєм. Причому даний пристрій може одночасно виконувати дві функції: калібрування похибок і перетворення НПСЧ у двійкову систему. Для виконання операцій безпосередньо з цифровими сигналами доцільно використовувати мікроконтролер. СП, a-ЦАП, РПН і БК сукупно складають ядро АЦП – блок порозрядного врівноважування (БПВ). У БК передбачено можливість подачі сигналу керування Узв.

Задачею БПВ є перетворення аналогового сигналу з виходу ПВЗ в робочий код К(а), що формується у РПН. Для перетворення робочого коду К у двійковий код використовується окремий ЦОП. Причому на етапі виготовлення системи і компонування аналогових вузлів здійснюється високоточне вимірювання ваг розрядів АЦП. Отримані результати у вигляді двійкових кодів заносяться в БП і використовуються надалі для роботи. Для зв’язку ЦОП із каналами виведення двійкової цифрової інформації використовується послідовний або паралельний інтерфейс залежно від необхідної швидкості передавання інформації [9].

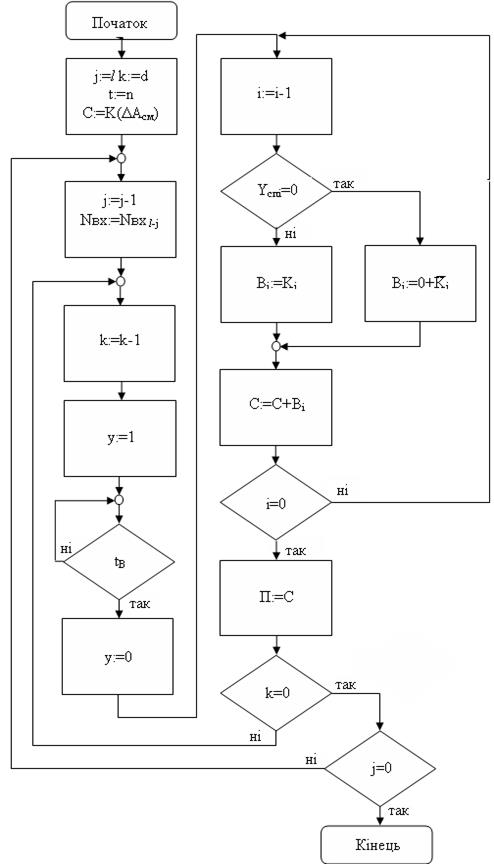

Граф-схему алгоритму функціонування АЦП системи наведено в додатку А. Тут: j – номер каналу; i – номер такту порозрядного врівноважування в БПВ; k – номер дискретизації; С – результат обчислень у ПК; В – операнд, якому призначаються значення кодів із ПЗП; К(ΔА0) – код похибки нуля; Кi – код ваги i-го додатного розряду; ![]() – код ваги i-го від’ємного розряду. Причому у випадку НПСЧ (0,1) існує тільки один від’ємний розряд – знаковий; П – масив пам'яті в мікроконтролері, в якому фіксуються коди дискретизованих відліків аналогових сигналів. Значення цифрового сигналу у=1 відповідає режимові вибірки ПВЗ, у=0 - збереження. У процесі функціонування системи аналогові сигнали з входу подаються на ПВЗ. Дискретизовані відліки потім перетворюються в цифрові еквіваленти і надходять у ЦОП для відповідного оброблення. Причому на етапі проектування виміряються ваги розрядів a-ЦАП, коди яких фіксуються в ПЗП. Надалі ці розряди вважаються "точними" і "стабільними". Водночас варто відзначити, що зазначений пристрій можна виконати, зокрема, на базі мікроконтролера.

– код ваги i-го від’ємного розряду. Причому у випадку НПСЧ (0,1) існує тільки один від’ємний розряд – знаковий; П – масив пам'яті в мікроконтролері, в якому фіксуються коди дискретизованих відліків аналогових сигналів. Значення цифрового сигналу у=1 відповідає режимові вибірки ПВЗ, у=0 - збереження. У процесі функціонування системи аналогові сигнали з входу подаються на ПВЗ. Дискретизовані відліки потім перетворюються в цифрові еквіваленти і надходять у ЦОП для відповідного оброблення. Причому на етапі проектування виміряються ваги розрядів a-ЦАП, коди яких фіксуються в ПЗП. Надалі ці розряди вважаються "точними" і "стабільними". Водночас варто відзначити, що зазначений пристрій можна виконати, зокрема, на базі мікроконтролера.

2.4 Розробка функціональної схеми АЦП

МК для мікропроцесорного АЦП порозрядного врівноваження, що калібрується повинен реалізувати функції таких блоків як: БК, ЦОП, БП, БДС.

Для реалізації даних блоків та їх функції потрібно, щоб МК забезпечував роботу:

1 лінії І/О для прийому сингалу від СП;

1 лінії І/О для передачі сигналу даних для РПН;

1 лінії І/О для сигналу дозволу перетворення РПН;

1 лінії І/О для сигналу початкового встановлення РПН;

14 лінії І/О для паралельного вихідного двійкового коду;

програмованого таймера.

Робота мікропроцесорного АЦП порозрядного врівноваження, що калібрується полягає в наступному:

БК забезпечує управління РПН за допомогою 3-х ліній І/О передачі сигналу даних D та сигналу S, а також сигналу процесом основного перетворення аналог-код з програмною корекцією ваг розрядів надлишкового ЦАП.

Ваги ЦАП виміряються на етапі виготовлення й записуються в EEPROM МК. У циклі калібрування потрібно сформувати в БП точні значення ваг розрядів ЦАП. Для цього за допомогою РПН та ЦАП для кожного з i-го розряду формується аналоговий сигнал.

На початку перетворення відбувається початкове встановлення всіх даних МК, а також встановлення сигналів S та С з рівня логічного 0 в рівень логічної 1 для початкового запуску РПН. Сигнал S в процесі перетворення залишається в рівні логічної 1, а сигнал С забезпечує запуск кожного наступного такту перетворення шляхом формування строб-імпульсу, що керує РПН по передньому фронту переходу з рівня логічного 0 в логічну 1. Відбувається примусове вмикання старшого розряду, що подається на надлишковий ЦАП з якого у вигляді компенсуючого сигналу передається на компаратор.

Після виконання порівняння вхідного сигналу з компенсуючим компаратор видає сигналу у вигляді певного логічного рівня (логічного 0 або 1).

МК сприймає даний сигнал на БК через порт та від його значення виконує функції керування РПН, а також забезпечує формування цифрового еквіваленту аналогового сигналу за допомогою збережених в БП ваг розрядів.

У цьому режимі ЦОП з метою перетворення надлишкового коду на виході РПН у двійковий вихідний код здійснює просте підсумовування двійкових еквівалентів ваг розрядів, які виявилися включеними після зрівноважування вхідного аналогового сигналу.

Про їх включення на РПН свідчить сигнал з компаратора, що сприймається БК.

Час перетворення в основному режимі визначається за допомогою програмованого таймера, що формує часовий період для виконання одного з тактів врівноваження. Після завершення періоду роботи таймера відбувається перевірка лічильника такту перетворення, і відсутності переповнення оцінюється рівень сигналу з компаратора, а також передача сигналів даних та дозволу для запуску РПН.

Після обчислення двійкового вихідного коду в ЦОП, на основі збережених в EEPROM двійкових еквівалентів надлишкових кодів, що відповідають кодам на виході РПН, відбувається їх виведення через порти МК. Вивід здійснюється за допомогою 14 ліній І/О для паралельного вихідного двійкового коду.

Функціональна схема зображена на рисунку 2.5.

Рисунок 2.4 – Функціональна схема пристрою

3. Розробка програмного забезпечення

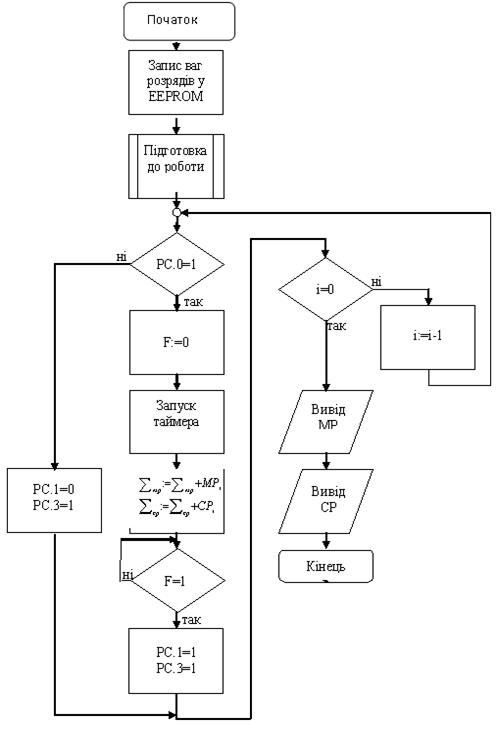

3.1 Розробка алгоритму функціонування пристрою

В МП АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується МК працює на основі наступного алгоритму, який наведено в додатку Б.

Алгоритм працює наступним чином:

Під час виготовлення пристрою вимірюються реальні ваги розрядів надлишкового ЦАП та записуються у вигляді цифрових еквівалентів до енергонезалежної пам’яті EEPROM МК. Цифрові еквіваленти ваг розрядів використовується для калібрування та обчислення в ЦОП 14-розрядного двійкового коду.

Під час запуску режиму основного перетворення аналог-код відбувається встановлення початкових налаштувань для роботи пристрою. Алгоритм підпрограми підготовки наведено в додатку В.

Його робота полягає в наступному: Очищаються регістри БП в яких будуть зберігатися значення двійкового 14-розрядного вихідного коду. Встановлюється початкове значення лічильника, що відповідає кількості розрядів надлишкового ЦАП і слугує для забезпечення необхідної кількості тактів спрацювання РПН і здійснення послідовного наближення. Шляхом встановлення сигналів порту С на виходах: РС.2 – відбувається встановлення сигналу пуску (встановлення сигналу S), РС.1 – сигнал даних, що на даному етапі примусово вмикає СЗР на РПН, який в свою чергу подає його на надлишковий ЦАП, РС.3 – сигнал тактового імпульсу, що по зростанню від рівня логічного 0 до рівня логічної 1 забезпечить запуск перетворення.

Після виконання даного процесу відбувається запуск РПН формування коду для надлишкового ЦАП, який формує аналоговий сигнал (Ак) для СП, що порівнюється із значенням вхідного сигналу (Авх).

Якщо виконується умова Ак>Авх, то на виході СП значення логічного 0, у випадку Ак<Авх – значення логічної 1. Сигнал з СП поступає на вивід РС.0 та залежно від його значення МК виконує певну функцію:

Якщо логічний 0, то МК виконує перевірку значення лічильника і в процесі виконання умови зменшує його та подає сигнали D і C на РПН для здійснення наступного такту врівноваження.

Якщо логічної 1, то МК виконує очистку прапорця стану таймера, потім запускає його. За період, визначений таймером, виконується процес встановлення в регістрах значення сигналів D і C, а також обчислення в ЦОП цифрового еквіваленту аналогового сигналу входу на ввімкненому розряді та його збереження його в БП.

Після завершення роботи таймера виконується перевірка лічильника і в процесі виконання умови зменшує його та подає збережений сигнали D і C на РПН для здійснення наступного такту врівноваження.

Даний процес продовжується до тих пір, поки значення в лічильнику буде рівне 0, що свідчить про завершення врівноваження. У вигляді паралельного, двійкового, 14-розрядного коду через порти B і D виводяться старша та молодша частина цифрового значення вхідного аналогового сигналу.

3.2 Організація пам’яті та розподіл адресного простору

Регістровий файл швидкого доступу містить 32 8-розрядні регістри загального призначення, доступ до яких здійснюється за один машинний цикл. Шість з 32 регістрів можна використовувати як три 16-розрядні покажчики в адресному просторі даних, що дає можливість використовувати високоефективну адресну арифметику (16-розрядні регістри X, У і Z). Один з трьох адресних покажчиків (регістр Z) можна використовувати для адресації таблиць в пам'яті програм.

Простір вводу/виводу складається з 64 адрес для периферійних функцій процесора, таких як управляючі регістри, таймери/лічильники і інші. Доступ до простору вводу/виводу може здійснюватися безпосередньо, як до елементів пам'яті розташованих після регістрового файлу (20h- 5Fh).

Доступ до статичного ОЗП, регістровому файлу і регістрам вводу/виводу здійснюється за допомогою п'яти доступних режимів адресації підтримуваних архітектурою AVR.

Весь простір пам'яті AVR є лінійним і безперервним. Гнучкий модуль переривань має власний керуючий регістр в просторі вводу/виводу , і прапор глобального дозволу переривань в регістрі стану.

Файл регістрів загального призначення

Всі команди, що оперують з регістрами прямо адресуються до будь-якого з регістрів за один машинний цикл. Кожному регістру привласнена адреса в просторі даних, вони відображаються на перші 32 комірки ОЗУ. Хоча регістровий файл фізично розміщений поза ОЗП, подібна організація пам'яті дає гнучкий доступ до регістрів. Регістри X, У і Z можуть використовуватися для індексації будь-якого регістра. Окрім звичних функцій, регістри R26..R31 мають додаткові функції, ці регістри можна використовувати як адресні покажчики у області пам'яті даних.

Flash-пам'ять програм.

AT90S2333 містять 2К завантажувальної flash-пам'яті для зберігання програм. Оскільки всі команди займають одне 16- або 32-розрядне слово, flash-пам'ять організована як 1Kx16. Flash--пам'ять витримує не менше 1000 циклів перезапису. Програмний лічильник має ширину 10 біт і дозволяє адресуватися до 1024 слів програмної flash-пам'яті.

EEPROM пам'ять даних

AT90S2333 містять 128 байт енергонезалежної пам'яті (EEPROM). EEPROM організована як окрема область даних, кожен байт якої може бути прочитаний і перезаписаний. EEPROM витримує не менше 100000 циклів запису/стирання.

Статичний ОЗП даних

На рисунку 3.1 показана організація пам'яті даних в AT90S2333. 224 елементи пам'яті включають регістровий файл, пам'ять вводу/виводу статичний ОЗП даних.

Перші 96 адрес використовуються для регістрового файлу і пам'яті вводу/виводу , наступні 128 - для ОЗП даних.

Рисунок 3.1 – Структура пам’яті

За допомогою будь-якого з цих режимів виробляється доступ до всіх 32 регістрів загального призначення, 64 регістрів вводу/виводу і 128 комірок ОЗП.

Розподіл адресного простору МК для пристрою здійснюється таким чином: R16 – регістр, що містить значення кількості розрядів, R17, R18 – для збереження та обчислення суми СЗР і МЗР, R19 – встановлення порта С для першого такту перетворення, а також для збереження адреси комірки пам’яті EEPROM, R20 – збереження проміжного значення ваг СЗР або МЗР i-го такту перетворення, R21 – для зчитування значень з компаратора, R22 – для переходу до адреси i-го адресу МЗР, R23, R24, R25 – для роботи таймера.

40 байт EEPROM для збереження двійкових еквівалентів надлишкових СЗР та МЗР.

3.3 Розробка програми, що керує роботою мікропроцесора

В МП АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується, МК виконує цифрове обчислення ваг розрядів. Для забезпечення основного перетворення аналог-код періодом 100мкс для 20 тактів перетворення перемикання повинно складати 100/20 – 5мкс. При тактовій частоті мікроконтролера 10 МГц його період 100 нс. Максимальне значення таймера: 216 = 65535.

Потрібно підібрати тактову частоту таймера так, щоб він рахував до 65535 за 5мкс.

При тактовій частоті 10 МГц таймер дорахує до кінця за 100 нс * 65536 = 6,6 мс, що більше 5 мкс.

Потрібно встановити Bit1, Bit0 TCCR1B без коефіцієнту поділу частоти TCCR1B = 0b00000001

Визначимо число, що буде завантажено до OCR1A з яким буде порівнювати компоратор поточний стан таймера.

Підрахуємо кількість тактових імпульсів за час 5 мкс: 5мкс / 100нс = 50

Затримка у 5мкс дорівнює 50 імпульсів. Саме це число завантажимо у OCR1A. Цей регістр складається з двох 8 бітних регістрів OCR1AH та OCR1AL. Перетворемо 50 у шестнадцяти розрядне число й завантажимо його до OCR1AH (старша частина) та OCR1AL (молодша частина).

50(10) = 32(16).

OCR1AH = $00

OCR1AL = $32

Цифрове обчислення коду здійснюється за допомогою двійкових еквівалентів надлишкового коду на виході РПН у ЦОП шляхом підсумовування двійкових еквівалентів ваг розрядів, які виявилися включеними після зрівноважування вхідного аналогового сигналу та зберігаються в EEPROM. Для

НПСЧ на основі “золотої пропорції“ двійкові еквіваленти являють собою двохбайтові числа, які наведено в таблиці 3.1.

Таблиця 3.1 – Двійкові еквіваленти надлишкового коду ЦАП

| № розряду | Двійковий код | № розряду | Двійковий код | ||

| СЗР | МЗР | СЗР | МЗР | ||

| 1 | $00 | $01 | 11 | $00 | $7B |

| 2 | $00 | $02 | 12 | $00 | $B7 |

| 3 | $00 | $03 | 13 | $01 | $42 |

| 4 | $00 | $04 | 14 | $02 | $09 |

| 5 | $00 | $08 | 15 | $03 | $4B |

| 6 | $00 | $0B | 16 | $05 | $53 |

| 7 | $00 | $12 | 17 | $08 | $A2 |

| 8 | $00 | $1D | 18 | $0D | $FF |

| 9 | $00 | $2F | 19 | $16 | $B0 |

| 10 | $00 | $4B | 20 | $24 | $C8 |

Програмна реалізація МП АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується доцільно розробити за допомогою компілятора мови асемблера. Лістинг програми має вигляд:

.include"2333def.inc"

;ПІДГОТОВКА ДО РОБОТИ

.defCOUNTER=R16

.defSZR=R17 ;старші розряди

.defMZR=R18 ;молодші розряди

.defZDVUG=R22 ;перехід до МЗР

CLRSZR

CLRMZR

LDICOUNTER,$13

LDIZDVUG,$14

LDIR19,$0E

OUTDDRC,R19

SBIPORTC,2 ;ВСТАНОВЛЕННЯ CИГНАЛУ S

SBIPORTC,1 ;ВСТАНОВЛЕННЯ CИГНАЛУ D

SBIPORTC,3 ;ВСТАНОВЛЕННЯ CИГНАЛУ C

CBIPORTC,3 ;СКИД СИГНАЛУ C

CBIPORTC,1 ;СКИД СИГНАЛУ C

RJMPSTART

; ПІДПРОГРАМА ЗЧИТУВАННЯ ЦИФРОВИХ ЕКВІВАЛЕНТІВ СЗРІ МЗР З EEPROM

.def ADR=R19

.def VAGA=R20

EEPROM_READ:

OUTEEAR,ADR

SBIEECR,0

INVAGA,EEDR

RET

START:

; ВИКОНАННЯ ЗЧИТУВАННЯ ЗНАЧЕННЯ З КОМПАРАТОРА

M2:INR21,$1

ANDIR21,$1

BREQL1

SBIPORTC,3

CBIPORTC,3

RJMPL2

;ПЕРЕВІРКА ЛІЧИЛЬНИКА КІЛЬКОСТІ ТАКТІВ ПЕРЕТВОРЕННЯ

L2:TSTCOUNTER

BRNEM1

DECCOUNTER

RJMPM2

;ВИКОНАННЯ ЦИФРОВОГО ОБЧИСЛЕННЯ ВАГ РОЗРЯДІВ

L1:

.def TEMP =R23

.def TEMP1 =R24

;ВЕКТОРИ ПЕРЕРИВАНЬ

RJMP RESET

RJMP INT0

RJMP INT1

RJMP TIMER1_CAPT

RJMP TIMER1_COMP1

RJMP TIMER1_OVF

RJMP TIMER0_OVF

RJMP SPI_STC

RJMP UART_RX

RJMP UART_UDRE

RJMP UART_TX

RJMP ADC

RJMP RDY

RJMP COMP

;RESET:

INT_0:

INT_1:

TIMER1_CAPT:

;TIMER1_COMP1

TIMER1_OVF:

TIMER0_OVF:

SPI_STC:

UART_RX:

UART_UDRE:

UART_TX:

ADC:

RDY:

COMP:

RETI

;ІНІЦІАЛІЗАЦІЯ ТАЙМЕРА

RESET:

LDI TEMP,0B01000000 ;ДОЗВІЛ ПЕРЕРИВАННЯ КОМПАРАТОРА

OUT TIMSK,TEMP

LDI TEMP,0B00000001 ;ТАКТОВИЙ СИГНАЛ = CK

OUT TCCR1B,TEMP

LDI R25,$00 ;ІНІЦІАЛІЗАЦІЯ КОМПАРАТОРА

OUT OCR1H,R25

LDI TEMP,$32

OUT OCR1L,TEMP

LDI TEMP,RAMEND ;УСТАНОВКА ВКАЗІВНИКА СТЕКА

OUT SPL,TEMP

LDI TEMP,0 ;СКИД ТАЙМЕРА

OUT TCNT1H,TEMP

OUT TCNT1L,TEMP

SEI ;ДОЗВІЛ ПРЕРИВАННЯ

;ВИКОНАННЯ ЦИФРОВОГО ОБЧИСЛЕННЯ ВАГ СЗР

MOVADR,COUNTER

RCALLEEPROM_READ

ADDSZR,VAGA

;ВИКОНАННЯ ЦИФРОВОГО ОБЧИСЛЕННЯ ВАГ МЗР

ADDADR,ZDVUG

RCALLEEPROM_READ

ADDMZR,VAGA

; ОБРОБЛЮВАЧ ПЕРЕРИВАННЯ КОМПАРАТОРА

TIMER1_COMP1:

LDI TEMP,0 ;СКИД ТАЙМЕРА

OUT TCNT1H,TEMP

OUT TCNT1L,TEMP

SBIPORTC,1

SBIPORTC,3

CBIPORTC,3

RJMPL2

;ВИВЕДЕННЯ ВАГ РОЗРЯДІВ У ВИГЛЯДІ ПАРАЛЕЛЬНОГО ДВІЙКОВОГО КОДУ НА ПОРТИ (ПОРТ D - СЗР; ПОРТ B - МЗР)

M1:.def TEMPP =R16

LSR MZR

LSR MZR

LDI TEMPP,$FF

OUT DDRD,TEMPP

OUT DDRB,TEMPP

OUT PORTD,SZR

OUT PORTB,MZR

NOP

4. Моделювання роботи

Моделювання даного пристрою виконується в програмі моделювання Proteus 7 Professional. за відсутності програмних еквівалентів електронних компонентів, доцільно виконати моделювання роботи МК, яке полягає в тому, щоб забезпечити наявність на вході PC.0 рівнів сигналів, що відповідають рівням при перетворенні на і-му такті та свідчать про стан “вмикання“ чи “вимикання“ певного розряду. В даному випадку від наявності рівня логічного 0 чи логічної 1 відбувається виконання обчислення кодової комбінації двійкового еквіваленту аналогового сигналу на основі цифрових еквівалентів надлишкових ваг розрядів ЦАП. Для отримання кінцевого результату у вигляді двійкового 14-розрядного коду, що є цифровим представленням аналогової величини, що підлягала перетворенню, використовується 14 світлодіодів. Загоряння світлодіодів свідчить про наявність стану “ввімкнено“ і-го розряду. Для прикладу скористаємося рядом сигналів виду 00010000000101110110, що свідчить про вмикання 2,3,5,6,7,9,17 розрядів. Цифрове обчислення коду здійснюється за допомогою двійкових еквівалентів надлишкового коду у ЦОП, які наведено в таблиці 3.1. Для початку програма МК в ЦОП обраховує суму СЗР, а потім МЗР та зберігає їх в регістрах R17, R18 для подальшого виведення у вигляді 14-розрядного двійкового коду на вихідну шину.

Для вище вказаного випадку кодових комбінацій отримуємо, що сума СЗР буде рівна $08, для МЗР – $FB.

Представляючи у двійкових еквівалентах та враховуючи зсув МЗР на 2 біти, отримаємо: 00001000 111110.

Висновки

В роботі було розроблено МП АЦП порозрядного врівноваження із ваговою надлишковістю, що калібрується, а також програму, що керує роботою МК. Програма наочно демонструє принцип роботи пристрою, який дозволяє зручно та якісно виконувати режим основного перетворення аналог-код з програмною корекцією ваг розрядів надлишкового ЦАП, а також передбачає можливість корекції роботи АЦП шляхом перезаписування надлишкових ваг розрядів у двійкових еквівалентах в EEPROM.

Як видно в АЦП на основі НПСЧ надлишковість виявляється тільки у співвідношенні між вагами розрядів ЦАП. Проте в АЦП залишається здатність істотно коригувати вихідні похибки ЦАП. Так, при вихідних відхиленнях ваг розрядів "надлишкового" ЦАП на рівні 5-10% вдається одержати після калібрування АЦП з похибкою лінійності 0.003%.

Очевидно, що описаний спосіб коригування ваг розрядів АЦП має істотні переваги. Так, при підсумовуванні ваг розрядів ЦАП виконується принцип суперпозиції, що передбачає незалежність ваги розряду від станів інших розрядів. Також забезпечується й досить малий дрейф ваг розрядів, який за умовами експлуатації АЦП можливо досить часто калібрувати.

Слід зазначити, що описаний модифікований спосіб порозрядного врівноваження є простим у технічній реалізації. Швидкодія АЦП залежить тільки від алгоритму роботи цифрової частини АЦП. Спосіб порозрядного врівноваження для НПСЧ на основі "золотої пропорції" призводить до подовження розрядної сітки, хоча виграш по швидкодії з урахуванням подовження розрядної сітки становить 5,3 рази.

Таким чином, розробка аналогових пристроїв АЦП на основі НПСЧ дозволяє вирішити ряд актуальних завдань, рішення яких потрібно для розвитку цього перспективного наукового напрямку й актуально для розробки високоточних вимірювальних систем.

1. Азаров О.Д., Архипчик О.А., Захарченко С.М. Високолінійні порозрядні АЦП з ваговою надлишковістю для систем реєстрації і обробляння сигналів – ВНТУ: УНІВЕРСУМ-Вінниця, 2001.

2. Азаров А. Д. Исследование принципов построения и разработка преобразователей информации на основе кодов с иррациональными основаниями: Автореф. дис. канд. техн. наук. – Харьков: ХИРЭ, 1980.

3. Избыточные системы счисления, моделирование, обработка данных и системное проектирование в технике преобразования информации: Учеб. пособие / Поджаренко В.А., Азаров А.Д., Власенко В.А., Коваленко И.И. – К.: Вища шк., 1990.-208с.

4. Азаров О.Д. Розробка теорії аналого-цифрового перетворення на основі надлишкових позиційних систем числення: Автореф. дис... д-ра техн. наук: 05.11.16 / Вінницький політехнічний ін-т. – Вінниця, 1994. – 44с.

5. Карцев А. А. Арифметика цифровых машин. – М.: Наука, 1969. – 576 с.

6. Стахов А.П. Коды золотой пропорции. – М.: Радио и связь, 1984. – 152 с.

7. Офіційна web-сторінка “Телесистеми“ [Електронний ресурс] – Режим доступу: http://www.telesys.ru , вільний. – Загл. з екрана. – Мова рос., англ.

8. Офіційна web-сторінка РефератOFF.ru [Електронний ресурс] – Режим доступу: http://manual.referatoff.ru/011104-1.html, вільний. – Загл. з екрана. – Мова рос.

9. Boyacigiller Z., Sockolov S. Increase analog system accuracy with a 14-bit monolithic ADC // EDN. – 1982. – August, №18.

10. Азаров О.Д. Основи аналого-цифрового перетворення на основі надлишкових позиційних сисем числення . Монографія. – Вінниця: УНІВЕРСУМ – Вінниця, 2004. – 260 с.

Додаток А

Алгоритм функціонування АЦП

Додаток Б

Алгоритм функціонування пристрою

Додаток В

Алгоритм підпрограми підготовки