| Скачать .docx | Скачать .pdf |

Реферат: Преобразователь семисегментного кода

РОССИЙСКАЯ ФЕДЕРАЦИЯ

ХАНТЫ-МАНСИЙСКИЙ АВТОНОМНЫЙ ОКРУГ

ДЕПАРТАМЕНТ ОБРАЗОВАНИЯ И НАУКИ

––––––––––––––––––––––––

СУРГУТСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ

Инженерно-физический факультет

Кафедра Автоматики и компьютерных систем

Пояснительная записка к курсовому проекту

по специальности

Пахомов М.В.

Проверил: преподаватель

Запевалов А.В.

Сургут 2004

Содержание

1. Структурная схема преобразователя семисегментного кода.5

2. Функциональная схема преобразователя семисегментного кода.6

4. Расчет быстродействия и потребляемой мощности.21

Приложение 1: Функциональная схема ПСК……………………………....25

Приложение 2: Принципиальная схема ПСК ..…………………………….26

Вариант 28

Тема: «Преобразователь семисегментного кода».

1. Разработать функциональную схему, проанализировать работу при помощи временных диаграмм.

2. Выбрать типы ИМС, построить принципиальную схему.

3. Рассчитать временные соотношения и потребляемую мощность.

Исходные данные.

|

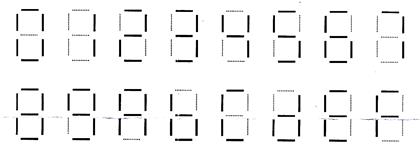

Для отображения состояния регистров цифрового устройства применяются семисегментные индикаторы, синтезирующие изображения цифр «0» - «9» и букв «A» – «F». Необходимо разработать устройство, выполняющее преобразование двоичного кода в семисегментный, причем включенному сегменту соответствует сигнал лог.1. Начертания символов приведены на рисунке.

Устройство должно быть реализовано на логических элементах.

Основная элементная база ИМС серий ТТЛ и ТТЛШ.

Остальные требования согласовать с руководителем проекта.

Руководитель проекта ________________________________

Исполнитель ________________________________

Задачей данного курсового проекта является проектирование устройства, выполняющего преобразование двоичного кода в семисегментный. Для успешного решения поставленной задачи необходимо процесс проектирования разделить на стадии, а именно: структурное, функционально-логическое и техническое проектирование.

При структурном проектировании выбираются, конкретизируются принципы построения устройства в целом. Определяется состав, устанавливаются связи взаимодействия между отдельными частями-блоками, формулируются требования к каждому блоку и выполняемым им функциям.

Функционально-логическое проектирование направлено на поиск и выбор способов реализации функций, возлагаемых на каждый блок. В результате определяются типы, номенклатура функциональных узлов и модулей, входящих в тот или иной блок, то есть функциональный состав блоков, образующих устройство.

Техническое проектирование представляет собой дальнейшую детализацию проектных решений: выбираются типы физических элементов, на которых будет реализовано устройство, то есть элементная база; конкретизируются типономиналы элементов и модулей; проводятся расчеты на обеспечение заданных технических требований.

Преобразователь семисегментного кода в основном находит свое применение в цифровых устройствах, в частности для отображения индикаторами состояния регистров.

1. Структурная схема преобразователя семисегментного кода.

Структурная схема – это условное графическое представление, показывающее количество, номенклатуру блоков устройства, взаимосвязи между блоками и с внешними устройствами.

|

Рис.1 Структурная схема.

Структурная схема преобразователя семисегментного кода может быть представлена (Рис.1):

1. Входная 4-х значная комбинация – 4-х разрядный двоичный код, поступающий на блок преобразования двоичного кода в семисегментный.

2. Блок преобразования двоичного кода в семисегментный – блок, состоящий из простых логических элементов, который предназначен для преобразования входной информации, представленной в виде двоичного кода, в семисегментный код.

3. Блок индикации – предназначен для отображения состояния регистров цифрового устройства на семисегментном индикаторе.

2. Функциональная схема преобразователя семисегментного кода.

Функциональная схема содержит сведения о способах реализации устройством заданных функций. По такой схеме можно определить, как осуществляются преобразования и какие для этого необходимы функциональные элементы. Каждый функциональный элемент содержит лишь те входы и выходы, которые необходимы для его корректной работы. Данная схема разрабатывается на основе структурной схемы для каждого блока, в результате из отдельных функциональных элементов составляется общая функциональная схема объекта.

Полная функциональная схема генератора представлена в приложении 1.

2.1. Блок преобразования двоичного кода в семисегментный.

Данный блок разрабатывается методом синтеза логических устройств с несколькими выходами, то есть на входе логического устройства есть 4-х значная двоичная комбинация, а на выходе 7-ми значная комбинация (семисегментный код).

Для визуализации чисел требуются индикаторы, отображающие цифры в привычной для человека форме, чаще всего это цифры десятичной и шестнадцатеричной систем счисления.

Простейшим из светодиодных индикаторов, выполняющих функции отображения выше названных чисел и некоторых других символов является семисегментный индикатор. Имеется семь элементов, расположенных так, как показано на рис. 2.1.1.

Рис. 2.1.1.

|

Каждый может светиться либо не светиться, в зависимости от значения соответствующей выходной функции, управляющей его свечением. Вызывая свечение элементов в определенных комбинациях, можно получить изображение цифр «0» - «9» и букв «A» – «F» (рис. 2.1.2).

Рис. 2.1.2.

При построении таблицы истинности преобразователя семисегментного кода (табл. 2.1.1) были приняты следующие условия: включенному элементу соответствует сигнал лог.1.

Таблица 2.1.1.

Таблица истинности преобразователя семисегментного кода.

| Отображаемыецифры и буквы | Входная комбинация (двоичный код) | Выходная комбинация (семисегментный код) | |||||||||

| X3 | X2 | X1 | X0 | g | f | e | d | c | b | a | |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 4 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 7 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

| 8 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| A | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| B | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

| C | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

| D | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| F | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| G | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

Синтез данного преобразователя производится с помощью минимизации каждой выходной функции в отдельности методом карт Карно.

При минимизации методом карт Карно нужно стремиться, чтобы число областей было минимальным, а каждая область содержала возможно большее число клеток. Т.к. синтезируемое устройство является устройством с несколькими выходами, то для получения минимальной схемы необходимо в картах Карно построить минимальное число областей, обеспечиваемых покрытие клеток, содержащих 1 во всех семи картах.

Для упрощения синтеза и получения минимальной схемы уменьшаем число единиц в картах Карно и, соответственно увеличиваем число «общих» областей. Для этого инвертируем выходные функции в таблице истинности преобразователя семисегментного кода (табл. 2.1.2).

Таблица 2.1.2.

Таблица истинности преобразователя семисегментного кода с инверсными выходами.

| Отображаемые цифры и буквы | Входная комбинация (двоичный код) | Выходная комбинация (семисегментный код) | |||||||||

| X3 | X2 | X1 | X0 | ||||||||

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 4 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| 5 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| A | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| B | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| C | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| D | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| F | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| G | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

Проанализируем работу преобразователя с помощью временных диаграмм, представленных на рис. 2.1.3.

|

Рис. 2.1.3.

Производим минимизацию каждой выходной функции отдельно методом карт Карно в зависимости от входной комбинации.

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

0 | 1 | 0 | 1 | X3 X3 X3 |

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 0 | 1 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

1 | 1 | 0 | 1 | X3 X3 X3 |

| 0 | 0 | 1 | 0 | ||

| 0 | 0 | 0 | 0 | ||

| 1 | 0 | 0 | 0 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

1 | 1 | 1 | 1 | X3 X3 X3 |

| 0 | 0 | 0 | 1 | ||

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

0 | 1 | 0 | 1 | X3 X3 X3 |

| 0 | 1 | 0 | 0 | ||

| 1 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

0 | 0 | 0 | 0 | X3 X3 X3 |

| 0 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 0 | ||

| 1 | 0 | 0 | 0 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

0 | 0 | 0 | 0 | X3 X3 X3 |

| 1 | 1 | 0 | 0 | ||

| 0 | 1 | 1 | 0 | ||

| 0 | 1 | 0 | 0 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

Карта Карно для функции ![]() :

:

|

|||||

X0 X0 |

0 | 0 | 0 | 0 | X3 X3 X3 |

| 1 | 0 | 1 | 0 | ||

| 0 | 0 | 0 | 0 | ||

| 0 | 0 | 1 | 0 | ||

| X2 X2 X2 | |||||

После выделения областей получим следующую функцию ![]()

После реализации всех функций можно проследить какие логические элементы участвуют в реализации блока преобразования двоичного кода в семисегментный. Для преобразования двоичного кода в семисегментный потребуются четыре элемента НЕ, трех и четырех-входовые элементы И, трех-, четырех-, пяти-входовые элементы ИЛИ-НЕ.

Таблицы истинности и условно-графические обозначения этих элементов представлены на рис. 2.1.6, где Xi – входные сигналы, Y – выходной сигнал.

| Xi |  Y Y |

| 0 | 1 |

| 1 |  0 0 |

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

а)

б)

| X1 | X2 | X3 | X4 | Y |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

г)

|

| X1 | X2 | X3 | X4 | X5 | Y |

| 0 | 0 | 0 | 0 | 0 | 1 |

| * | * | * | * | * | 0 |

в)

д)

| X1 | X2 | X3 | X4 | Y |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 |

|

е)

Рис. 2.1.6. – Таблица истинности и УГО элемента: а) НЕ; б) 3И; в) 4И; г) 3ИЛИ-НЕ; д) 5ИЛИ-НЕ; е) 4ИЛИ-НЕ.

2.2. Блок индикации.

Блок индикации предназначен для отображения состояние регистров цифрового устройства. Данный блок состоит из семисегментного индикатора с общими катодами (рис. 2.1.7), т.к. он управляется высоким уровнем сигнала.

Рис. 2.1.7.

Принципиальную схему разрабатываем на основе функциональной, подбирая для каждого элемента из специальных справочников типономиналы, соответствующие ГОСТу.

3.1. КР1533ЛН1

Микросхема типа ЛН представляет собой инвертор и реализует функцию НЕ. УГО микросхемы представлено на рис. 3.1.1.

Микросхема типа ЛН представляет собой инвертор и реализует функцию НЕ. УГО микросхемы представлено на рис. 3.1.1.

Рис. 3.1.1.

Данная ИМС содержит шесть элементов НЕ, каждый из которых работает в соответствии с таблицей 3.1.1.

Таблицы 3.1.1.

Таблица истинности элемента НЕ

| X | Y |

| 0 | 1 |

| 1 | 0 |

где Х – входной сигнал,

Y – выходной сигнал.

3.2. КР1533ЛИ6

Микросхема типа ЛИ реализует функцию И. УГО микросхемы представлено на рис. 3.2.1.

Микросхема типа ЛИ реализует функцию И. УГО микросхемы представлено на рис. 3.2.1.

Рис. 3.2.1.

Данная ИМС содержит два четырехвходовых элемента И, каждый из которых работает в соответствии с таблицей 3.2.1.

Таблица 3.2.1.

Таблица истинности элемента 4И.

| X1 | X2 | X3 | X4 | Y |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

где Xi – входные сигналы,

Y – выходной сигнал.

3.3. КР1533ЛИ3

Микросхема типа ЛИ реализует функцию И. УГО микросхемы представлено на рис. 3.3.1.

Рис. 3.3.1.

Данная ИМС содержит три трехвходовых элемента И, каждый из которых работает в соответствии с таблицей 3.3.1.

Таблица 3.3.1.

Таблица истинности элемента 3И.

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

где Xi – входные сигналы,

Y – выходной сигнал.

3.4. КР1533ЛЕ4

Микросхема типа ЛЕ реализует функцию ИЛИ-НЕ. УГО микросхемы представлено на рис. 3.4.1.

Рис. 3.4.1.

Данная ИМС содержит три трехвходовых элемента ИЛИ-НЕ, каждый из которых работает в соответствии с таблицей 3.4.1.

Таблица 3.4.1.

Таблица истинности элемента 3ИЛИ-НЕ.

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

где Xi – входные сигналы,

Y – выходной сигнал.

3.5. КР531ЛЕ7

Микросхема типа ЛЕ реализует функцию ИЛИ-НЕ. УГО микросхемы представлено на рис. 3.5.1.

Рис. 3.5.1.

Данная ИМС содержит два пятивходовых элемента ИЛИ-НЕ, каждый из которых работает в соответствии с таблицей 3.5.1.

Таблица 3.5.1.

Таблица истинности элемента 5ИЛИ-НЕ.

| Х1 | X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 0 | 1 |

| * | * | * | * | 0 |

где Xi – входные сигналы,

Y – выходной сигнал.

3.6. К155ЛЕ3

Микросхема представляет собой два логических элемента 4ИЛИ-НЕ со стробированием. Если на входе стробирования присутствует низкий уровень, то вывод соответствующего элемента будет переведен в высокий уровень, независимо от состояния других входов. Если на входе стробирования присутствует высокий уровень, то элемент работает как обычный 4ИЛИ-НЕ (рис. 3.6.1).

Микросхема представляет собой два логических элемента 4ИЛИ-НЕ со стробированием. Если на входе стробирования присутствует низкий уровень, то вывод соответствующего элемента будет переведен в высокий уровень, независимо от состояния других входов. Если на входе стробирования присутствует высокий уровень, то элемент работает как обычный 4ИЛИ-НЕ (рис. 3.6.1).

Рис. 3.6.1.

Данная ИМС содержит два пятивходовых элемента ИЛИ-НЕ, в каждом из которых один вход – стробирующий (Е1), и работает в соответствии с таблицей 3.6.1.

Таблица 3.6.1.

Таблица истинности элемента 4ИЛИ-НЕ.

| E1 | Х1 | X1 | X2 | X3 | Y |

| 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 0 | 0 | |

| 0 | 0 | 1 | 1 | 0 | |

| 0 | 1 | 0 | 0 | 0 | |

| 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 0 | 0 | |

| 1 | 0 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 0 | |

| 0 | * | * | * | * | 1 |

где Xi – входные сигналы,

Е1 – вход стробирования,

Y – выходной сигнал.

3.7. АЛС320Б

Одноразрядный семисегментный цифробуквенный индикатор. Изготавливается на основе структур галлий – фосфор. Данный индикатор имеет зеленый корпус и не имеет цветных точек. УГО данного индикатора представлено на рис. 3.7.1.

Рис. 3.7.1.

где a, b, c, d, e, f, g – светодиоды индикатора.

Составленная принципиальная схема представлена в приложении 2.

4. Расчет быстродействия и потребляемой мощности.

Спроектированная принципиальная схема объекта сопровождается поверочными расчетами технических характеристик: быстродействия, потребляемой мощности, погрешности и т.д.

В данном курсовом проекте необходимо рассчитать быстродействие и потребляемую мощность.

4.1. Расчет потребляемой мощности.

В первом приближении Рсумм рассчитывается как сумма максимальных мощностей, потребляемых микросхемами.

![]() (4.1.1)

(4.1.1)

Рпот – потребляемая мощность;

Рмах i – максимальная потребляемая мощность ИМС i -го типономинала;

ni – количество ИМС i -го номинала;

M – число различных типономиналов ИМС, входящих в схему.

При расчете Рмах i необходимо пользоваться формулой:

![]() (4.1.2)

(4.1.2)

Uпит – напряжение источника питания микросхем (для ИМС серии ТТЛ U пит = 5В).

Iпот i – максимально потребляемый ток ИМС i-го типа.

Максимальная потребляемая мощность для каждой ИМС приведена в таблице 4.1.1.

Таблица 4.1.1.

Таблица мощностей ИМС.

| № | ИМС | n | Рмах ,мВт |

| 1 | КР1533ЛН1 | 1 | 12 |

| 2 | КР1533ЛИ3 | 2 | 12 |

| 3 | КР1533ЛИ6 | 5 | 8 |

| 4 | КР1533ЛЕ4 | 1 | 14,5 |

| 5 | К155ЛЕ3 | 2 | 95 |

| 6 | КР531ЛЕ7 | 1 | 185 |

| 7 | АЛС320Б | 1 | 40 |

![]() (4.1.3)

(4.1.3)

4.2. Расчет быстродействия.

Быстродействие относится к динамическим характеристикам ИМС и характеризуется временем задержки распространения сигнала. Временная задержка - период времени с момента поступления сигнала на вход ИМС до времени его появления на выходе.

В схемах, содержащих несколько последовательно включенных ИМС, время задержки распространения сигнала определятся суммой задержки распространения по всем микросхемам (см. формула 4.2.1).

![]() (4.2.1)

(4.2.1)

где ![]() –суммарная задержка в распространении сигнала через n микросхем от входа первой к выходу последней (n-й).

–суммарная задержка в распространении сигнала через n микросхем от входа первой к выходу последней (n-й).

![]() – средняя задержка распространения сигнала для n-й микросхемы:

– средняя задержка распространения сигнала для n-й микросхемы:

![]() (4.2.2)

(4.2.2)

где ![]() – задержка распространения сигнала при переходе от уровня логической 1 к уровню логического 0;

– задержка распространения сигнала при переходе от уровня логической 1 к уровню логического 0;

![]() – задержка распространения сигнала при переходе от уровня логического 0 к уровню логической 1.

– задержка распространения сигнала при переходе от уровня логического 0 к уровню логической 1.

Для ИМС со многими функционально неравнозначными входами и несколькими выходами время задержки распространения по различным входам неодинаковы. При разработки схем необходимо использовать цепи, создающие минимальные задержки.

Для оценки быстродействия следует выбрать цепь наибольшей длины и рассчитать её суммарную задержку![]() .

.

Типы ИМС и их время задержки, составляющие самую длинную цепь в данном проекте, представлены в таблице 4.2.1.

Таблица 4.2.1

Типы ИМС и время задержки.

| № | Элемент | Тип ИМС | Δtзд ,нс |

| 1 | D1 | КР1533ЛН1 | 12 |

| 2 | D2.1 | КР1533ЛИ6 | 18 |

| 3 | D5.1 | К155ЛЕ3 | 18,5 |

С помощью формулы 4.2.1 определяется общее время задержки:

![]() (4.2.3)

(4.2.3)

В данном курсовом проекте был разработан преобразователь двоичного кода в семисегментный. В ходе проектирования были получены такие навыки как:

1. Выбор и обоснование принципов построения объекта (структурная схема);

2. Разработка функциональных элементов и анализ их функционирования в соответствии с заданными условиями (функциональная схема);

3. Выбор способа реализации функциональных элементов на реально существующих ИМС (принципиальная схема);

4. Расчет технических показателей объекта.

Спроектированное устройство преобразователя двоичного кода в семисегментный соответствует заданным условиям функционирования. Устройство состоит из простейших логических элементов, количество которых не высоко, потребляет мало мощности и имеет незначительное время задержки. Но данное устройство не является удобным, т.к. существуют микросхемы, которые могут производить аналогичные преобразования кодов и по своим характеристикам превосходят данное разработанное устройство.

Список литературы.

1. Калабеков Б.А., Цифровые устройства и микропроцессорные системы: Учебник для техникумов связи. – М.: Горячая линия – Телеком, 2000. – 332 с.

2. Методические указания к выполнению курсового проекта по дисциплине “Цифровая схемотехника” для студентов специальности 210100 “Управление и информатика в технических системах”. Составители: доцент, к.т.н. А.В. Запевалов, Ст. преподаватель Л.Ю. Запевалова. Сургут СурГУ 2000-34 с.

3. Табарина Б.В. Интегральные микросхемы: справочник. – М.: Радио и связь, 1983. – 528 с.

4. Лекции по цифровой схемотехнике.

X1 X1

X1 X1