| Скачать .docx |

Реферат: Регистры сдвиги

1. Оглавление

1. Оглавление …………………………………………………………… 1

2. Введение …………………………………………………………… 2

3. Обзор литературных источников ………………………………… 3

3.1. Общие сведения о регистрах ………………………………… 3

3.2. Общие сведения о триггерах …………………………….…... 6

3.3. Сдвигающие регистры ……………………………………….. 12

3.4. Универсальные регистры ……………………………………….. 20

4. Разработка схемы регистра сдвига ………………………………… 24

4.1. Исходные данные ……………………………………………… 24

4.2. Порядок разработки регистра сдвига …………………..……… 24

4.3. Разработка четырёхфазного регистра сдвига ……............……… 25

5. Вывод ……………………………………………………………. 27

6. Список используемой литературы …………………………………. 28

2. Введение

Регистры – самые распространённые узлы цифровых устройств. Они оперируют с множеством связанных переменных, составляющих слово. Над словами выполняется ряд операций: приём, выдача, хранение, сдвиг в разрядной сетке, поразрядные логические операции.

Сдвигающие (последовательные) регистры используются для сдвига n -разрядных чисел в одном направлении. Кроме того, их можно применять для сдвига нечисловой информации.

Регистры сдвига применяют в качестве запоминающих устройств, качестве преобразователей последовательного кода в параллельный, в качестве устройств задержки и счётчиков импульсов (правда, применение сдвигающих регистров в качестве счётчиков достаточно неэкономично).

3. Обзор литературных источников

3.1. Общие сведения о регистрах

Регистры состоят из разрядных схем, в которых имеются триггеры и, чаще всего, также и логические элементы. Действуют они как единое целое.

По количеству линий передачи переменных регистры делятся на однофазные и парафазные, по системе синхронизации на однотактные, двухтактные и многотактные. Однако главным классификационным признаком является способ приёма и выдачи данных. По этому признаку различают параллельные (статические) регистры, последовательные (сдвигающие) и параллельно-последовательные .

В параллельных регистрах приём и выдача слов производится по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательных регистрах слова принимаются и выдаются разряд за разрядом. Их называют сдвигающими, так как тактирующие сигналы при вводе и выводе слов перемещают их в разрядной сетке. Сдвигающий регистр может быть нереверсивным (с однонаправленным сдвигам) или реверсивным (с возможностью сдвига в обоих направлениях).

Последовательно-параллельные регистры имеют входы-выходы одновременно последовательного и параллельного типа. Имеются варианты с последовательным входом и параллельным выходом (SIPO, Serial Input – Parallel Output), параллельным входом и последовательным выходом (PISO, Parallel Input – Serial Output), а также варианты с возможностью любого сочетания способов приёма и выдачи слов.

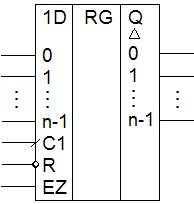

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса / установки, разрешение выхода или приёма, то есть цепи управления. Пример схемы статического регистра, построенного на триггерах D-типа с прямыми динамическими входами, имеющего входы сброса R и выходы с третьим состоянием, управляемые сигналом EZ, показан на рисунке 1 .

a)

б)

Рисунок 1. Схема статического регистра (а) и его условное графическое обозначение (б)

Для современной схемотехники характерно построение регистров на триггерах D-типа, преимущественно с динамическим управлением. Многие имеют выходы с третьим состоянием. Некоторые регистры относятся к числу буферных, то есть рассчитаны на работу с большими ёмкостными и / или низкоомными активными нагрузками. Это обеспечивает их работу непосредственно на магистраль (без дополнительных схем интерфейса).

Из статических регистров составляются блоки регистровой памяти – регистровые файлы.

Главные функции регистров:

1) Хранение информации,

2) Прием информации,

3) Выдача информации,

4) Сдвиг информации,

5) Преобразование кодов,

6) Установление в ноль или в единицу нужного числа,

7) Поразрядные логические операции: дизъюнкция, конъюнкция, сложение по модулю 2.

3.2. Общие сведения о триггерах

Триггеры – большой класс электрических устройств, позволяющих длительно находится в одном из двух (или более) устойчивых состояний и чередовать их под воздействием внешних сигналов (в следствии регенеративного процесса (переходной процесс в электрической цепи, охваченной ПОС)).

Триггер – импульсное логическое устройство с памятью (элемент памяти – фиксатор).

Существует более десятка различных интегральных триггеров. В основу их классификации положены:

- функциональный признак,

- способ записи информации в триггер.

По функциональному признаку различают Т-триггеры, JK-триггеры, RS-триггеры, D-триггеры, комбинированные триггеры (TV, DV, E, R) и т.д.

По способу записи (приёма) информации различают:

8) Асинхронные триггеры:

а) с внутренней задержкой;

б) управляемые уровнем входного импульса;

9) Синхронные триггеры (тактируемые):

а) с внутренней задержкой;

б) управляемые уровнем тактирующего импульса:

- однотактного действия (одноступенчатые);

- многократного действия.

Запись информации в тактируемые триггеры осуществляется только при подаче разрешающего тактирующего импульса. Такие триггеры делят на управляемые уровнем (для срабатывания необходим определённый уровень сигнала) и управляемые фронтом (не зависят от уровня сигнала, важно его присутствие) тактирующего импульса. Тактирующие импульсы иногда ещё называют синхронизирующими, исполнительными, командными сигналами (на схемах обычно обозначают буквой С - Clock).

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Динамический вход может быть прямым и инверсным. Прямое динамическое управление подразумевает разрешение на переключение при изменении тактового сигнала с нулевого значения на единичное ( ). Инверсное динамическое управление – изменение тактового сигнала с единичного на нулевой ( ).

Динамический вход может быть прямым и инверсным. Прямое динамическое управление подразумевает разрешение на переключение при изменении тактового сигнала с нулевого значения на единичное ( ). Инверсное динамическое управление – изменение тактового сигнала с единичного на нулевой ( ).

![]()

![]() Управление фронтом тактирующего импульса:

Управление фронтом тактирующего импульса:

![]()

![]() Управление спадом тактирующего импульса:

Управление спадом тактирующего импульса:

![]()

![]() Управление верхним уровнем тактирующего импульса:

Управление верхним уровнем тактирующего импульса:

Управление нижним уровнем тактирующего импульса:

Тактируемые триггеры с внутренней задержкой (срабатывают по окончании действия сигнала) являются, как правило, однотактными. Многотактные триггеры срабатывают после n -ного импульса.

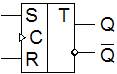

RS-триггер имеет два информационных входа: S (Set) и R (Reset). Одновременная подача сигналов S и R не допускается. На рисунке 2 изображен синхронный RS-триггер, срабатывающий по фронту тактирующего сигнала.

Рисунок 2. Синхронный RS-триггер

Кроме входов, простейший RS-триггер имеет и два выхода. Выходы обозначают Q

и ![]() . Выход Q

называют прямым, a

. Выход Q

называют прямым, a ![]() - инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q

= 1, то

- инверсным. Уровни напряжения на обоих выходах взаимно инверсны: если сигнал Q

= 1, то ![]() = 0, либо если Q

= 0, то

= 0, либо если Q

= 0, то ![]() = 1. Необходимо еще отметить, что состояние триггера, при котором Q

= 1, a

= 1. Необходимо еще отметить, что состояние триггера, при котором Q

= 1, a ![]() = 0, называют единичным. При нулевом состоянии триггера Q

= 0 и

= 0, называют единичным. При нулевом состоянии триггера Q

= 0 и ![]() = 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется.

= 1. С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется.

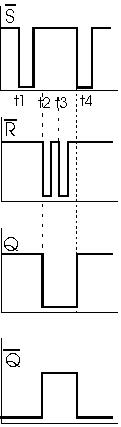

Рисунок 3. ![]() -

триггер: его условное графическое обозначение и схема с двумя логическими элементами И-НЕ

-

триггер: его условное графическое обозначение и схема с двумя логическими элементами И-НЕ

На рисунке 3

показан простейший триггер – типа ![]() . Здесь использованы только два логических элемента И-НЕ. Назначение входов:

. Здесь использованы только два логических элемента И-НЕ. Назначение входов: ![]() -для установки триггера в единичное состояние и

-для установки триггера в единичное состояние и ![]() - для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рисунок 4

). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q

= 1 и

- для возвращения в нулевое состояние. Черточки над обозначениями входов показывают, что переключение триггера происходит, когда входное напряжение высокого уровня сменяется напряжением низкого уровня (рисунок 4

). Нетрудно видеть, что когда на входы не поступают сигналы, триггер сохраняет свое состояние. Если, например, Q

= 1 и ![]() = 0, то есть триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение

= 0, то есть триггер в единичном состоянии, то, поскольку выход DD1 связан с одним из входов DD2, а выход DD2 - с одним из входов DD1, на двух входах DD2 действует напряжение

|

Рисунок 4.

Временная диаграмма работы |

высокого, а на выходе - низкого ( |

Из сказанного следует, что смена состояния триггера происходит только при чередовании сигналов низкого уровня на входах ![]() и

и ![]() . При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q

= 0 или Q

= 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается.

. При этом, если такие сигналы поступят на оба входа одновременно, то после их прекращения состояние триггера станет неопределенным (состояние Q

= 0 или Q

= 1 равновероятно). Поэтому одновременная подача сигналов низкого уровня на оба входа не разрешается.

Работа ![]() -триггера характеризуется таблицей состояний (индексы n

и n+1

означают принадлежность сигнала моменту времени tn

и следующему за ним tn+1

):

-триггера характеризуется таблицей состояний (индексы n

и n+1

означают принадлежность сигнала моменту времени tn

и следующему за ним tn+1

):

|

|

|

|

|

| 1 |

1 |

|

|

| 1 |

0 |

1 |

0 |

| 0 |

1 |

0 |

1 |

| 0 |

0 |

Неопределённое состояние |

|

Не разрешается одновременная подача напряжения низкого уровня на оба входа ![]() -триггера.

-триггера.

Триггер типа RS, как и ![]() -триггер, "запоминает", на какой из двух входов (R или S) поступил последний сигнал: если на вход R, триггер находится в нулевом состоянии (Q

= 0 и

-триггер, "запоминает", на какой из двух входов (R или S) поступил последний сигнал: если на вход R, триггер находится в нулевом состоянии (Q

= 0 и ![]() = 1), а если на вход S, то в единичном состоянии (Q

= 1 и

= 1), а если на вход S, то в единичном состоянии (Q

= 1 и ![]() = 0).

= 0).

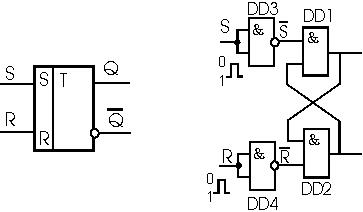

Рисунок 5. RS- триггер: его условное графическое обозначение и схема с четырьмя логическими элементами И-НЕ

На рисунке 5

показана схема RS-триггера, выполненного на логических элементах И-НЕ. Она отличается от схемы ![]() -триггера тем, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только обеспечивают необходимый уровень входных сигналов.

-триггера тем, что к каждому входу добавлено по инвертору (DD3 и DD4), которые только обеспечивают необходимый уровень входных сигналов.

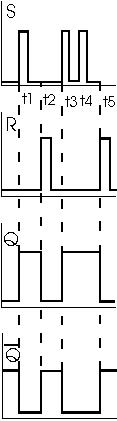

Изменение входных сигналов от низкого уровня до высокого приводит к смене состояния триггера (моменты t1, t2, t2 и t5 ; в момент t4 опрокидывания не происходит, так как триггер уже установлен в единичное состояние в предшествующий момент - t3, рисунок 6 ).

Рисунок 6. Временная диаграмма работы RS- триггера

Все сказанное относительно RS-триггера сохраняет силу и для ![]() -триггера. Единственное различие касается инверсии уровней входных сигналов (R вместо

-триггера. Единственное различие касается инверсии уровней входных сигналов (R вместо ![]() и S вместо

и S вместо ![]() ).

).

Работа RS-триггера характеризуется следующей таблицей состояний:

|

|

|

|

|

| 0 |

0 |

|

|

| 0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

| 1 |

1 |

Неопределённое состояние |

|

3.3. Сдвигающие регистры

Триггерным регистром сдвига называют совокупность триггеров с определёнными связями между ними, при которых они действуют как единое устройство. Последовательные (сдвигающие) регистры представляют собой цепочку разрядных схем, связанных цепями переноса.

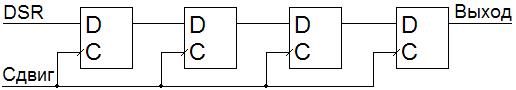

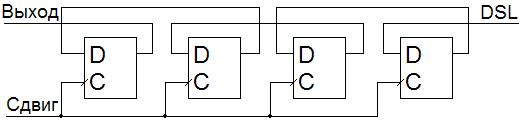

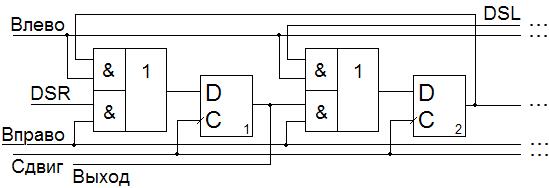

В однотактных регистрах со сдвигом на один разряд вправо (рисунок 7 ) слово сдвигается при поступлении сигнала синхронизации. Вход и выход последовательные (DSR – Data Serial Right). На рисунке 8 показана схема регистра со сдвигом влево (вход данных DSL – Data Serial Left), а на рисунке 9 иллюстрируется принцип построения реверсивного регистра, в котором имеются связи триггеров с обоими соседними разрядами, но соответст-вующими сигналами разрешается работа только одних из этих связей (команды «влево» и «вправо» одновременно не подаются).

Рисунок 7. Схема право-сдвигающего регистра

Рисунок 8 . Схема лево-сдвигающего регистра

Рисунок 9 . Схема реверсивного регистра

Согласно требованиям синхронизации, в сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время действия разрешающего уровня синхросигнала переключится неоднократно, что недопустимо. В данных схемах следует применить триггеры с динамическим управлением (двухступенчатые).

Появление в межразрядных связях логических элементов и, тем более, логических схем неединичной глубины упрощает выполнение условий работоспособности регистров и расширяет спектр типов триггеров, пригодных для этих схем.

Многотактные сдвигающие регистры управляются несколькими синхропоследовательностями. Из их числа наиболее известны двухтактные с основным и дополнительным регистрами, построенными на простых одноступенчатых триггерах, управляемых уровнем. По такту С1 содержимое основного регистра переписывается в дополнительный, а по такту С2 возвращается в основной, но уже в соседние разряды, что соответствует сдвигу слова. По затратам оборудования и быстродействию этот вариант близок к однотактному регистру с двухступенчатыми триггерами.

В регистре сдвига присутствует набор триггеров с определёнными связями между ними и организация этих связей такова, что при подаче тактового импульса, общего для всех триггеров, выходное состояние каждого триггера сдвигается в соседний. В зависимости от организации связей этот сдвиг может происходить влево или вправо:

![]() - сдвиг влево

- сдвиг влево

![]() - сдвиг вправо

- сдвиг вправо

Ввод информации в регистр может выполнятся различными способами, однако наиболее часто используют параллельный или последовательный ввод, при которых ввод двоичного числа осуществляется или одновременно во все разряды регистра, или последовательно во времени по отдельным разрядам. В счётчиках импульсов находят применение сдвигающие регистры с последовательным вводом и выводом информации и со сдвигом вправо. На рисунке 10

a

приведена схема четырёхразрядного регистра сдвига, выполненного на RS-триггерах. В этой схеме каждый выход Q

триггера соединён со входом S последующего разряда, а каждый выход ![]() - с входом R. Тактовые входы всех триггеров соединены вместе, и поступление сигнала синхронизации осуществляется одним общим импульсом через логический элемент И-НЕ (DD7). Состояние первого триггера определяется входными сигналами на входах Х1, Х2 логического элемента И-НЕ (DD5). На вход Х1 подаётся текущая информация, а на вход Х2 сигнал разрешения её передачи. Логический элемент НЕ используется (DD6) используется для инвертирования входного сигнала, подаваемого на вход S.

- с входом R. Тактовые входы всех триггеров соединены вместе, и поступление сигнала синхронизации осуществляется одним общим импульсом через логический элемент И-НЕ (DD7). Состояние первого триггера определяется входными сигналами на входах Х1, Х2 логического элемента И-НЕ (DD5). На вход Х1 подаётся текущая информация, а на вход Х2 сигнал разрешения её передачи. Логический элемент НЕ используется (DD6) используется для инвертирования входного сигнала, подаваемого на вход S.

На рисунке 10 б приведены временные диаграммы выходных сигналов триггеров и состояния регистров при записи в первый разряд единичного сигнала. Если при поступлении первого тактового импульса на входах Х1 и Х2 установлены сигналы Х1 = Х2 = 1, которые затем снимаются к приходу второго тактового импульса, то в результате в первый триггер будет записан сигнал Q 1 = 1. С приходом второго тактового импульса в первый триггер будет записан сигнал Q 1 = 0, а на выходе второго триггера появится сигнал Q 2 = 1, который перед этим был на выходе второго триггера. При поступлении последующих тактовых импульсов единичный сигнал перемещается последовательно в третий и четвёртый триггеры, после чего все триггеры устанавливаются в нулевое состояние.

a)

a)

| n |

Q1 |

Q2 |

Q3 |

Q4 |

| 0 |

1 |

0 |

0 |

0 |

| 1 |

0 |

1 |

0 |

0 |

| 2 |

0 |

0 |

1 |

0 |

| 3 |

0 |

0 |

0 |

1 |

б)

Рисунок 10 . Схема четырёхфазного регистра сдвига (а), временные диаграммы его сигналов и состояния регистров при записи в первый разряд единичного сигнала (б)

Сдвиговые регистры также можно реализовать на D-триггерах ил JK-триггерах. Для всех регистров сдвига характерны следующие положения:

1) необходима предварительная установка исходного состояния и ввод единицы в первый триггер

2) для регистра из n триггеров после поступления n входных тактовых импульсов первоначально введённая единица выводится, вследствие чего прямые выходы всех регистров оказываются в нулевом состоянии.

Интегральные микросхемы регистров сдвига бывают реверсивными, то есть выполняющими сдвиг в любом направлении: влево или вправо. Направление сдвига определяется значением управляющего сигнала.

Рисунок 11. Реализация регистра сдвига на однотактных RS-триггерах

Последовательный регистр сдвига обладает двумя недостатками: он позволяет вводить только по одному биту информации на каждом тактовом импульсе и, кроме того, каждый раз при сдвиге информации в регистре вправо теряется крайний правый информационный бит. На рисунке 12 показана система, которая позволяет осуществлять одновременную параллельную загрузку 4 бит информации.

Рисунок 12. Структурная схема 4-разрядного параллельного регистра

Входы 1, 2, 3, 4 в этом устройстве являются информационными входами. Эту систему можно снабдить еще одной полезной характеристикой - возможностью кольцевого перемещения информации, когда данные с выхода устройства возвращаются на его вход и не теряются.

Рисунок 13. Логическая схема четырёхразрядного параллельного кольцевого регистра

Схема 4-разрядного параллельного кольцевого регистра сдвига показана на рисунке 13 . В этом регистре сдвига используются четыре JK-триггера. Благодаря цепи обратной связи введенная в регистр информация, которая обычно теряется на выходе четвёртого триггера, будет циркулировать по регистру сдвига. Сигналом очистки регистра (установки его выходов в состояние 0000) является уровень логического 0 на входе CLR. Входы параллельной загрузки данных 1, 2, 3 и 4 связаны со входами предварительной установки триггеров (PS), что позволяет устанавливать уровень логической 1 на любом выходе (1, 2, 3, 4). Если на один из этих входов даже кратковременно подать логический 0, то на соответствующем выходе будет установлена логическая 1. Подача тактовых импульсов на входы C всех JK-триггеров приводит к сдвигу информации в регистре вправо. Из четвёртого триггера данные передаются в первый триггер (кольцевое перемещение информации).

Таблица 1.

| № |

Входы |

Выходы |

||||||||

| Очистка |

Параллельная загрузка данных |

№ тактового импульса |

1 |

2 |

3 |

4 |

||||

| 1 |

2 |

3 |

4 |

|||||||

| 1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

| 2 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

| 3 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

| 4 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

| 5 |

1 |

1 |

1 |

1 |

1 |

2 |

0 |

0 |

0 |

1 |

| 6 |

1 |

1 |

1 |

1 |

1 |

3 |

1 |

0 |

0 |

0 |

| 7 |

1 |

1 |

1 |

1 |

1 |

4 |

0 |

1 |

0 |

0 |

| 8 |

1 |

1 |

1 |

1 |

1 |

5 |

0 |

0 |

1 |

0 |

| 9 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

|

| 10 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

| 11 |

1 |

1 |

1 |

1 |

1 |

6 |

0 |

0 |

1 |

1 |

| 12 |

1 |

1 |

1 |

1 |

1 |

7 |

1 |

0 |

0 |

1 |

| 13 |

1 |

1 |

1 |

1 |

1 |

8 |

1 |

1 |

0 |

0 |

| 14 |

1 |

1 |

1 |

1 |

1 |

9 |

0 |

1 |

1 |

0 |

| 15 |

1 |

1 |

1 |

1 |

1 |

10 |

0 |

0 |

1 |

1 |

Принцип работы параллельного регистра сдвига описан в таблице 1 . При включении питания на выходах регистра может установиться любая двоичная комбинация, такая, например, как в строке 1 таблицы. Подача логического 0 на входы CLR триггеров инициирует очистку регистра (строка 2). Далее (строка 3) осуществляется загрузка в регистр двоичной комбинации 0100. Последовательные тактовые импульсы вызывают сдвиг введенной информации вправо (строки 4 - 8). В строках 5 и 6: единица из крайнего правого триггера (четвёртого) переносится в крайний левый триггер (первый). В данном случае можно говорить о кольцевом перемещении единицы в регистре. Далее (строка 9) вновь инициируется очистка регистра с помощью входа CLR. Загружается новая двоичная комбинация 0110 (строка 10). Подача 5 тактовых импульсов (строки 11-15) приводит к кольцевому сдвигу информации на 5 позиций вправо. Для возвращения данных в исходное состояние требуется 4 тактовых импульса.

Если в регистре сдвига на рисунке 13 разорвать петлю обратной связи, то мы получим обычный параллельный регистр сдвига: возможность кольцевого перемещения информации будет исключена.

|

|

Рисунок 14. Трехтактный регистр сдвига на RS-триггерах

3.4. Универсальные регистры

Часто вместо обычных последовательных или параллельных требуется применить более сложные сдвигающие регистры: с параллельной синхронной записью информации, реверсивные, реверсивные с параллельной синхронной записью. Такие регистры называют универсальными .

Есть множество серий ИС регистров многорежимных (многофункциональных) или универсальных, способных выполнять набор микроопераций. Многорежимность достигается композицией в одной и той же схеме частей, необходимых для выполнения различных операций. Управляющие сигналы, задающие вид выполняемой в данное время операции, активизируют необходимые для этого части схемы.

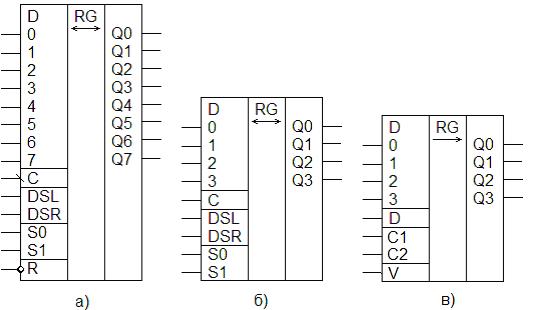

Рисунок 15. Универсальные регистры сдвига: а – К155ИР13, б – К500ИР141, в – КМ155ИР1

На рисунке 15 показано три типичных представителя универсальных сдвиговых регистров серии К155, КМ155 и К500.

Микросхема ИР13 (рисунок 15 а

) – это восьмиразрядный реверсивный сдвигающий регистр с допустимой тактовой частотой до 25 МГц при токе потребления до 40 мА. Имеет параллельные входы и выходы, вход асинхронного сброса ![]() , входы DSL (сдвиг влево) и DSR (сдвиг вправо) по перепаду синхронизирующих импульсов С, входы выбора режима S0 и S1. При S0 = 0, S1 = 1 происходит сдвиг информации вправо, при S0 = 1, S1 = 0 – влево, а при S0 = S1 = 1 – запись информации в регистр.

, входы DSL (сдвиг влево) и DSR (сдвиг вправо) по перепаду синхронизирующих импульсов С, входы выбора режима S0 и S1. При S0 = 0, S1 = 1 происходит сдвиг информации вправо, при S0 = 1, S1 = 0 – влево, а при S0 = S1 = 1 – запись информации в регистр.

Микросхема ИР141 (рисунок 15 б ) – это универсальный четырёх-разрядный сдвиговый регистр, построенный на эмитерно-связной логике. Тактовая частота – до 150 МГц. Потребляемый ток – не менее 120 мА. При S0 = 0, S1 = 1 происходит сдвиг информации вправо, при S0 = 1, S1 = 0 – влево, а при S0 = S1 = 1 – хранение числа, при S0 = S1 = 0 – установка числа.

Микросхема ИР1 (рисунок 15 в ) – это сдвигающий регистр с синхронной записью информации на RS-триггерах. Входы 1 – 4 предназначены для параллельной записи информации, вход D – для последовательной записи. Вход V – управляющий. При V = 0 схема работает как сдвигающий регистр по отрицательному перепаду (с 1 на 0) сигнала С1, а при V = 1 схема работает в режиме синхронной записи в регистр сигналов входов 1 – 4 по отрицательному перепаду сигнала С2.

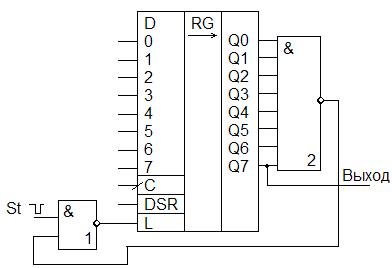

Регистры, имеющие разнотипные вход и выход, служат основными блоками преобразователей параллельных кодов в последовательные и обратно. На рисунке 16 показана схема преобразователя параллельного кода в последовательный на основе восьмиразрядного регистра типа SI/PO/SO. В этой схеме отрицательный стартовый импульс St, задающий уровень логического нуля на верхнем входе элемента 1, создаёт единичный сигнал параллельного приёма данных на вход L (Load – загрузка), по которому в разряды 1 – 7 регистра загружается преобразуемое слово, а в нулевой разряд – константа 0. На последовательный вход DSR подана константа 1. Таким образом, после загрузки в регистре формируется слово. Тактовые импульсы, поступающие на вход С, вызывают сдвиг слова вправо. Сдвиги выводят слово в последовательной форме через выход Q7. Вслед за информационными разрядами идёт 0, после которого цепочка единиц. Пока ноль не выведен из регистра, на выходе элемента 2 действует единичный сигнал. После вывода нуля все входы элемента 2 становятся единичными, его выход приобретает нулевое значение и через элемент 1 формирует сигнал автоматической загрузки следующего слова, после чего цикл преобразования повторяется.

Рисунок 16. Схема преобразователя параллельного кода в последовательный

Современные регистры мало приспособлены для выполнения поразрядных логических операций, но при необходимости их можно выполнить пользуясь регистрами на RS-триггерах. Для выполнения операции ИЛИ на S вход статического регистра с исходным нулевым состоянием подаётся первое слово, единичные разряды которого устанавливают соответствующие триггеры. Затем без сброса регистра на S выходы подаётся второе слово.

При выполнении поразрядной операции И в первом такте на S входы регистра подаётся первое слово, устанавливающее те разряды регистра, в которых это слово имеет единицы. Затем следует подать на регистр второе слово. Чтобы в регистре сохранились единицы только в тех разрядах, в которых оба слова имеют единицы, второе слово подаётся на входы R триггеров в инверсном виде.

Сложение по модулю 2 может быть выполнено схемой с триггерами типа Т в разрядах путём последовательной во времени подачи на неё двух слов.

4. Разработка схемы регистра сдвига

4.1. Исходные данные

Заданы тактовые импульсы положительной полярности.

4.2. Порядок разработки регистра сдвига

а) Рассмотрение общих требований к схеме регистра.

б) Разработка регистра сдвига.

в) Описание работы разработанной схемы.

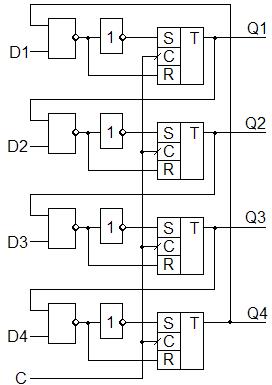

4.3. Разработка четырёхфазного регистра сдвига

Необходимо разработать четырёхфазный регистр сдвига на RS-триггерах. Пусть он будет правосдвигающим. Для этого нам понадобится четыре синхронных RS-триггера с синхронизацией по фронту тактирующего импульса и некоторое число логических элементов для создания цепей переноса. Так как сдвигающие регистры с последовательными входом и выходом имеют низкое быстродействие, разработаем схему с параллельными входом и выходом.

Рисунок 17. Разработанная схема правосдвигающего синхронного регистра на RS-триггерах

Выполняя инвертирование сигнала на входах триггеров мы добиваемся того, что подача напряжений одинаковых уровней на входы S и R невозможна. Значит, при S = 0, R = 1 – на выходе получим 0, при S = 1, R = 0 – на выходе получим 1. На входах сдвигающего регистра необходимо установить четыре элемента со следующей таблицей истинности:

| Х1 |

Х2 |

Y |

| 0 |

0 |

1 |

| 0 |

1 |

0 |

| 1 |

0 |

1 |

| 1 |

1 |

0 |

Соединив четвёртый выход с первым входом мы получаем кольцевой правосдвигающий регистр. Информация с выхода Q4 не будет теряться, а будет циркулировать заново.

Поскольку такой регистр сдвига четырёхразрядный, количество возможных комбинаций на входе составит 16. Рассмотрим работу нашего регистра при подаче на вход некоторых комбинаций.

| № комбинации |

Вход |

Выход |

|||||||

| D1 |

D2 |

D3 |

D3 |

№ синхроимпульса |

Q1 |

Q2 |

Q3 |

Q4 |

|

| 1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

| 1 |

1 |

1 |

0 |

1 |

|||||

| 2 |

1 |

1 |

1 |

0 |

|||||

| 3 |

0 |

1 |

1 |

1 |

|||||

| 4 |

1 |

0 |

1 |

1 |

|||||

| 2 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

| 1 |

1 |

0 |

0 |

1 |

|||||

| 2 |

1 |

1 |

0 |

0 |

|||||

| 3 |

0 |

1 |

1 |

0 |

|||||

| 4 |

0 |

0 |

1 |

1 |

|||||

| 3 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

| 1 |

1 |

0 |

0 |

0 |

|||||

| 2 |

0 |

1 |

0 |

0 |

|||||

| 3 |

0 |

0 |

1 |

0 |

|||||

| 4 |

0 |

0 |

0 |

1 |

|||||

| 4 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

| 1 |

0 |

0 |

1 |

1 |

|||||

| 2 |

1 |

0 |

0 |

1 |

|||||

| 3 |

1 |

1 |

0 |

0 |

|||||

| 4 |

0 |

1 |

1 |

0 |

|||||

5. Вывод

В курсовом проекте было рассмотрено классификацию регистров, принципы их работы. Рассмотрено типы и принцип работы триггеров как главных составляющих регистров. Было детально рассмотрено регистры сдвига и, в частности, сдвиговые регистры на RS-триггерах.

Также был спроектирован правосдвигающий кольцевой синхронный четырёхразрядный регистр на базе четырёх RS-триггеров и восьми логических элементов. Приведена таблица, описывающая работу регистра при некоторых входных комбинациях.

6. Список используемой литературы

1. Прянишников В.А. Электроника (курс лекций). – С-П., 1998

2. Скаржепа В.А., Луценко А.Н. Электроника и микросхемотехника (часть первая). – К.: Высшая школа, 1989

3. Будищев М.С. Электротехника, электроника и микропроцессорная техника. – Л.: Афиша, 2001

4. Угрюмов Е.П. Цифровая схемотехника. – С-П., 2000

5. Справочник современных интегральных микросхем