| Похожие рефераты | Скачать .docx |

Реферат: Цифровые устройства

1.14.1. RS – Триггер.

RS - Триггер имеет два входа S и R, основной и инверсный выходы. Состояние триггера определяется по сигналу на основном входе. Вход S называется входом установки, а вход R входом сброса. При подаче управляющего сигнала на вход S на основном входе устанавливается логическая единица или эта единица подтверждается, если она там была. При подаче управляющего сигнала на вход R на основном входе появляется логический ноль, как говорят, триггер сбрасывается. Если триггер был уже сброшен , то сброс подтверждается. Подача управляющих сигналов одновременно на входы S и R запрещена. В отсутствии управляющих сигналов состояние триггера измениться не может, триггер находится в режиме хранения информации. В зависимости от типа логических элементов, на которых собран триггер, управляющими сигналами могут быть, как нули, так и единицы. На рис.1.14.1 показана таблица функционирования RS – триггера.

В таблица Qt это значение выходного сигнала к моменту подачи управляющих сигналов St и Rt , или его исходное состояние. Qt+1 – новое состояние триггера после подачи управляющих сигналов, которыми являются логические единицы.

|

St |

Rt |

Qt+1 |

|||||

|

|

0 |

0 |

0 |

Хранение информации |

||||

|

|

0 |

1 |

0 |

Подтверждение 0 |

0 |

1 |

Х1 |

0 |

| 0 |

1 |

0 |

1 |

Установка в 1 |

||||

|

|

1 |

1 |

Х |

Запрет |

1 |

1 |

Х1 |

0 |

| 1 |

0 |

0 |

1 |

Хранение информации |

||||

|

|

0 |

1 |

0 |

Сброс в 0 |

||||

| 1 |

1 |

0 |

1 |

Подтверждение 1 |

||||

| 1 |

1 |

1 |

Х |

Запрет |

Рис 1.14.1

На рис 1.14.1 показана процедура минимизации функции Qt+1

с использованием карты Карно, полученная формула описывает работу RS триггера, но схемы триггеров строят после преобразования этой формулы, заменяя операцию умножения на сложение или сложение заменяют умножением. После замены умножения на сложение по 16-й теореме Булевой алгебры можно получить следующую формулу ![]() .

.

Если заменить сложение на умножение, то получим ![]() . Схемы триггеров, построенные по этим формулам показаны на рис 1.14.2. Первая из схем построена на элементах ИЛИ-НЕ, этот триггер управляется логическими единицами. Таблица его функционирования приведена на рис. 1.14.1. Схема триггера построена по второй формуле на элемента И-НЕ самая распространенная , этот триггер управляется логическими нулями, т.е. имеет инверсные входы. Таблица его функционирования показана на рис 1.14.2.

. Схемы триггеров, построенные по этим формулам показаны на рис 1.14.2. Первая из схем построена на элементах ИЛИ-НЕ, этот триггер управляется логическими единицами. Таблица его функционирования приведена на рис. 1.14.1. Схема триггера построена по второй формуле на элемента И-НЕ самая распространенная , этот триггер управляется логическими нулями, т.е. имеет инверсные входы. Таблица его функционирования показана на рис 1.14.2.

| Qt |

St |

Rt |

Qt+1 |

|

| 0 |

0 |

0 |

Х |

Запрет |

| 0 |

0 |

1 |

1 |

Установка в 1 |

| 0 |

1 |

0 |

0 |

Подтверждение 0 |

| 0 |

1 |

1 |

0 |

Хранение информации |

| 1 |

0 |

0 |

Х |

Запрет |

| 1 |

0 |

1 |

1 |

Подтверждение 1 |

| 1 |

1 |

0 |

0 |

Сброс |

| 1 |

1 |

1 |

1 |

Хранение информации |

Рис.1.14.2

Рис.1.14.2

|

На рис 1.14.3 показаны временные диаграммы переключения RS – триггера с инверсными входами с учетом задержки переключения каждого элемента на tзад.ср. Из временных диаграмм видно, что задержка полного переключения триггера равна 2tзад.ср .

Рис.1.43.3

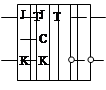

RS – триггер может быть синхронным. В этом случае кроме двух информационных входов S и R триггер имеет еще вход синхронизации. Сигналы на входах S и R лишь подготавливают триггер к нужному переключению, а само переключение происходит только в момент подачи синхронизирующего импульса. Схема такого триггера показана на рис 1.14.4. Синхронизация организуется с помощью двух дополнительных элементов И-НЕ D1 и D2. Элементы D3 и D4 образуют несинхронный (асинхронный) RS – триггер с инверсными входами.

При отсутствии сигнала синхронизации ( С = 0 ) на входах асинхронного RS – триггера устанавливаются две единицы, что обеспечивает в нем хранение информации. При подаче синхронизирующего сигнала ( С = 0 ) триггер переключается соответственно поданной информации на входы S и R.

|

|

Рис. 1.14.4

1.14.2 D – триггер.

|

|

D – триггер, называемый еще триггером задержки может быть асинхронным и синхронным, но асинхронный D – триггер смысла не имеет, т.к. имеет один информационный вход D и основной и инверсный выходы. Сигнал (информация ) на выходе всегда совпадает с информацией на входе, т.е. Qt+1 = Dt . Смысл имеет только синхронный D – триггер, у которого кроме информационного входа D есть вход синхронизации С. Информация со входа D передается на основной выход (записывается в триггер) в момент прихода синхронизирующего импульса. Структурная формула, описывающая работу синхронного D – триггера следующая:

Рис 1.14.5

1.14.3 Т – триггер

Несинхронный Т – триггер имеет один вход Т, основной и инверсный выходы. Входной импульс переключает триггер в противоположное состояние. Структурная формула, описывающая работу Т- триггера имеет следующий вид:![]() . У синхронного Т – триггер

. У синхронного Т – триггер ![]() а есть еще вход синхронизации. Этот триггер переключается сигналом на входе Т в противоположное состояние только при наличии логической единицы на входе синхронизации С. Т –триггер называют «счетным» триггером, т.к. делит частоту следования управляющих импульсов в два раза, или, как говорят, «пересчитывает» их вдвое.

а есть еще вход синхронизации. Этот триггер переключается сигналом на входе Т в противоположное состояние только при наличии логической единицы на входе синхронизации С. Т –триггер называют «счетным» триггером, т.к. делит частоту следования управляющих импульсов в два раза, или, как говорят, «пересчитывает» их вдвое.

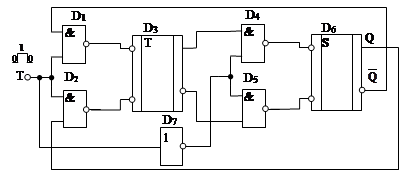

На рис 1.14.6 показана схема Т – триггера с элементами задержки. Основным признаком Т – триггера является подача на информационные входы синхронного RS триггера входящего в состав Т – триггера, информации с выходов этого же триггера.

|

Рис 1.14.6

Если триггер перед подачей очередного входного импульса был сброшен, то логическая единица с его инверсного входа поступает на информационный вход S синхронного RS – триггера (верхний вход элемента D1 ) и поэтому триггер переключается в состояние «единица». При единичном исходном состоянии единица с основного выхода поступает на вход сброса синхронного RS – триггера и триггер сбрасывается в «0», т.е. опять переключается в противоположное состояние.

|

Устройства задержки в схеме триггера необходимы для того, чтобы легче было выполнить условие tU вх < tпер.тр. Длительность входного импульса обязательно должна быть меньше времени переключения триггера, т.к. в противном случае триггер может переключиться не один раз под действием одного входного импульса. Создать управляющий импульс короче времени переключения триггера довольно сложно. Введение задержки, увеличивающей время переключения уменьшает требования к длительности входного импульса, но создает усложнение схемы, особенно при её миниатюризации, т.к. конденсаторы, входящие в состав элементов задержки плохо миниатюризируются. На рис 1.14.7 показана схема двухступенчатого триггера, свободного от этого недостатка.

Рис 1.14.7

Двухступенчатый Т – триггер состоит из двух синхронных RS – триггеров и инвертора. При подаче первого перепада из 0 в1 входного импульса переключается в противоположное состояние только первая ступень всего триггера ( первый RS – триггер на элементах D1 ,D2 ,D3 ). Вторая ступень не меняет своего состояния, т.к. логическая единица со входа триггера через инвертор D7 поступает на элементы D4 и D5 и обеспечивает на инверсных входах RS –триггера D6 две единицы и, следовательно, хранение информации на выходе Т – триггера. При окончании входного импульса логический ноль на входе сохраняет состояние первой ступени триггера, но меняется на противоположное второй ступени, т.е. всего Т – триггера. Такое управление триггером, когда переключение происходит только под действием импульса, т.е. под действием двух перепадов напряжения называется динамическим управлением. На рис 1.14.7 показаны условные обозначения двух типов Т – триггеров с динамическим входом. Верхний триггер имеет динамический инверсный вход. Это означает, что триггер переключается перепадом из 1 в 0. Рассмотренный триггер имеет такой вход. Другой триггер имеет прямой динамический вход, это означает, что он переключается перепадом из 0 в 1, а перепадом из 1 в 0 переключается только первая ступень триггера.

Т – триггер может быть построен на D – триггере. Если в структурной формуле D – триггера приравнять D к ![]() то получим

то получим ![]() . Полученная формула совпадает с формой Т – триггера. Вход С D – триггера играет роль входа Т Т – триггера. Следовательно для получения Т – триггера на основе D – триггера достаточно соединить вход D с инверсным выходом, а вход синхронизации С использовать как вход Т – триггера.

. Полученная формула совпадает с формой Т – триггера. Вход С D – триггера играет роль входа Т Т – триггера. Следовательно для получения Т – триггера на основе D – триггера достаточно соединить вход D с инверсным выходом, а вход синхронизации С использовать как вход Т – триггера.

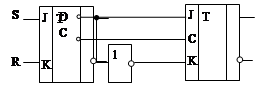

1.14.4 Универсальный JK –триггер.

Несинхронный JK – триггер имеет два входа J и K, основной и инверсные входы. Вход J аналогичен входу S RS – триггера. По этому входу триггер устанавливается в состояние «1». По входу K триггер сбрасывается в «0», как и RS – триггер по входу R. Отличие от RS – триггера состоит в том, что этот триггер не имеет запрещенных комбинаций сигналов на входах, а при подаче управляющих сигналов одновременно на оба входа триггер переключается в противоположное состояние. Синхронный JK – триггер имеет еще один вход С – вход синхронизации и переключается только при подаче импульса на этот вход.

Структурная формула, описывающая работу несинхронного JK – триггера имеет следующий вид: ![]() . JK – триггер называют универсальным, т.к. из него можно сделать любой тип триггера. RS – триггер получается из JK – триггера, когда входы JK используются, как входы S и R соответственно, а запрещенная комбинация не подается.

. JK – триггер называют универсальным, т.к. из него можно сделать любой тип триггера. RS – триггер получается из JK – триггера, когда входы JK используются, как входы S и R соответственно, а запрещенная комбинация не подается.

Если в формуле несинхронного JK – триггера J назвать входом D, а на вход K подать ![]() , то получим:

, то получим: ![]() , что соответствует несинхронному D – триггеру, но т.к. несинхронный D – триггер смысла не имеет, то для получения синхронного D – триггера нужно использовать синхронный JK – триггер. Для получения T – триггера достаточно объединить входы J и K и назвать этот вход входом Т по которому триггер будет переключаться в противоположное состояние, как это должен делать Т – триггер. На рис 1.14.8 показано условные обозначения JK – триггеров и выполнение на основе JK – триггеров другие типы триггеров.

, что соответствует несинхронному D – триггеру, но т.к. несинхронный D – триггер смысла не имеет, то для получения синхронного D – триггера нужно использовать синхронный JK – триггер. Для получения T – триггера достаточно объединить входы J и K и назвать этот вход входом Т по которому триггер будет переключаться в противоположное состояние, как это должен делать Т – триггер. На рис 1.14.8 показано условные обозначения JK – триггеров и выполнение на основе JK – триггеров другие типы триггеров.

|

|

|

|

|

несинхр. RS – триггер Т – триггер

синхр. D – триггер

Рис 1.14.8

1.14.4 Регистры.

Регистром называют последовательное устройство предназначенное для хранения небольшого объёма цифровой информации (числа). Один из типов регистров, последовательный регистр, позволяет производить над этим числом арифметические операции умножения и деления.

Процедура ввода числа в регистр называется записью. Процедура вывода числа называется считыванием. По способу записи и считывания различают следующие типы регистр: 1. Параллельный регистр, в котором и запись и считывание производят в параллельном коде, т.е. во все разряды одновременно записывается число и одновременно со всех разрядов считывается. 2. Последовательный регистр, в котором и запись и считывание производятся в последовательном коде, т.е. последовательно разряд за разрядом. 3. Параллельно – последовательный регистр, в котором запись производится в параллельном коде, а считывание в последовательном. 4. Последовательно – параллельный, в котором запись производится в последовательном коде, а считывание в параллельном.

Рассмотрим примеры построения схем перечисленных типов регистров.

1.

|

Параллельный регистр на D – триггерах.

Рис 1.14.9

Информация (число) записывается во все разряды регистра, во все D – триггеры одновременно, т.е. параллельным кодом. В приведенной на рисунке схеме считывание выполняется с использованием элементов И – НЕ, часть из которых превращается в инверторы путем объединения двух входов. При отсутствии сигнала считывания, которым является логическая единица, т.е. при нуле на входе считывания, на всех выходах установятся логические нули. При единице на входе «счит.» число на выходах будет равно числу, записанному в триггерах.

2. Последовательный регистр.

последовательный регистр строится на D – триггерах путем соединения выхода каждого триггера со входом «D» следующего. Для записи и считывания одновременно на входы синхронизации всех триггеров подаются тактовые импульсы «ТИ» рис 1.14.10

|

Рис 1.14.10

Первым тактовым импульсом первая единица старшего разряда числа 101 записывается в первый триггер. Вторым тактовым импульсом в первый триггер записывается значение следующего разряда (в нашем примере 0), а во второй триггер записывается единица, которая была перед приходом второго тактового импульса на выходе первого триггера.

Таким образом каждый тактовым импульсом в регистре происходит сдвиг числа на один разряд. Трехразрядное число будет полностью записано в регистр после третьего тактового импульса. При этом на выходе регистра можно просчитать значения разряда, который был записан первым. Для считывания значений следующих двух разрядов нужно подать ещё два тактового импульса. В двоичной системе счисления при сдвиге числа на один разряд в сторону старших разрядов происходит увеличения числа в два раза. При сдвиге числа в сторону младших разрядов число записывается в регистр уменьшается в два раза. Таким образом сдвигающий регистр можно использовать для умножения или деления числа на 2n , где n – количество сдвигов равное количеству под тактовых импульсов.

3. Параллельно – последовательный регистр.

|

В параллельно – последовательном регистре запись информации происходит в параллельном коде, а считывание в последовательном. На рис 1.14.11 показан пример построения такого регистра на JK – триггерах.

Рис 1.14.11

В приведенной схеме JK – триггеры дважды превращены в D – триггеры. Одно превращение осуществлено для организации записи с использованием вспомогательных инверсных входов S и R и, добавлением двух элементов И –НЕ. Этот способ построения триггера показан на рис 1.14.5. Запись числа в регистр в параллельном коде происходит при подаче числа на входы х1 , х2 , х3 и сигнала «1» на вход «зап». Для считывания информации из регистр в последовательном коде JK – триггеры второй раз превращены в D – триггеры у которых выходы каждого триггера соединены со входом D следующего, как это делается в последовательном регистре. Во втором случае JK – триггеры превращены в D – триггеры способом показанном на рис 1.14.8, но вместо дополнительного инвертора используется инверсный выход предыдущего триггера. Исключение составляет первый триггер, у которого входы J и K объединены и соединены с основным входом этого же триггера. Благодаря такой схеме после подачи импульсов считывания первый триггер оказывается в состоянии «0».

4. Последовательно – параллельный регистр.

Для построения последовательно – параллельного регистра достаточно в последовательном регистре организовать параллельное считывание используя дополнительные элементы И – НЕ, как это показано на рис 1.14.12.

|

Рис. 1.14.12

При подаче сигнала «1» на вход «счит» значение разрядов числа с инверсных выходов триггеров поступают на выходы У1 , У2 , У3 через элементы И – НЕ.

1.14.6 Счетчики импульсов.

Счетчиком называется устройство, предназначенное для подсчета числа импульсов, поступающих на его вход, и фиксации этого числа в виде кода, хранящегося в триггерах. Счетчик относится к последовательным логическим устройствам. Число разрядов счетчика определяется наибольшим числом подсчитываемых импульсов. В счетчиках имеется один вход и n выходов по числу разрядов. Для установки начального состояния счетчика (сброс в ноль) обычно предусматривается вход сброса.

По назначению счетчики могут быть суммирующими, вычитающими и реверсивными.

Суммирующие счетчики производят сложение чисел поступающих на вход импульсов с тем числом, которое хранилось в нем.

Вычитающие счетчики производят вычитание числа поступающего импульса из начального числа, записанного в нем заранее.

Реверсивные счетчики могут производить как сложение, так и вычитание поступающих на вход импульсов в зависимости от управляющих сигналов, меняющих режим работы счетчика.

По способу переноса сигнала в старший разряд счетчики могут быть с последовательным, параллельным и сквозным переносом.

Счетчики отличаются друг от друга кодом, в котором они работают. Код всегда бывает двоичным, но может иметь различные веса разрядов, например вес 8421 или 5211 и т.п., двоично-десятичным, когда значение каждого разряда десятичного числа кодируется двоичным кодом.

Счетчики бывают синхронными, когда счетные импульсы подаются счетные входы всех триггеров, и асинхронными, когда сигнал на счетный вход какого-либо триггера подается с выхода одного из триггеров младших разрядов.

Счетчики строятся на Т – триггерах или на универсальных JK – триггерах.

Максимальное число, которое может быть записано в счетчике, равно числу его состояний и называется модулем счета Ксч . Счетчик , не имеющий дополнительных связей , имеет модуль счета Ксч = 2n . Счетчики, имеющие модуль счета 2n , называются двоичными. Если Ксч ¹ 2n , то счетчик называется не двоичным. Одним из недвоичных является двоично-десятичный счетчик.

1. Суммирующий двоичный асинхронный счетчик с последовательным переносом.

|

Схема двоичного счетчика с последовательным переносом на JK – триггерах, работающего в коде 8421, показана на рис 1.14.13. Здесь JK – триггеры превращены в Т – триггеры путем подачи «1» на вход J и K .

Рис. 1.14.13

Поскольку триггеры имеют инверсный динамический вход, то каждый последующий триггер будет переключаться при сбросе в «0» предыдущего триггера. Важным параметром счетчика является его максимальное время установления кода, т.е. время, необходимое для установления кода после подачи счетного импульса. В схемах счетчиков с последовательным переносом максимальное время установления Туст определяется суммой времени задержки переключения всех триггеров. Время установления Туст определяет быстродействие счетчика. Счетчики с последовательным переносом обладают сравнительно плохим быстродействием.

2. Суммирующий двоичный счетчик с последовательным переносом.

Наличие сигнала переноса в старший разряд определяется выражениями:

P12 = Q1 ×C1 ; P23 = Q1 ×Q2 ×C; P34 = Q1 ×Q2 ×Q3 ×C,

, где Р12 – сигнал переноса из первого разряда во второй; Р23 – сигнал переноса из второго разряда в третий и т.п.

Для любого разряда Pn(n+1) = Q1 ×Q2 ×Q3 , …, Qn ×C . В схеме счетчика с параллельным переносом сигналы переноса в каждый разряд формируются согласно приведенным формулам.

Схема счетчика с параллельным переносом показана на рис 1.1.4.14.

Рис. 1.14.14

Время установления кода при параллельной организации переноса определяется задержкой переключения одного триггера и временем задержки срабатывания схем И и существенно меньше, чем при последовательном переносе.

Недостатком параллельного переноса является то, что при большом числе разрядов требуются схемы И с большим числом входов.

2. Суммирующий счетчик со сквозным переносом.

|

При сквозном переносе триггеры счётчика объединяются в группы, внутри каждой группы осуществляется параллельный перенос, а между группами – последовательный. На рис 1.14.15 представлена схема счетчика со сквозным переносом, каждая группа которого содержит по два триггера. При такой организации переноса все схемы умножения должны быть двухвходовыми. Время установления кода в счетчике со сквозным переносом определяется задержкой переключения триггера, задержка переключения схем И и инвертора в одной группе и количеством групп. Таким образом, быстродействие такого счетчика является промежуточным между быстродействиями счетчиков с последовательным и параллельным переносом.

4. Реверсивный счётчик.

|

Для построения вычитающего счетчика достаточно подать сигнал переноса на триггер старшего разряда не с прямого выхода предыдущего триггера, а с инверсного.

Связи между триггерами реверсивного счётчика соответствуют как суммирующему, так и вычитающему счётчику, но работает только одна из связей, которая определяется командой «Реверс» и подается на элемент И–НЕ, включенные в цепи передачи сигнала переноса. Схема реверсивного счётчика показана на Рис 1.14.16.

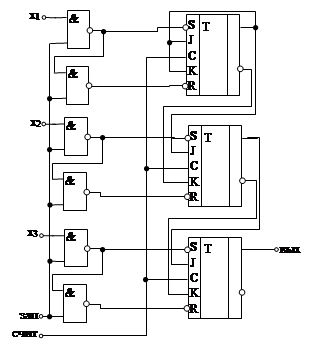

Пример синтеза двоично-десятичного счетчика.

Пусть требуется синтезировать асинхронный счетчик, работающий в коде 5-2-1-1. В соответствии с заданным кодом заполняем левую часть табл. 1 функционирования счётчика (столбцы Q4 , Q3 , Q2 , Q1 , n).

Таблица 1

| . n |

Q4 |

Q3 |

Q2 |

Q1 |

J1 |

K1 |

J2 |

K2 |

J3 |

K3 |

J4 |

K4 |

| 0 |

0 |

0 |

0 |

0 |

1 |

- |

0 |

- |

- |

- |

- |

- |

| 1 |

0 |

0 |

0 |

1 |

- |

0 |

1 |

- |

- |

- |

- |

- |

| 2 |

0 |

0 |

1 |

1 |

- |

0 |

- |

1 |

1 |

- |

- |

- |

| 3 |

0 |

1 |

0 |

1 |

- |

0 |

1 |

- |

- |

- |

- |

- |

| 4 |

0 |

1 |

1 |

1 |

- |

1 |

- |

1 |

- |

1 |

1 |

- |

| 5 |

1 |

0 |

0 |

0 |

1 |

- |

0 |

- |

- |

- |

- |

- |

| 6 |

1 |

0 |

0 |

1 |

- |

0 |

1 |

- |

- |

- |

- |

- |

| 7 |

1 |

0 |

1 |

1 |

- |

0 |

- |

1 |

1 |

- |

- |

- |

| 8 |

1 |

1 |

0 |

1 |

- |

0 |

0 |

- |

- |

- |

- |

- |

| 9 |

1 |

1 |

1 |

1 |

- |

1 |

- |

1 |

- |

1 |

- |

1 |

В таблице n – номер состояния счетчика, меняющийся на единицу при подаче каждого счетного импульса; Q1 , Q2 , Q3 и Q4 – логические переменные на выходе четырех триггеров, первый триггер с выходом Q1 соответствует первому младшему разряду; J и K – значения соответствующих сигналов на соответствующих входах JK – триггеров.

Каждый из универсальных триггеров может переключаться при подаче на вход С положительного («одиночного») импульса либо при подаче сигнала на вход С с выхода другого триггера. При этом переключение последующего триггера происходит тогда, когда предыдущий переключается из «1» в «0». Учитывая это, находим необходимое место подключения входов С всех четырех триггеров. Первый триггер должен переключаться при подаче первого, пятого и нулевого (десятого) импульса. Ни один из последующих триггеров не может обеспечить всех трех переключений. Поэтому на вход С первого триггер нужно подавать счетные импульсы. Они обеспечивают максимальную частоту переключений, а выборка нужных моментов переключения обеспечивается подачей сигналов на вход J и K .

На вход с второго триггера также нужно подать счетные импульсы, так как выходные сигналы ни одного из триггеров не обеспечат его переключения в нужный момент.

Вход С третьего триггера нужно соединить с выходом второго, так как его переключение при подаче третьего, пятого, восьмого триггера в эти моменты времени из «1» в «0».

По тем же соображениям выход третьего триггера нужно соединить со входом четвертого. Для определения сигналов на входах J и K заполняют правую часть табл. 1, используя таблицу функционирования JK – триггера (табл. 2). Почерк в таблице показывает, что значение сигнала в данном виде не вызывает изменения или сохранения состояния триггера. Например, для переключения первого триггера из «0» в «1» при подаче первого счетного импульса требуется, чтобы J1 = 1 в позиции n = 0,а значения K1 может быть любым, что означает прочерк. Если при очередном такте работы на какой – либо триггер сигнал переноса не подается, т.е. триггер, с которого он может прийти, не сбрасывается в «0», то в соответствующих клетках J и K можно ставить прочерки, так как при любых значениях J и K триггер не переключается. Таким способом заполняется

|

Таблица 2

Таблица 2

| Qn ® Qn+1 |

Jn |

Kn |

| 0 0 |

0 |

- |

| 0 1 |

1 |

- |

| 1 0 |

- |

1 |

| 1 1 |

- |

0 |

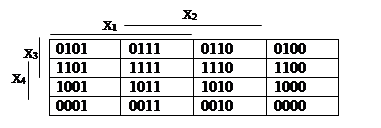

Перенесем теперь данные правой части табл. 1 на диаграммы Вейча. В табл. 3 приведена диаграмма Вейча для четырех логических переменных. Принимаем за логические переменные значения сигналов на выходах триггеров и заполним восемь диаграмм Вейча (табл. 4), по которым определим сигналы на входах J и K четырех триггеров. При заполнении диаграмм единицы, нули или прочерк ставятся в тех клетках, в которых находятся соответствующие комбинации выходных переменных Q.

Таблица 4

Таблица 4

J1

| - |

- |

- |

- |

| - |

- |

- |

- |

| - |

- |

- |

1 |

| - |

- |

- |

1 |

В клетках, в которых функция не определена или её значение не играет роли (т.е. ставится прочерк), можно помещать любые значения переменных, чтобы объединить контуром наибольшее количество клеток. Так, в табл. 4 для J1

во всех клетках можно поставить единицы и объединить одним контуром. Это означает, что J1

= 1.из всех других диаграмм следует, что K1

= Q2

Q3

, J2

=Q1

, K2

= 1, J3

= 1, K3

=1, J4

=1, K4

= 1. Следовательно, на входы J1

, K2

, J3

, K3

, J4

, K4

надо подать единицы, на вход K1

– конъюнкцию сигналов с прямых выходов второго и третьего триггеров, а вход J2

соединить с прямым выходом первого триггера. Если какой либо вход не куда не подключен, это эквивалентно подаче на этот вход единицы. Таким образом, счетчик синтезирован. Его схема показана на рис. 1.14.17.

В клетках, в которых функция не определена или её значение не играет роли (т.е. ставится прочерк), можно помещать любые значения переменных, чтобы объединить контуром наибольшее количество клеток. Так, в табл. 4 для J1

во всех клетках можно поставить единицы и объединить одним контуром. Это означает, что J1

= 1.из всех других диаграмм следует, что K1

= Q2

Q3

, J2

=Q1

, K2

= 1, J3

= 1, K3

=1, J4

=1, K4

= 1. Следовательно, на входы J1

, K2

, J3

, K3

, J4

, K4

надо подать единицы, на вход K1

– конъюнкцию сигналов с прямых выходов второго и третьего триггеров, а вход J2

соединить с прямым выходом первого триггера. Если какой либо вход не куда не подключен, это эквивалентно подаче на этот вход единицы. Таким образом, счетчик синтезирован. Его схема показана на рис. 1.14.17.

|

Рис 1.14.17

Синтез синхронных счетчиков производится аналогично, но счетные импульсы подаются на входы С всех триггеров, поэтому при подаче каждого счетного импульса в каждом триггере нужно обеспечивать нужные значения J и K.

Похожие рефераты:

Техническая диагностика средств вычислительной техники

Методы позиционирования и сжатия звука

Ответы к Экзамену по Микропроцессорным Системам (микроконтроллеры микрокопроцессоры)

Беспроводные телекоммуникационные системы

Машины, которые говорят и слушают

0

0