| Похожие рефераты | Скачать .docx |

Реферат: Триггеры

Общие сведения о триггерах

Триггер — логическое устройство, способное хранить 1 бит данных. К триггерным принято относить все устройства, имеющих два устойчивых состояния. В основе любого триггера находится кольцо из двух инверторов, показанное на рис.12.1. Общепринято это кольцо изображать в виде так называемой защелки, которая показана на рис.12.2.

Рис.12.1. Кольцо из двух инверторов

Рис.12.2. Изображение бистабильного элемента защелки

В настоящее время существует много разновидностей триггерных схем. Все они появились как результат разработки новых цепей запуска. Состояние триггера определяется значением выходного сигнала Q . Если изменение Q , т.е. переключение триггера, происходит только при поступлении синхронизирующего сигнала (синхроимпульса), то триггер называется синхронным. Триггеры могут синхронизироваться уровнем или фронтом синхроимпульсов . Триггеры, синхронизируемые уровнем, могут изменять свое состояние в течении длительности синхроимпульса (уровня синхросигнала) при поступлении соответствующих управляющих сигналов, т.е. могут могут переключаться несколько раз за время действия одного синхроимпульса. В течение паузы между синхроимпульсами состояние такого триггера сохраняется при любых изменениях управляющих сигналов.

Триггеры, синхронизируемые фронтом, изменяют свое состояние при поступлении на синхронизирующий вход соответствующего фронта (положительного или отрицательного) синхроимпульса, а затем это состояние сохраняется при любых изменениях управляющих сигналовю За время действия одного синхроимпульса, триггер, синхронизируемый фронтом, может переключаться только один раз. В асинхронных триггерах отсутствует вход синхронизации. Поэтому переключение таких триггеров происходит когда на управляющие входы поступает соответствующая комбинация управляющих сигналов.

RS - триггер

RS ‑триггер имеет два входа раздельной установки в нулевое и единичное состояния. Воздействия по входу S (от слова SET - установка) приводит триггер в единичное состояние, а воздействие по входу R (от слова RESET - сброс) – в нулевое. Одновременная подача сигналов S и R не допускается.

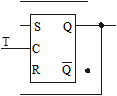

На рис.12.3 показано условное графическое обозначение RS ‑триггера.

Рис.12.3. Условное графическое обозначение RS ‑триггера

Тип триггера определяется по его характеристическому уравнению , которое указывает значение выходного сигнала Qn+1 после переключения триггера (в момент времени tn+1 ) в зависимости от значений управляющих сигналов и выходного сигнала Qn до переключения триггера ( в момент времени tn ).

В соответствие с таблицей характеристическое уравнение RS ‑триггера имеет вид:

![]()

При S=R=0 (режим хранения) – состояние выхода триггера не меняется: Qn+1=Qn

RS ‑триггер может быть получен из двух логических элементов И‑НЕ (рис.12.4).

Рис.12.4. RS – триггер на двух логических элементах И‑НЕ

Временные диаграммы показывают уровни напряжения и временные интервалы между входными и выходными сигналами и соответствуют той картине, которую можно наблюдать на экране осциллографа. По горизонтали откладывается время, по вертикали – уровень напряжения.

Временные диаграммы для различных режимов установки RS ‑триггера показаны на рис.12.5.

Рис.12.5. Временные диаграммы сигналов для RS ‑триггера

Тактируемый (синхронный) RS ‑триггер

В тактируемых (синхронных) устройствах процесс переработки информации упорядочивается во времени с помощью специальных тактовых сигналов, вырабатываемых общим для всего устройства генератором.

Отличия тактируемого RS ‑триггера от обычного RS ‑триггера состоит в появление одного дополнительного синхронизирующего входа. Условное графическое изображение тактируемого RS ‑триггера показано на рис.12.6.

Рис.12.6. Условное графическое изображение тактируемого RS ‑триггера

Из таблицы истинности (табл.12.2) видно, что только три верхние строки таблицы описывают реальные режимы работы тактируемого RS ‑триггера. Нижняя строка соответствует запрещенному состоянию, которое никогда не используется.

Для получения тактируемого RS ‑триггера нужно ввести два дополнительных элемента И‑НЕ (рис.12.7).

Таблица 12.2. Таблица истинности для тактируемого RS ‑триггера

Рис.12.7. Тактируемый RS ‑триггер на четырех элементах И‑НЕ

Рассмотрим временные диаграммы, которые иллюстрируют принцип работы тактируемого RS ‑триггера (рис.12.8).

Рис.12.8. Временные диаграммы сигналов для тактируемого RS ‑триггера

Синхронизирующему входу соответствует самая верхняя диаграмма. Тактовый импульс 1 не оказывает никакого влияния на состояние выхода Q , когда на обоих входах R и S установлен уровень логического 0 . Во время прохождения импульса 1 триггер находится в режиме хранения. В момент предварительной установки (предустановки) входа 5 , когда на этот вход подается логическая 1 , выход Q все ещё остается в прежнем состояние Q=0 , и только на фронте (нарастающем крае) тактового импульса 2 происходит его переключение к 1 . Тактовые импульсы 3 и 4 не влияют на состояние выхода Q . Во время прохождения импульса 3 , триггер находится в режиме установки 1 , во время прохождения импульса 4 - в режиме хранения. Затем логическая 1 подается на вход R (предустановка входа R ). На фронте импульса 5 происходит сброс (очистка) выхода Q путем установки его в состояние 0 . Во время прохождения импульсов 5 и 6 триггер находится в режиме установки 0 , во время прохождения импульса 7 – в режиме хранения.

Из временных диаграмм (рис.12.8) видно, что состояние выходов тактируемого RS ‑триггера может изменяться только в моменты прихода тактовых импульсов. В этом случае триггер работает синхронно, т.е. процесс переключения его выходов находится в синхронизме с тактовыми импульсами.

Важную роль во многих цифровых схемах играет такая характеристика RS ‑триггера, как наличие памяти. Если триггер установлен в состояние 1 или 0 , то он остается в этом состояние даже при некоторых изменениях входных сигналов. Такое свойство триггера проявляется в режиме хранения. Из временных диаграмм (рис.12.8) видно, что этот режим реализуется во время прохождения тактовых импульсов 1 , 4 и 7 .

Изменение состояний триггера при поступлении различных последовательностей входных (управляющих и синхронизирующих) сигналов представляются с помощью графа переходов .

Рассмотрим граф переходов (рис.12.9) для RS ‑триггера, синхронизируемого положительным фронтом (С=0 1 ) синхросигнала.

Рис.12.9. Графы переходов RS ‑триггера, синхронизируемого фронтом

На рис.12.9 кружками, в которых указаны значения выходного сигнала Q , обозначены устойчивые состояния триггера. Стрелками показаны переходы из одного состояния в другое, при поступление соответствующих комбинаций входных сигналов. Если данная комбинация не вызывает изменения Q , то стрелка замыкается на исходном состоянии. Триггер, синхронизируемый фронтом имеет по два различных состояния, соответствующих Q=0 и Q=1 , которые помечены индексами А и В . Изменение значения Q происходит при поступление перепада С=0 1 , если предварительно при С=0 на управляющих входах установлены соответствующие комбинации: RS=10 или 01 . Поэтому граф переходов имеет промежуточные состояния 0В , 1В , в которые триггер переводится перед переключением. D ‑триггер

D ‑триггер (от слова delay -задержка) принимает информацию по одному входу. Его состояние повторяет входной сигнал, но с задержкой, определяемой тактовым сигналом.

Условное графическое обозначение D ‑триггера показано на рис.12.10.

Рис.12.10.Условное графическое обозначение D ‑триггера

Табл.12.3 показывает, что сигнал на выходе Q в такте n+1 (Qn+1 ) повторяет сигнал, который был на входе D в предыдущем такте n (Dn ).

Таблица 12.3.Таблица истинности для D ‑триггера

D ‑триггеры бывают только синхронными. В соответствии с табл.12.3, характеристическое уравнение D ‑триггера имеет вид:

Qn+1 =Dn

Граф перехода для D

‑триггера, синхронизируемого положительным фронтом ![]() синхросигнала, показан на рис.12.1.

синхросигнала, показан на рис.12.1.

Рис.12.11. Граф переходов D ‑триггера, синхронизируемого положительным фронтом синхросигнала

На рис.12.11 в кружках указаны значения выходного сигнала Q . В знаменателях дробей показаны промежуточные состояния, в которые триггер переводится перед переключением. Стрелками показаны переходы триггера из одного состояния в другое при поступлении соответствующих комбинаций входных сигналов С и D . D ‑триггер можно получить из тактируемого RS ‑триггера, путем добавления инвертора (рис.12.11).

Рис.12.12.Схема D ‑триггера

Серийно выпускаемые D ‑триггеры имеют два дополнительных входа: предварительной установки (S ) и очистки (R ). Название этих входов происходит от английских слов PRESET (предустановка) и CLEAR (очистка).

Условное графическое обозначение D ‑триггера с двумя дополнительными входами показано на рис.12.13.

Рис.12.13. Условное графическое обозначение D ‑триггера с двумя дополнительными входами

Логический 0 на входе S инициирует установку логической 1 на выходе Q . Логический 0 на входе R инициирует очистку выхода Q (установку логического 0 на выходе Q ). В активных состояниях входы S и R блокируют действия входов D и C . При разблокировании входы D и С действуют так, как и в обычном D -триггере. В таблице истинности (табл.12.4) входы разделяются на асинхронный и синхронный. Асинхронные входы S и R в активных состояниях блокируют действия синхронных входов (D и C ). Первые три строки табл.12.4 описывают режимы, в которых работа триггера контролируется асинхронными входами. При этом синхронные входы (D и C ) могут находиться в любых состояниях, что отмечено знаком Х в табл.12.4.

Таблица 12.4. Таблица истинности для D ‑триггера с дополнительными входами

Если оба асинхронных входа приведены в неактивное состояние (S=1 и R=1 ), D ‑триггер можно установить в состояние 1 или 0 , используя D и С входы. Две последние строки табл.12.4 описывают передачу информационного сигнала с D входа триггера на его Q ‑выход с использованием тактового импульса. Поскольку эта операция осуществляется одновременно с приходом тактового импульса, она называется синхронной операцией . В данном триггере для передачи сигнала с D ‑входа на выход Q используется положительный перепад напряжений (от низкого уровня к высокому) на фронте тактового импульса. Этот факт показан в табл.12.4 знаком.

Т ‑триггер

Триггер типа Т называется триггером со счётным входом. Он изменяет своё состояние на противоположное каждый раз, когда на его вход приходит очередной сигнал. Обозначение триггера произошло от первой буквы английского слова toggle – защёлка.

Условное графическое обозначение Т

-триггера показано на рис. 12.14. Т

‑триггер имеет один вход Т

и два выхода Q

и ![]() . T

- счётный вход триггера.

. T

- счётный вход триггера.

![]()

Рис.12.14. Условное графическое обозначение T ‑триггера

Принцип работы триггера иллюстрирует его таблица истинности (табл.12.5).

Состояние его выхода меняется на противоположное при поступлении на вход счётного сигнала Т=1 и сохраняется неизменным при Т=0 . В соответствии с табл.12.5 характеристическое уравнение Т ‑триггера имеет вид:

![]()

Согласно этому уравнению Т

‑триггер сохраняет неизменное состояние при Т=0

, когда Q n+1=Q n

и при Т=1

, когда Q n+1=![]() .

.

Т ‑триггер может быть реализован введением в RS ‑ и D ‑триггеры обратных связей (рис.12.15).

Рис.12.15. Схемы T ‑триггера

Временная диаграмма сигналов Т ‑триггера показана на рис.12.16.

Рис.12.16. Временные диаграммы Т ‑триггера

Из рис.12.16 видно, что Т ‑триггер осуществляет деление частоты тактовой последовательности в 2 раза и переключение триггера происходит отрицательным фронтом счётного сигнала.

Рассмотрим граф переходов Т-триггера (рис.12.17)

Рис.12.17. Граф переходов Т ‑триггера

В кружках указаны значения выходного сигнала Q . Триггер, синхронизируемый фронтом, имеет по два различных состояния, значения которых приведены в знаменателях дроби. Стрелками показаны переходы триггера из одного состояния в другое при поступлении соответствующих комбинаций входных сигналов. Изменение значения Q происходит при поступлении перепада Т=0 1 . Граф переходов имеет промежуточные состояния 10 и 01 , в которые Т ‑триггер переводится перед переключением.

JK ‑триггер

JK ‑триггер наиболее широко используемый универсальный триггер, обладающий характеристиками всех других типов триггеров. JK ‑триггер в отличии от RS ‑триггера не имеет запрещенных комбинаций входных сигналов, которые следует исключать при работе цифровых систем.

На рис.12.18 показано условное графическое обозначение JK ‑триггера.

Рис.12.18. Условное графическое обозначение JK ‑триггера

Рассмотрим табл.12.6, иллюстрирующую принципы работы JK ‑триггера.

Таблица 12.6. Таблица истинности для JK ‑триггера

Из табл.12.6 видно, что когда на оба входа J и K подается уровень логического 0 , триггер блокируется, и состояния его выходов не изменяются. В этом случае триггер находится в режиме хранения.

Строки 2 и 3 табл.12.6 описывают режимы, соответствующие установке триггера в состояние 0 и 1 . Строка 4 соответствует переключательному режиму работы JK ‑триггера. Если на обоих входах J и K установлен уровень логической 1 , то следующие друг за другом тактовые импульсы будут вызывать перебросы уровней сигналов на выходах триггера от 1 к 0 , от 0 к 1 и т.д. Такая работа триггера напоминает последовательно производимые переключения тумблера, откуда и происходит название режима.

Характеристическое уравнение JK ‑триггера имеет вид:

![]()

JK ‑триггер может быть реализован с использованием двух элементов И и RS ‑триггера (рис.12.19).

Рис.12.19. Реализация JK ‑триггера

Граф переходов JK ‑триггера, синхронизируемого отрицательным фронтом синхросигнала показан на рис.12.20. В кружках указаны значения выходного сигнала Q , в знаменателях дробей показаны промежуточные состояния триггера перед переключением.

Рис.12.20. Граф переходов JK ‑триггера,

Синхронизируемого отрицательным фронтом ![]() синхросигнала

синхросигнала

JK ‑триггер может иметь два дополнительных входа (асинхронных): предварительной установки S и очистки R (рис.12.21).

Рис.12.21. Условное графическое обозначение JK-триггера с дополнительными входами

Асинхронные входы (S и R ) в активных состояниях блокируют действия синхронных входов. Активным состояниям асинхронных входов соответствуют три первых строки табл.12.7. В этих режимах синхронные входы блокированны и их состояния не влияют на состояние выходов триггера, поэтому для входов J , K и C в этих строках поставлен знак Х (любое состояние). Одновременная подача на оба асинхронных входа активного уровня сигнала (логического 0 ) соответствует запрещенному состоянию. При блокировании обоих асинхронных входов (S и R ) уровнем логической 1 ,работу триггера контролируют синхронные входы. Это показано в четырех нижних строках табл.12.7.

Таблица 12.7. Таблица истинности для JK ‑триггера с дополнительными входами

JK ‑триггеры широко применяются во многих цифровых схемах, в частности они используются для построения счетчиков. Схема фиксатораФиксатором можно назвать любое цифровое запоминающее устройство. Примером такого устройства является D ‑триггер. В микросхемном исполнении разработано большое число фиксаторов. Рассмотрим одну из таких схем: 4 ‑разрядный прозрачный фиксатор типа К155ТМ7 (зарубежный аналог — схема 7475), относящийся к классу ТТЛ - схем. Устройство состоит из четырех D ‑триггеров, объединенных в одной ИС. Условное графическое обозначение фиксатора показано на рис.12.22.

Рис.12.22. Условное графическое обозначение фиксатора

Информационный вход D0

, а также выходы Q0

и ![]() относятся к первому D

‑триггеру. Разрешающий вход Е0-1

аналогичен синхронизирующему входу D

‑триггера и используется для управления сразу двумя триггерами D0

и D1

внутри ИС. Анализ табл.12.8 показывает, что если на разрешающем входе действует уровень логической 1

, данные сразу не передаются (без ожидания тактового импульса) с соответствующих D

-входов на соответствующие выходы Q

и

относятся к первому D

‑триггеру. Разрешающий вход Е0-1

аналогичен синхронизирующему входу D

‑триггера и используется для управления сразу двумя триггерами D0

и D1

внутри ИС. Анализ табл.12.8 показывает, что если на разрешающем входе действует уровень логической 1

, данные сразу не передаются (без ожидания тактового импульса) с соответствующих D

-входов на соответствующие выходы Q

и ![]() . В режиме пересылки данных сигналы на Q

‑выходах фиксатора просто повторяют сигналы на соответствующих D

‑входах.

. В режиме пересылки данных сигналы на Q

‑выходах фиксатора просто повторяют сигналы на соответствующих D

‑входах.

При установке на разрешающем входе уровня логического 0 , соответствующие D ‑триггеры переводятся в режим фиксации данных. Информационные сигналы, которые действовали на выходах Q в момент перехода фиксатора в этот режим, сохраняются даже при изменении сигналов на входах D , т.е. данные оказываются «запертыми».

Таблица 12.8. Таблица истинности для фиксатора

Данную схему называют прозрачным фиксатором , поскольку при наличии высокого уровня сигнала на входе Е выходные сигналы точно отслеживают информационные сигналы на D ‑входах («насквозь просматривают»). Вход Е2-3 контролирует работу триггеров D2 и D3 .

Двухступенчатые триггеры

Для надёжной и чёткой работы триггерных ячеек в многоразрядных устройствах (регистрах, счётчиках) используются двухступенчатые триггеры, называемые MS ‑триггерами (master /slave — ведущий/ведомый или «мастер»/ «помощник»). Схема такого триггера, состоящего из двух синхронных RS ‑триггеров, показана на рис.12.23.

Входы с обоих триггеров ТМ

(мастера) и ТП

(помощника) соединены между собой через инвертор. На рис.12.24 показана диаграмма, из которой видно, что составным триггером ТМ

‑ТП

управляет полный (с фронтом и срезом) тактовый импульс C

. Входная комбинация будет записана в ТМ

в момент прихода положительного перепада тактового импульса С

. В этот момент в ТП

информация попасть не может. Когда придёт отрицательный перепад входного импульса С

, на выходе инвертора он появится как положительный. Положительный перепад импульса ![]() перепишет данные от выходов

перепишет данные от выходов ![]() ’ и

’ и ![]() ’ в ТП

.

’ в ТП

.

Рис.12.23. Схема двухступенчатого RS ‑триггера

Принцип работы двухступенчатого RS ‑триггера иллюстрирует табл.12.9.

Таблица 12.9. Таблица истинности для двухступенчатого RS ‑триггера

Условное графическое обозначение двухступенчатого RS ‑триггера показано на рис.12.25.

Рис.12.25. Условное графическое обозначение двухступенчатого RS ‑триггера

Двухфазный способ управления полным тактовым импульсом С применяется и для двухступенчатых JK ‑триггеров (рис.12.26). Этот триггер, как и простой JK ‑триггер, имеет обратные связи с выходов на входы, исключающие неопределённое логическое состояние. На рис.12.27 показана временная диаграмма переключающего импульса, на которой отмечены этапы работы составного триггера. В момент t1 ТП изолирован от ТМ ; в момент t2 разрешается приём данных входами ТМ . С приходом отрицательного перепада импульса в момент t3 запрещается приём данных входами ТМ , а в момент t4 заканчивается перенос данных из ТМ в ТП .

Рис.12.26. Схема двухступенчатого JK ‑триггера

Рис.12.27. Временная диаграмма управления двухступенчатым JK ‑триггером

Привлекательное свойство двухступенчатого триггера состоит в том, что входы приёма данных за период тактового импульса, т.е. во время загрузки 1 бита информации, не имеют сквозной связи с выходными цепями. Изоляция входов от выходов обеспечивает устойчивое переключение триггера, если частота тактовых импульсов нестабильна.

Похожие рефераты:

Техническая диагностика средств вычислительной техники

Устройство управления синхронного цифрового автомата

Классификация триггерных устройств. Требования и параметры, характеризующие триггерные устройства

Синтез суммирующего асинхронного счетчика

Автоматизация измерений, контроля и испытаний

Электротехника и основы электроники

Методы позиционирования и сжатия звука